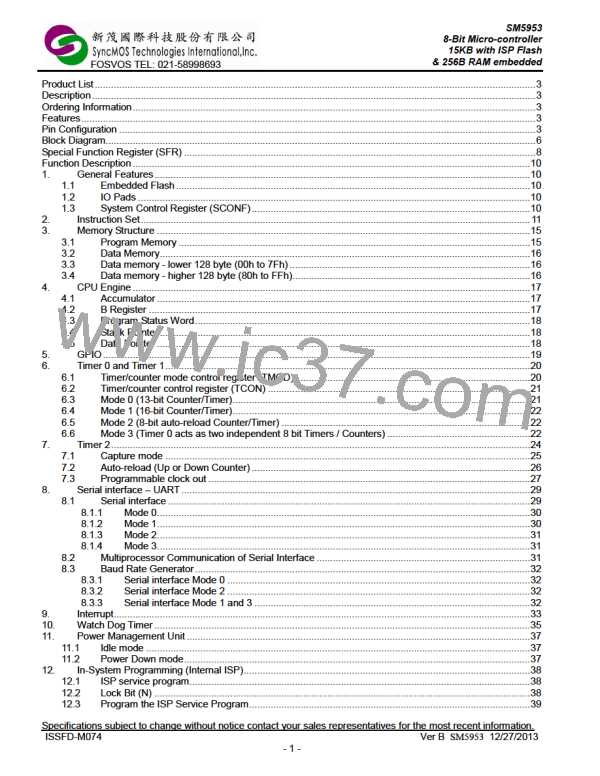

SM5953

8-Bit Micro-controller

15KB with ISP Flash

& 256B RAM embedded

7. Timer 2

Timer2 is a 16-bit timer/counter which can operate as either an event timer or an event counter as selected by

C/T2in the special function register T2CON.

Mnemonic

Description

Dir.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

RST

Serial interface 0 and 1

Timer 2 , low

byte

Timer 2 , high

byte

TL2

TH2

CCh

CDh

TL2[7:0]

00h

00h

TH2[7:0]

Reload and

RCAP2L

RCAP2H

capture data low CAh

byte

Reload and

RCAP2L[7:0]

00h

00h

capture data

high byte

CBh

RCAP2H[7:0]

T2MOD

T2CON

Timer 2 mode

C9h

C8h

-

-

-

-

-

-

T2OE DCEN

CP/

x0h

00h

Timer 2 control

register

EXEN

2

TF2

EXF2

RCLK

TCLK

TR2

C/ T2

RL2

Mnemonic: T2MOD

Address: 98h

7

-

6

-

5

-

4

-

3

-

2

-

1

0

Reset

00H

T2OE DCEN

T2OE: Timer 2 Output Enable bit. It enables Timer2 overflow rate to toggle P1.0.

DCEN: Down Count Enable bit. When set, this allows Timer2 to be configured as an up/down

Counter.

Mnemonic: T2CON

Address: 98h

7

6

5

4

3

2

1

0

Reset

CP/

TF2

EXF2

RCLK

TCLK

EXEN2

TR2

00H

C/ T2

RL2

TF2: Timer 2 overflow flag is set by a Timer 2 overflow and must be cleared by software. TF2

will not be set when either RCLK = 1 or TCLK = 1.

EXF2: Timer 2 external flag is set when either a capture or reload is caused by a negative

transition on T2EX and EXEN2 = 1. When Timer 2 interrupt is enabled, EXF2 = 1 will

cause the CPU to vector to the Timer 2 interrupt routine. EXF2 must be cleared by

software. EXF2 does not cause an interrupt in up/down counter mode (DCEN = 1).

RCLK: Receive clock enable. When set, causes the serial port to use Timer 2 overflow pluses

for its receive clock in serial port Modes 1 and 3. RCLK = 0 causes Timer 1 overflows to

be used for the receive clock.

TCLK: Transmit clock enable. When set, causes the serial port to use Timer 2 overflow pulses

for it’s transmit clock in serial port Modes 1 and 3. TCLK = 0 causes Timer 1 overflows to

be used for the transmit clock.

Specifications subject to change without notice contact your sales representatives for the most recent information.

ISSFD-M074 Ver B SM5953 12/27/2013

- 24 -

SYNCMOS [ SYNCMOS TECHNOLOGIES,INC ]

SYNCMOS [ SYNCMOS TECHNOLOGIES,INC ]