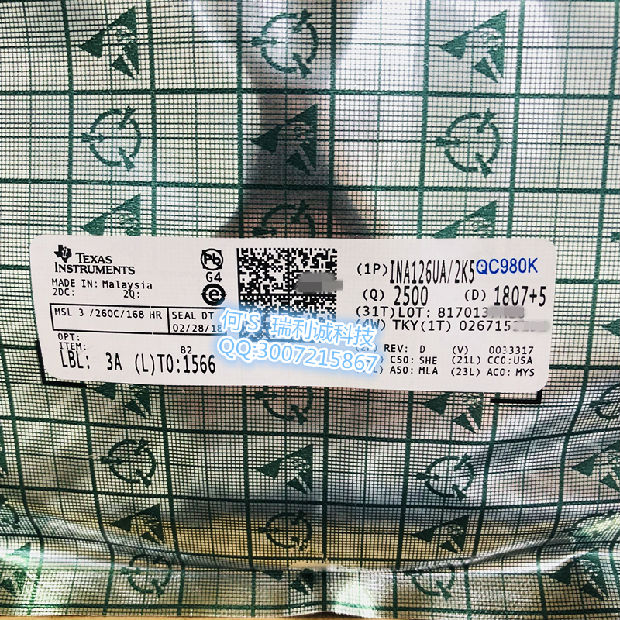

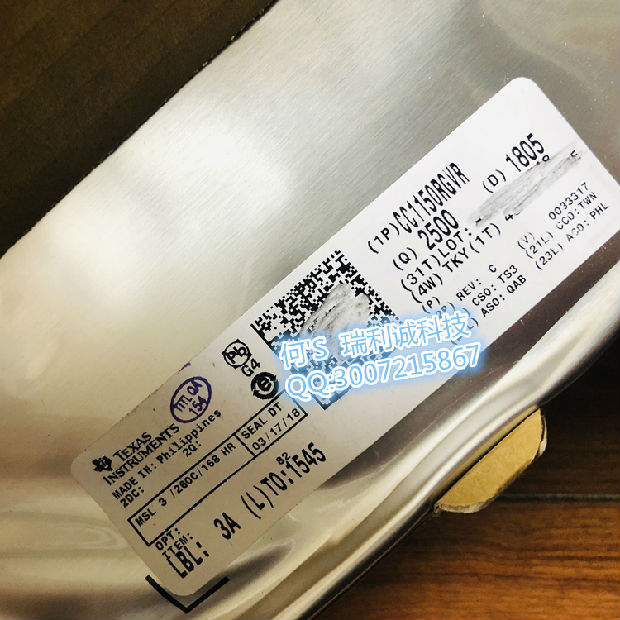

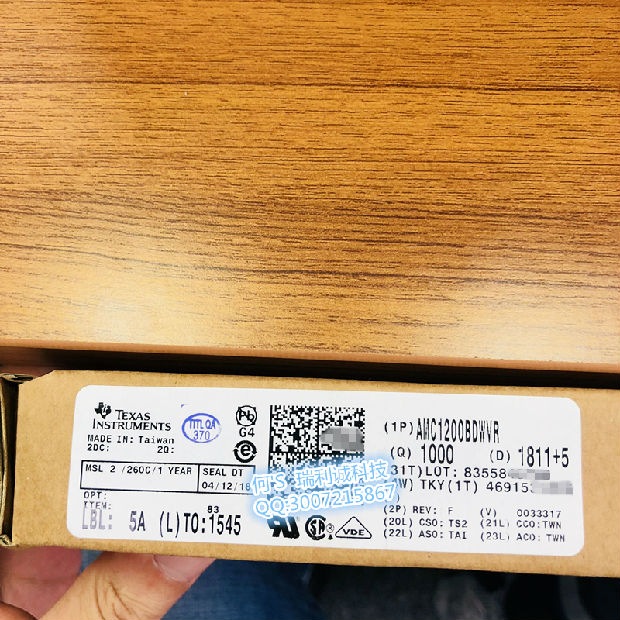

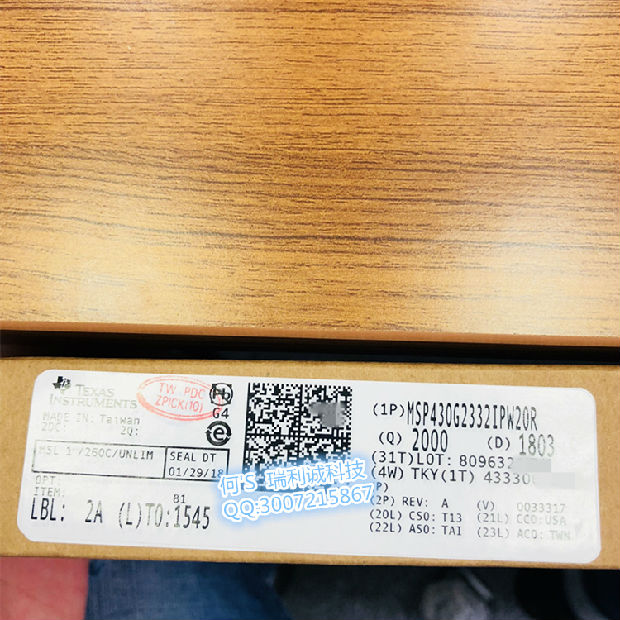

CDCLVC1104PWR

日期:2018-5-26

品牌;TI

封装:SSOP8

包装;2500

数量;250000

年份:1810+

产地:马来西亚

瑞利诚科技(深圳)有限公司

联系人:Eason

电话:13312991513

QQ:1134043964

邮箱:13312991513@163.com

备选器件推荐

CDCV304 - 器件与被比较器件具有相似功能,但并不功能等效。 1:4 LVCMOS Buffer up to 200MHz

LMK00105 - 器件与被比较器件具有相同的功能,但并不是引脚对引脚等效,也有可能参数不相同。 Ultra low additive jitter,1:5 LVCMOS Buffers/Level translator

描述

CDCLVC11xx是一个模块化、高性能、低倾斜、通用时钟缓冲家庭,来自德州仪器。

整个家庭的设计思路是模块化的。它的目的是使ti系列的LVCMOS时钟发生器。

有七种不同的扇出变奏曲,1:2到1:12。所有的设备都是相互兼容的,便于操作。

所有家庭成员都具有相同的高表现特征,如低加性抖动、低倾斜和广泛的工作温度范围。

CDCLVC11xx支持异步输出启用控制(1G),当1G处于低位时,将输出转换为低状态。

CDCLVC11xx家族以2.5-V和。

3.3-V环境,并具有从-40 C到85 C的操作特征。

特性

高性能1:2,1:3,1:4,1:6,1:8,1:10,1:12 LVCMOS时钟缓冲家庭。

非常低的Pin-to-Pin偏差< 50 ps。

非常低的附加抖动< 100 fs。

电源电压:3.3 V或2.5 V。

fmax = 250 MHz,为3.3 V。

fmax = 180 MHz, 2.5 v。

操作温度范围:-40 C至85 C。

8-,14-,16-,20-,24-Pin TSSOP包(所有与pin兼容)

所有商标都是其各自所有者的财产。

CDCLVC11xx 3.3-V和2.5-V LVCMOS高性能时钟缓冲家庭。

1

1功能

1•高性能1:2,1:3,1:4,1:6,1:8,1:10,

1:12 LVCMOS时钟缓冲家庭。

•非常低的Pin-to-Pin偏差< 50 ps。

非常低的附加抖动< 100 fs。

•电源电压:3.3 V或2.5 V。

•fmax = 250 MHz,为3.3 V。

fmax = 180 MHz, 2.5 V。

•操作温度范围:-40°C到85°C

•可在8- 14- 16- 20- 24-Pin TSSOP中使用。

包(所有Pin-Compatible)

2应用程序

通用通信、工业、和

使用者应用程序

3描述

CDCLVC11xx是一个模块化的、高性能的,

低倾斜,通用时钟缓冲家庭。

德州仪器。

整个家庭都是用模块化设计的。

方法记住。它的目的是要把TI的。

一系列LVCMOS时钟发生器。

7个不同的扇出变化,1:2到1:12,是。

可用。所有的设备都是与pin兼容的。

为便于操作。

所有家庭成员的表现都是一样的。

低附加抖动,低倾斜,

和广泛的工作温度范围。

CDCLVC11xx支持异步输出。

使控制(1G)将输出转换为a。

低状态时1G低。

CDCLVC11xx家族以2.5-V和。

3.3-V的环境和特征。

操作从-40°C到85°C。

8.1概述

CDCLVC11xx系列设备是一种低抖动、低倾斜的LVCMOS输出缓冲液。最佳的信号

完整性,重要的是匹配CDCLVC11xx的输出驱动程序的特性阻抗与之匹配。

输电线路。图5和图6显示了VDD = 3.3 V和。

VDD = 2.5 V。TI建议将串联电阻器靠近驱动器,以减少信号反射。

8.3特性描述

通过驱动异步输出使pin (1G)低,可以禁用CDCLVC11xx的输出。

未使用的输出可以保持浮动,以减少整个系统组件的成本。所有的供应和地脚必须是。

分别与VDD和GND连接。

8.4设备功能模式

CDCLVC11xx由2.5 V和3.3 V之间的供应操作。

9应用和实现

请注意

以下应用程序部分中的信息不是TI组件的一部分。

规格,而TI不保证其准确性或完整性。“透明国际”的客户

负责为其目的确定组件的适用性。客户应该

验证并测试其设计实现以确认系统功能。

9.1应用程序信息

CDCLVC11xx家族是一种低加性抖动的LVCMOS缓冲液,可以在250兆赫的范围内运行。

180 MHz在VDD = 2.5 V。低输出倾斜,以及异步输出的能力是有特色的。

在应用程序中同时启用或禁用缓冲时钟输出。

9.2.1设计要求

图10中显示的CDCLVC11xx配置为从本地LVCMOS振荡器中输出100 mhz的信号。

CPU被配置为通过1G控制输出状态。

配置示例在一个backplane应用程序中驱动三个LVCMOS接收器。

属性:

•CPU时钟可以接受一个完整的swing dc -耦合LVCMOS信号。一个串联电阻器被放置在靠近的地方。

CDCLVC11xx与跟踪的特性阻抗紧密匹配,以最小化反射。

•FPGA时钟同样是dc -耦合的,在CDCLVC11xx附近安装了一个适当的串联电阻。

•本例中的PLL可以接受较低的振幅信号,因此使用了Thevenin的等效终止。

PLL接收机具有内部偏置的特点,所以在共模电压时可以使用交流耦合。

不匹配。

9.2.2详细设计过程

参考图5和电气特性表,确定所需的串联电阻。

为了匹配CDCLVC11xx的输出阻抗与该特性阻抗的匹配。

输电线路。

10供电的建议

高性能的时钟缓冲器对电源的噪声敏感,这将极大地增加电力供应。

缓冲的附加抖动。因此,减少系统电源的噪声是至关重要的,特别是在系统供电时。

抖动和相位噪声是应用的关键。

过滤器电容器用于消除来自电源的低频噪声,在这里旁路。

电容器为高频噪声提供非常低的阻抗通道,并保护供电系统。

对引起的波动。这些旁路电容器还可以根据需要提供瞬时电流。

该装置应具有低等效串联电阻(ESR)。为了正确使用旁路电容,他们。

必须非常靠近电源端子,并铺设短环以减少电感。“透明国际”

建议增加许多高频(例如,0.1 F)旁路电容器,因为有供应。

终端在包。TI建议,但不需要,在板的力量之间插入一个铁素体珠。

电源和芯片电源,隔离时钟缓冲器产生的高频开关噪声;

这些珠子可以防止开关噪音泄露到板上。选择一个是必要的。

适当的铁氧体珠,具有非常低的直流电阻,可以在板的供应和之间提供足够的隔离。

芯片的供应,以及在供应终端保持电压大于最小电压。

正确操作所必需的。