DS90UB940TNKDRQ1

日期:2018-5-17

品牌:TI

型号:DS90UB940TNKDRQ1

封装:QFN64

包装:2000

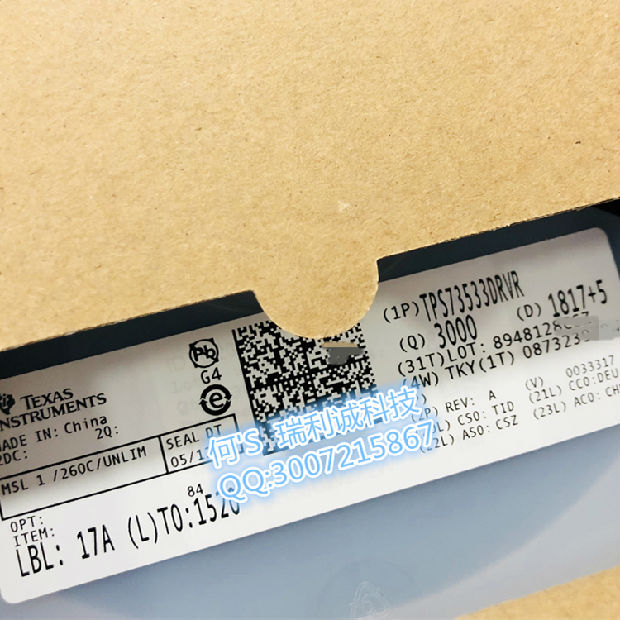

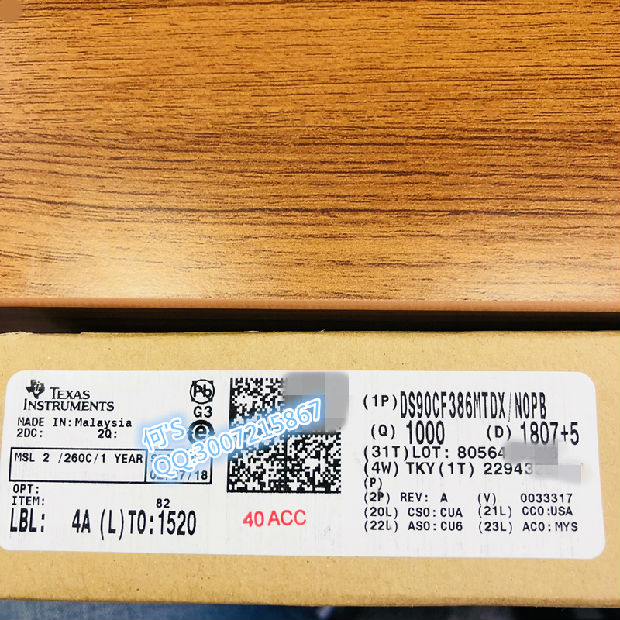

年份:1807+5

产地:马来西亚

数量:80000

瑞利诚科技(深圳)有限公司

联系人:Eason

电话:13312991513

QQ:1134043964

邮箱:13312991513@163.com

描述

DS90UB940-Q1 是一款 FPD-Link III 解串器,与 DS90UB949/947/929-Q1 串行器配合使用时可将单通道或双通道 FPD-Link III 流转换成 MIPI CSI-2 接口格式。该解串器能够在经济高效的 50Ω 单端同轴或 100Ω 差分屏蔽双绞线 (STP) 电缆上运行。它能够从单通道或双通道 FPD-Link III 串行流中恢复数据,然后将其转换为摄像机串行接口 (CSI-2) 格式,最高可支持 WUXGA 和 1080p60 视频分辨率(24 位色深)。

DS90CF366接收机将四个LVDS(低电压差分信令)数据流转换回并行28位的LVCMOS数据。同样可用的是将三个LVDS数据流转换为21位LVCMOS数据的DS90CF366接收机。两个接收器的输出在下降沿上闪动。上升沿或下降沿选通发送器将与没有任何转换逻辑的下降沿选通接收机互操作。

接收器LVDS时钟工作在从20 MHz到85 MHz的速率。设备相位锁定到输入LVDS时钟,在LVDS数据线上采样串行比特流,并将它们转换成并行输出数据。在85 MHz的输入时钟速率下,每个LVDS输入线以595 Mbps的比特率运行,导致DS90CF366的最大吞吐量为2.38 Gbps,而D90CF366的最大Gbps为1.785 Gbps。

这些串行链路设备的使用对于解决在宽、高速并行LVCMOS接口上传输数据相关的EMI和电缆尺寸问题是理想的。这两种设备都提供在TSSOP封装。DS90CF366还提供了一个64引脚,0.8毫米,细间距球栅阵列(NFBGA)封装,提供了44%的PCB足迹减少相比,56引脚TSSOP封装。

特技

20 MHz至85 MHz移位时钟支持

RX功耗<142毫瓦(典型)

85兆赫灰度级

RX掉电模式<1.44毫瓦(最大值)

ESD额定值>7 kV(HBm)>700 V(EIAJ)

支持VGA、SVGA、XGA和单像素

SXGA

PLL不需要外部组件

与TIA/EIA-64 4 LVDS标准兼容

低剖面56针或48针TSSOP封装

DS90CF366也可在64针,0.8毫米,

细间距球栅阵列(NFBGA)封装

FPD-Link III 接口支持通过同一条差分链路进行视频和音频数据传输以及全双工控制(包括 I2C 和 SPI 通信)。通过两个差分对实现视频数据和控制的整合可减小互连线尺寸和重量,并简化了系统设计。通过使用低压差分信令、数据换序和随机生成最大限度地减少了电磁干扰 (EMI)。在向后兼容模式下,该器件在单一差分链路上最高可支持 WXGA 和 720p 分辨率(24 位色深)。

DS90CF3x6 3.3-V LVDS接收机24位或18位平板显示器(FPD)链路,85兆赫

1大特征

1·20 MHz至85 MHz移位时钟支持

·Rx功耗<142毫瓦(典型)

85兆赫灰度级

RX掉电模式<1.44毫瓦(最大值)

·ESD额定值>7千伏(HBM)>700 V(EIAJ)

支持VGA、SVGA、XGA和单像素

SGA

PLL不需要外部组件

兼容TIA/EIA-64 4LVDS标准

低轮廓56针或48针TSSOP封装

DS90CF366也可在64针,0.8毫米

2应用

视频显示器

打印机和成像

数字视频传输

机器视觉

RGB桥开放LDI

描述

DS90CF366接收机转换四LVDS(Low)

电压差分信号)数据流回到

并行28位的LVCMOS数据。也可用的是

转换三个LVDS数据的DS90CF366接收机

流回到平行21位的LVCMOS数据。两个接收器的输出都在下降。边缘。上升沿或下降沿选通发射机将与下降沿选通接收机互操作

没有任何翻译逻辑。

接收器LVDS时钟以速率从

20兆赫至85兆赫。设备相位锁定到

输入LVDS时钟,采样串行位流

LVDS数据线,并将它们转换成并行

输出数据。在85兆赫的输入时钟速率下,

每个LVDS输入行以一个比特率运行。

595 Mbps,导致最大吞吐量

用于DS90CF38 6和1.785 Gbps的2.38 Gbps

DS90CF366。

这些串行链路设备的使用是理想的。

解决EMI和电缆尺寸问题

通过宽、高速并行传输数据

LVCMOS接口。两种设备都提供在

TSSOP封装。DS90CF86也提供在

64针,0.8毫米,细间距球栅阵列(NFBGA)

PCB提供44%的包装

占地面积相比,56引脚TSSOP封装。

设备信息(1)

零件号封装体尺寸(NOM)

DS90CF366 TSSOP(48)12.50 mm×6.10 mm

DS90CF86

TSSOP(56)14毫米×6.10毫米

NFBGA(64)8毫米×8毫米

(1)对于所有可用的包,请参见可订购附件。

数据表的末尾。

细间距球栅阵列(NFBGA)封装该器件将自动检测 FPD-Link III 通道并提供一种时钟对齐和偏移补偿功能,无需任何特殊的训练模式。这可在互连线路(例如,印刷电路板 (PCB) 布线)中出现不匹配问题、电缆线对长度存在差异以及连接器不平衡时确保相位偏移在容差范围内。

特性

支持高达 170MHz 的像素时钟频率,支持 WUXGA (1920x1200) 和 1080p60 分辨率(24 位色深)

具有偏移补偿能力的单通道或双通道 FPD-Link III 接口

MIPI D-PHY/CSI-2 发送器

支持 2 通道或 4 通道两种可选操作的 CSI-2 输出端口

每个 CSI-2 端口最多支持 4 个数据通道,每个通道最高 1.3Gbps

视频格式:RGB888/666/565、YUV422/420 和 RAW8/10/12

可编程虚拟通道标识符

速度高达 2.0Mbps 的通用输入输出 (GPIO)

具有自动温度和老化补偿功能,支持长达 15 米的电缆

速率高达 3.3Mbps 的串行外设接口 (SPI) 控制接口

具有 1Mbps 快速模式+ 的 I2C(主/从)

自适应接收均衡

支持多条 I2S(4 个数据)通道

向后兼容 DS90UB925/925AQ-Q1 和 DS90UB927Q-Q1 FPD-Link III 串行器

汽车应用级产品:符合 AEC-Q100 2 级要求

应用

汽车信息娱乐:

中央信息显示屏

后座娱乐系统

数字仪表板

高级驾驶员辅助系统 (ADAS) 摄像机系统

ds90ub940 Q1 1080p的三至FPD链路的CSI 2解串器

1特性

••支持高达的像素时钟频率170MHz,支持wuxga

(1080p60分辨率1920x1200)和(24位色深)

•三具有偏移补偿能力的单通道或双通道FPD链路接口

•MIPI D - PHY / 2发送器CSI

支持2–4通道两种可选操作的通道或CSI 2输出端口

每个CSI 2–4个数据通道端口最多支持,每个

通道最高1.3gbps

–视频格式:rgb888 666 565、yuv422 420和/ / /

raw8 / 10 / 12

–可编程虚拟通道标识符

•速度高达2.0mbps的通用输入输出(GPIO)

•具有自动温度和老化补偿功能,支持长达15米的电缆

•速率高达3.3mbps的串行外设接口控制接口(SPI)

•具有1Mbps快速模式+”I2C(主/从)

•自适应接收均衡

•(4个数据通道支持多条I2S)

•向后兼容ds90ub925 / 925aq Q1和

ds90ub927q Q1三串行器FPD链路

汽车应用级产品AEC - Q100:•2级要求符合

引脚功能(continued)

松树

I / O型的描述

名称编号

PDB 48 I,LVCMOS

配置W /弱松

内部PD

电源输入PIN唐模式

PDB=1,设备是启用(正常运行)

PDB = 0,设备是供电下。

when the device is in the power down in the state,LVCMOS输出是三态;

the PLL是关闭和IDD是最小的。

注:要求最小斜坡时间PDB松200us

bisten 5 I,LVCMOS

配置W /弱松

内部PD

BIST的松树

0:BIST模式是残疾人。

1:BIST模式是启用的。

See内置自我测试(BIST)更多信息

bistc(人居署_ in)

4我的LVCMOS

配置W /弱松

内部PD内建自测试点选择。

ds90ub940 Q1

Copyright2016,德克萨斯仪器公司

引脚功能(续)

I / O型,描述

name的值

vddio 3功率低I / O电源1.8V(±5%)或3.3V(±10%)。requires 10μF;,1μF;0.1μF;和电容的gnd 0.01μF;

在1.2V电源(±5%)的用品。requires 10μF;,1μF;0.1μF;,和0.01μF

第decoupling电容器的连接方法是芯片上的调节。每一requires 0.1μF;

decoupling电容的gnd VSS地面磷酸二铵DAP是大的金属接触的底端,位于在中心wqfn

包装。连接到地平面(gnd)和至少32个通孔。

O,监测点的equalized CML差分信号。布局的建议:

1)浇在0.1μF;系列电容器是cmloutp和cmloutn

2)现浇25欧姆接到100欧姆终端之间0.1μF;从cmloutp和消失

3)的测试点的地方从0.1μF;电容

在下面的DEFINE定义的功能性的I / O细胞for each

•P =电源 •G =地面

•在慢性髓细胞性白血病CML接口.

•dphy = dphy MIPI接口

•模拟=模拟接口

•LVCMOS = LVCMOS引脚;引用到vddio IO电源

•I / O =输入/输出

•PD,PU =内部拉式拉升(全皮带的地面,有弱的内部拉UPS或拉起伏。如果皮带的默认值是需要的是

改变了当时的外部电阻应该可以使用。多功能引脚

规格

7.1绝对最大额定值

超过运行的自由空气温度范围(除非另有说明)(1)

参数最小最大单位

VDD33电源电压- 0.3伏4伏

VDD12电源电压- 0.3伏1.8伏

VDDIO电源电压- 0.3伏4伏

LVCMOS I/O电压- 0.3 VDIO+

FPD链路III输入电压- 0.3 2.75 V

TJ结温度150°C

TSTG储存温度范围:65℃150℃

(1)AEC Q100-2000表示HBM应力应符合ANSI/ESDA/JEDEC JS-1001规范。

7.2 ESD等级JEDEC

V(静电放电)静电放电

人体模型(HBM),每个AEC Q100-2000(1)±8000

充电装置模型(CDM),每个AEC Q100-011±1250

7.3 ESD评级IEC和ISO

价值单位

V(静电放电)静电放电

RD=330Ω,CS=150 pF

IEC,仅供电接触放电

(Run0+,Run0-,Run1+,Run1-)

IEC,仅气隙放电

(Run0+,Run0-,Run1+,Run1-)

ISO10605接触放电(RUN0+,RUN0-,

ISO10605气隙放电(RI00+,RAN0-,

RD=2 KΩ,CS=150和330 pF

ISO10605接触放电(RUN0+,RUN0-,

ISO10605气隙放电(RI00+,RAN0-,

推荐的7.4种操作条件

电源电压(VDD33)3 3.3 V 3.6 V

电源电压(VDD18)1.71 1.8 V 1.89 V

电源电压(VDD12)1.14 1.2 V 1.26 V

运行自由空气温度(Ta):40℃25°C°C

像素时钟频率(单链路)25 MHz 96

像素时钟频率(双链路)50 170 MHz

电源噪声——VDD33(DC-50MHz)100 MVP P

电源噪声——VDD18(DC-50MHz)50 MVP P