DAC8565IAPWR

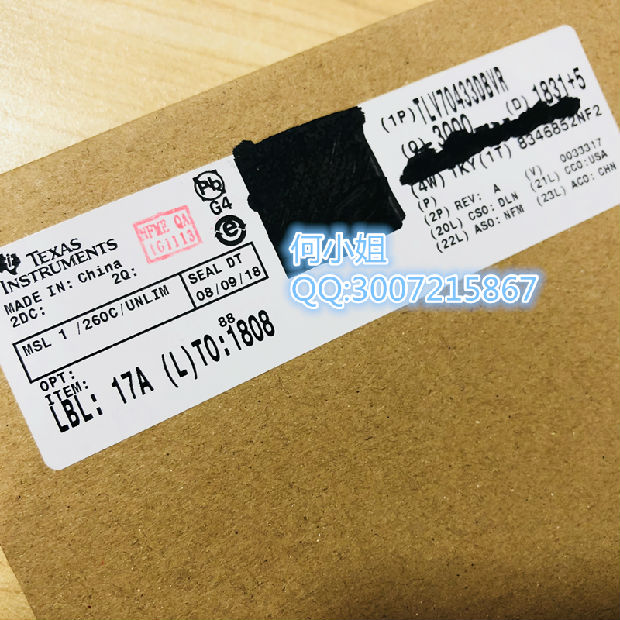

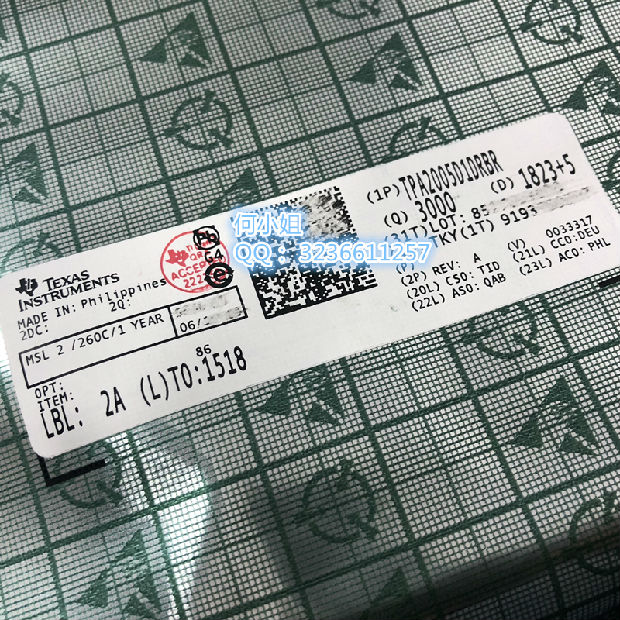

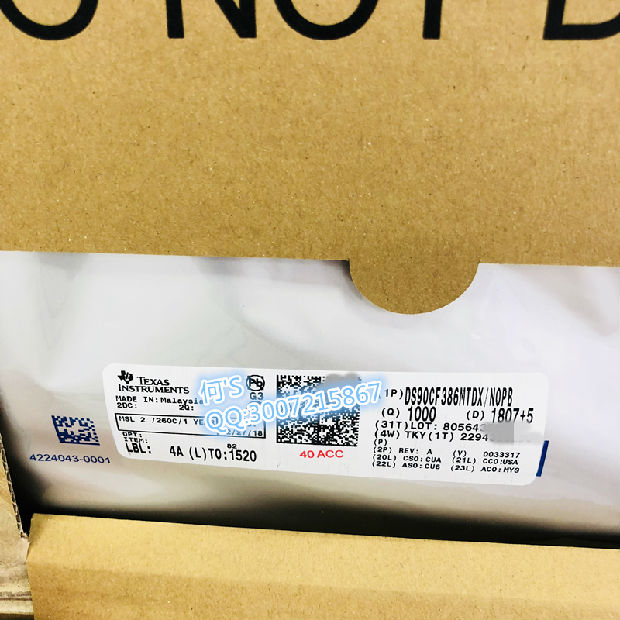

日期:2018-8-3

品牌:TI

型号:DAC8565IDPWR

封装:TSSOP16

包装:2000

年份:1825+

产地:MY 马来西亚

数量:80000

瑞利诚科技(深圳)有限公司

联系人:何小姐

电话:83253832

qq:3007215867

描述

DAC8565是一种低功率、电压输出、四通道、16位数字-模拟转换器(DAC)。设备包括一个2.5 v,2 ppm /°C内部参考(默认启用),给予全面的输出电压2.5 v。内部引用的初始精度为0.004%,可在VREFH/VREFOUT引脚处获取最高20mA的数据。

该设备是单调的,提供非常好的线性,并最小化不希望的代码到代码的瞬变电压(glitch)。DAC8565采用一种通用的三线串行接口,其时钟频率可达50MHZ。它是兼容标准SPI™,QSPI™,导电带™,和数字信号处理器(DSP)的接口。

DAC8565集成了一个电源复位电路,确保DAC的输出功率在零级或中级都有提升,直到一个有效的代码被写入设备。设备包含一个省电功能,访问串行接口,减少设备的电流消耗1.3μa 5 v。低功耗,内部引用,和小的碳足迹,使这个设备理想的便携式,电池操作的设备。在3 v 2.9 mw电力消耗,减少到1.5μw处于省电模式。

DAC8565与DAC7564和DAC8164功能兼容,与DAC7565、DAC8165和DAC8564功能兼容。所有这些设备都可以在TSSOP-16包中使用。

特性

相对精度:4 lsb

nv-s故障能源:0.15

内部参考:

2.5V参考电压(默认启用)

0.004%的初始精度(typ)

2 ppm /°C温度漂移(typ)

5 ppm /°C温度漂移(max)

20 ma水槽/源能力

开机复位至零刻度或中刻度

异步清晰到零或中刻度

超低功耗操作:1mA, 5V

电源范围:+2.7V ~ +5.5V

16位单调温度范围

结算时间:10μs±0.003%全面范围(FSR)

低功耗串行接口与schmitt触发输入:高达50MHZ

片上输出缓冲放大器与轨道-轨操作

1.8V至5.5V的逻辑兼容性。

温度范围:-40°C + 105°C

应用程序

便携式仪器

闭环伺服控制

过程控制、制度

数据采集系统

可编程衰减

电脑外围设备

SPI, QSPI是摩托罗拉公司的商标。

微丝是国家半导体公司的商标。

所有其他商标均为其各自所有者的财产。

16位,四通道,超低故障,电压输出。

数模转换器为2.5 v,2 ppm /°C内部参考

检查样品:DAC8565

1功能描述

DAC8565是一款低功率,电压输出,

234•相对精度:4 lsb

四通道,16位数字-模拟转换器(DAC)。

•故障能源:0.15 nv-s设备包括一个2.5 v,2 ppm /°C的内部

•内部引用:引用(默认启用),给出一个完整的值

- 2.5V参考电压(默认启用)内部参考

初始精度为0.004%,是否可以提供?

- 0.004%的初始精度(typ)到20mA的VREFH/VREFOUT引脚。该设备是

- 2 ppm /°C温度漂移(typ)单调,提供了很好的线性,

- 5 ppm /°C温度漂移(max)最小化干扰code-to-code瞬态电压(故障)。

DAC8565采用通用的三线串行

- 20mA接收器/源能力接口,在时钟频率高达50MHZ

它加电复位为0比例或中级兼容标准SPI™,QSPI™,

•异步清楚0比例或中级导电带™,和数字信号处理器(DSP)接口。

·超低功耗操作:1mA, 5V

·广泛的电源范围:+2.7V到+5.5V。

DAC8565采用了电源复位电路

这就确保了DAC的输出功率在温度范围的16位单调或零刻度或中刻度,直到写入一个有效的代码

•解决时间:10μs全面设备±0.003%。

这个装置装有电源范围(FSR)特性,通过串行接口访问,即

•低功耗串行接口,减少设备的电流消耗1.3 Schmitt-Triggeredμa 5 v。

低功耗,内部输入:高达50MHZ

参考,和小的足迹使这个设备理想

•芯片输出缓冲放大器,用于便携式,电池操作的设备。电源轨到轨操作消费2.9 mw在3 v,1.5μw减少•1.8V至5.5V逻辑兼容关机模式。

•温度范围:-40°C + 105°C DAC8565 dropin和功能兼容的

具有DAC7564和DAC8164的功能与DAC7565、DAC8165和

•便携式仪表DAC8564

所有这些设备都可以在a中使用

TSSOP-16包

•闭环伺服控制

•过程控制、制度

•数据采集系统

•可编程衰减

•PC外围设备

超过自由空气温度范围(除非另有说明)。

DAC8565单位

AVDD到GND -0.3到+6 V。

数字输入电压为GND -0.3到+VDD + 0.3 V。

VOUT到GND -0.3到+VDD + 0.3 V

VREF到GND -0.3到+VDD + 0.3 V

操作温度范围-40 + 125°C

存储温度范围-65 + 150°C

结温度范围(TJ max)+ 150°C

功耗(TJ马克斯- TA)/θJA W

热阻抗,θJA + 118°C / W

热阻抗,θJC + 29°C / W

人体模型(HBM) 4000 V

防静电等级充电设备型号(CDM) 1500v

(1)超过绝对最大额定值的应力可能会对设备造成永久损坏。

暴露于绝对延长周期的最大条件可能影响设备的可靠性。

数字-模拟转换器(DAC)码装入DAC寄存器,确定为

在弦上的哪个节点电压被抽调到DAC8565结构由一个串DAC组成,通过关闭一个接在后面的输出缓冲放大器进入输出放大器。图92连接字符串到放大器的开关。它展示了DAC体系结构的框图。因为它是一串电阻。

DAC8565架构

DAC8565的输入编码可以是直接的

二进制或二进制的补码,所以是理想的输出。电压由公式1给出。

哪里的DIN =十进制的二进制代码等效

加载到DAC寄存器;它可以从0开始

到65535年。

X代表通道A、B、C或D。数据格式

数据格式可以是直接二进制或两种补。

表1说明了差异

在USB(无符号直二进制)和BTC之间

(二进制2的补码)数据格式。

DAC8565包含一个2.5V的内部引用

默认情况下是启用的。内部参考

外部可用的VREFH/VREFOUT引脚。

一个推荐最小100nF电容。

噪声滤波的参考输出和GND。

DAC8565的内部引用是双极的电晶体、精密隙电压图94显示了基本的带隙拓扑。

晶体管Q1和Q2是有偏差的。

Q1的电流密度两个基发射极电压的差值(VBE1 - VBE2)温度系数为正被强制通过电阻R1

这个电压是

增加了基极-发射极电压

第二季,温度系数为负。

产生的输出电压实际上是独立于温度。

短路电流受图94的限制。简化的带隙示意图设计到大约100 ma。

参考

启用/禁用内部引用,以启用内部引用,或者执行。

可以通过表3所示的串行命令来启用用于重置设备或编写DAC8565中的24位内部引用的电源循环。这些动作设置为默认,并以自动模式运行;但是,内部引用回到默认模式。在引用中可以禁用调试、评估默认模式、内部引用权限或使用外部引用

一个在任何需要24位写序列的串行命令中,当所有的DACs都关机时,自动关机模式(请参阅关机模式(请参阅串行接口部分)必须用于分区);内部引用增强了对内部引用的禁用,如表2所示。

当任何DAC启动时自动。当内部引用被禁用时,

DAC功能通常使用外部的DAC8565也提供了保留参考。

此时,无论如何,内部引用始终是内部引用

与VREFH/VREFOUT引脚断开(DAC(s)状态的3个状态(通电或通电)。保持输出)。

不要试图驱动VREFH/VREFOUT打开的内部引用,不管它是什么

在外部和内部同时在DAC(s)状态下,写入显示的24位串行命令。

DAC8565有一个3线串行接口(同步,到图36的典型特征部分,

SCLK和DIN)兼容SPI、QSPI和图57,以及图79(提供电流vs逻辑微丝接口标准,以及大多数dsp。输入电压)。参见串行写操作时序图

典型的写序列的例子。IOVDD和电压翻译

DAC8565输入移位寄存器24位宽,IOVDD引脚为数字输入结构提供电源,由8个控制位(DB23到DB16)和16个DAC8565组成。对于单供应操作,它可以数据位(DB15到DB0)。所有24位数据都与AVDD绑定。对于双电源操作,IOVDD在串口引脚的控制下装入DAC,提供了各种CMOS时钟输入SCLK的接口灵活性。

DB23 (MSB)是第一个作为逻辑族的位,应该连接到加载到DAC移位寄存器的逻辑,然后是系统的供应。模拟电路和内部其余的24位字模式,左对齐。DAC8565的这个逻辑使用AVDD作为供应配置,意味着前24位数据是电压。外部逻辑高输入转换为锁存到移位寄存器和任何进一步的按电平移位器锁定AVDD。

这些水平移位器使用的数据被忽略。DAC8565接收所有24位IOVDD电压作为参考,以转移数据的输入,并解码前8位,以确定对AVDD的逻辑高水平。确保IOVDD为DAC操作/控制模式。16位数据从2.7V运行到5.5V,而不考虑后面的AVDD, DAC对其进行解码以确定电压,保证与各种逻辑等效模拟输出的兼容性。数据格式是直系亲属。IOVDD虽然被指定为2.7V,但所有'0's对应于0V输出,且所有的操作都在1.8V以下,时序退化,而'1'对应于全尺寸输出(即VREF -)

温度性能。最低功率为1 LSB);有关更多细节,请参见数据格式部分。消费,逻辑VIH水平应该接近。

写入序列首先将可能的同步线引入IOVDD,逻辑VIL级别应该是

低。来自DIN线的数据被记录到尽可能接近GND电压的24位。

在SCLK的每个下降边缘上移位寄存器。串行

时钟频率可高达50MHZ,实现异步复位

DAC8565与高速dsp兼容。在DAC8565输出被异步地设置为串行时钟的第24个下降边缘,最后的数据零刻度电压或中刻度电压(取决于位被锁定到移位寄存器和移位RSTSEL)在RST引脚被带来寄存器锁之后。进一步的锁定不会改变低点。RST信号重置所有内部寄存器,并移位寄存器数据。一旦24位被锁定到“因此”,行为就像开机复位。移位寄存器,8个MSBs作为控制位,RST引脚必须在写入之前恢复到高,16个LSBs作为数据使用。在收到

序列的开始。如果RSTSEL引脚很高,RST第24个下降的时钟边缘,DAC8565解码低的信号,将所有输出重置为中等规模。如果执行RSTSEL引脚的8个控制位和16个数据位是低的,那么低的RST信号就会重新设置所需的函数,而不需要等待同步将所有输出提升到零级。RSTSEL应该设置在边缘。一个新的书写顺序从下一个秋天开始

升高。同步的边缘。同步的上升边缘

24位序列完成SPI接口的重置;

没有发生数据传输。在输入移位寄存器的第24下降沿之后

接收到SCLK,同步线可以保持低,DAC8565的输入移位寄存器(SR)为24或高。

无论哪种情况,最小延迟位都是宽的,如表5所示。它由八个时间从第24次下降到下一个控制位(DB23到DB16)和16个数据位(DB15)。

为了正确地到达DB0,必须满足落差同步边缘。