聊聊半导体产品的8大封装工艺

发布日期:2024-06-06

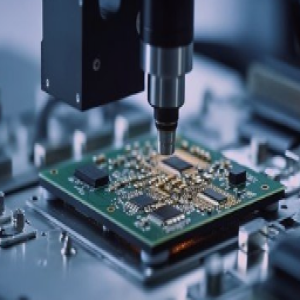

半导体产品的封装是芯片制造过程中的关键步骤之一,它不仅保护脆弱的集成电路免受物理损伤和环境影响,还负责电路与外部系统的电气连接。随着技术的发展,封装技术不断演进,以适应更小、更快、更复杂的芯片设计需求。以下是半导体产品中常见的八种封装工艺,每种工艺都有其独特的优势和应用场景。

1. 引线框架封装(Lead Frame Package)

引线框架封装是最传统的封装形式之一,广泛应用于消费电子、计算机和通信领域。它包括将芯片粘贴或焊接在金属引线框架上,通过细小的金属线(引线)连接芯片的接点与框架上的引脚,最后用塑料或环氧树脂封装。这种封装成本低、可靠性高,但尺寸较大,不适合高密度应用。

2. 球栅阵列封装(Ball Grid Array, BGA)

BGA封装通过在芯片底部排列一矩阵状的焊球来实现与主板的连接,大大提高了引脚密度,适用于高性能处理器、内存芯片等。它能提供更好的散热性能,减少信号路径长度,提高信号完整性,但对焊接工艺要求较高。

3. 芯片级封装(Chip Scale Package, CSP)

CSP封装的尺寸接近芯片尺寸,具有极高的封装密度,适用于便携式设备。它通过直接在芯片表面布设焊球或其他类型的接触点来实现,显著减小了封装体积和重量,但成本相对较高。

4. 四方扁平无引脚封装(Quad Flat No-Lead Package, QFN)

QFN封装是一种无引脚结构,四边均有电极触点,适合高密度安装。它比传统的QFP(四方扁平封装)占用更少的电路板空间,且具有良好的热性能,广泛用于移动设备和无线通信领域。

5. 系统级封装(System in Package, SiP)

SiP技术将多个不同的芯片(如处理器、EPM570F256C4N存储器、传感器等)集成在一个封装内,形成一个完整的系统或子系统。这种封装方式能够实现高度集成,减少组件间的互连距离,提高系统性能和降低功耗,适用于智能穿戴、物联网设备等。

6. 晶圆级封装(Wafer Level Package, WLP)

WLP在整个晶圆级别进行封装,然后切割成单个芯片,极大地减小了封装尺寸,提高了封装效率。它特别适合于需要超小型封装的高性能、高密度应用,如智能手机和可穿戴设备中的芯片。

7. 扇出型封装(Fan-Out Package)

扇出型封装技术通过在芯片周围扩展封装材料并布置更多的I/O接口,实现了更高的引脚数和更小的封装尺寸。它支持更大的设计灵活性,有助于提升芯片的性能和降低功耗,是高端移动处理器和高性能计算应用的理想选择。

8. 三维封装(3D Packaging)

三维封装技术,如硅通孔(Through Silicon Vias, TSV)和堆叠封装,通过在垂直方向上堆叠芯片或使用穿透硅片的导电通孔来缩短信号传输路径,提高数据传输速度和降低能耗。这种技术对于高性能计算、存储和图像处理等领域尤为重要,可以实现前所未有的系统集成度和性能。

综上所述,不同的封装工艺各有优势,选择合适的封装技术需根据具体的应用需求、成本预算、性能指标以及市场趋势综合考虑。随着半导体技术的持续进步,新的封装技术还将不断涌现,以满足未来电子设备对更小、更快、更智能的需求。