Z8018X微处理器提供指令集和CPU寄存器

日期:2019-10-18Z8018X微处理器操作

显示功能、一般说明、管脚说明、块

Z8018X微处理器工作模式的图表、寄存器和详细信息。

软件体系结构

为Z8018X微处理器提供指令集和CPU寄存器。

直流特性

提出了直流参数和绝对最大额定值的Z8x180英里/小时。

交流特性

介绍了Z8018X微处理器的交流参数。

时序图

包含Z8018X的时序图和标准测试条件MPU。

附录

致Zilog MPU的Z8018X系列:

•指令集

•指令汇总表

•操作代码图

•每个机器周期和中断中的总线控制信号条件

条件

•运行模式总结

•状态信号

•I/O寄存器和订购信息

Z80180、Z8S180、Z8L180 MPU操作

特征

•工作频率为33 MHz

•片上mmu支持扩展地址空间

•两个DMA通道

•片上等待状态发生器

•两个通用异步接收器/发射器(UART)通道

•两个16位定时器通道

•片上中断控制器

•片上时钟振荡器/发生器

•时钟串行I/O端口

•代码与Zilog Z80 CPU兼容

•扩展指令

一般说明

基于微代码执行单元和先进的cmos制造技术,Z80180、Z8S180、Z8L180(Z8x180)是8位MPU,具有降低系统成本和低成本的优点提供更高性能和维护的电源操作与大量行业标准软件的兼容性围绕Zilog Z8X CPU。

更高的工作频率可以获得更高的性能,减少指令执行时间,增强指令集,以及具有以下能力的片上存储器管理单元(MMU)寻址高达1 MB的内存。

通过合并几个关键系统,降低了系统成本使用CPU实现片上功能。这些关键功能包括I/O设备例如DMA、UART和定时器通道。芯片上还包括动态RAM刷新控制、等待状态等多种粘合功能发电机、时钟振荡器和中断控制器。

Z8x180不仅在

正常操作,但具有Z8S180和Z8L180类的处理器处理器还提供了两种操作模式,旨在进一步大幅降低功耗。睡眠模式通过将CPU置于停止状态来降低功耗,从而在片上i/o设备仍在工作时,消耗更少的电流。

系统停止模式将CPU和片上外围设备进入停止状态,从而降低功耗更进一步。

当与其他cmos vlsi器件和存储器相结合时,Z8x180为需要高性能,低功耗运行。

Z8x180 MPU中的三针封装

家庭:

•64针双列直插式封装(DIP)

•68针塑料引线芯片载体(PLCC)

•80针四方扁平封装(QFP)

其他基于Z8x180的产品的引脚输出包说明如下

包含在各自的产品规范中。

Z8x180的配置。

管脚说明

a0-a19级。地址总线(输出,高电平,3状态)。a0-a19表格a 20-位地址总线。地址总线为存储器数据提供地址总线交换,高达1 MB,I/O数据总线交换,高达64K。地址总线在复位和外部总线期间进入高阻抗状态确认周期。地址线A18与PRT信道1(TOUT,复位时选择为地址输出)和地址行A19在DIP版本的Z8x180中不可用。

布萨克。总线确认(输出,有效低)。BUSACK指示请求设备、微处理器地址和数据总线,以及控制信号,已进入高阻抗状态。

总线请求总线请求(输入,低激活)。此输入由外部设备(如DMA控制器)请求访问公共汽车系统。此请求的优先级高于NMI,并且总是在当前机器循环结束时识别。这个信号停止CPU执行进一步的指令并放置地址和数据总线和其他控制信号进入高阻抗状态。

cka0,cka1。异步时钟0和1(双向,高电平活动)。

这些pin是asci信道的发送和接收时钟。

cka0与dreq0多路复用,cka1与dreq0多路复用趋势0克!串行时钟(双向,高电平)。这条线是钟CSIO频道。

时钟(phi)系统时钟(输出,高电平)。使用输出作为MPU和外部系统的参考时钟。频率这个输出等于晶体或输入时钟的一半。

频率。

cts0。cts1。清除发送0和1(输入,低激活)。这些线是用于ASCI信道的调制解调器控制信号。CTS1与RX多路复用。

d0–d7。数据总线(双向、高电平、三态)。d0-d7构成一种8位双向数据总线,用于向和传输信息从I/O和内存设备。数据总线进入高阻抗复位和外部总线确认周期期间的状态。

DCd0号。数据载波检测0(输入,低电平有效)。此输入是ASCI通道0的可编程调制解调器控制信号。

德雷克,德雷克。DMA请求0和1(输入,低电平)。德雷克是用于从一个片上dma信道请求dma传输。

DMA通道监视这些输入,以确定外部设备已准备好进行读或写操作。这些输入可以是编程为水平或边缘感应。DREQ0被多路复用用CKa0。

e.启用时钟(输出,激活高)。同步机周期时钟总线事务期间的输出。

外文。外部时钟/晶体(输入,高电平)。晶体振荡器连接。外部时钟可通过该引脚输入到Z8x180不使用水晶时。这个输入是施密特触发的。

停下。停止/睡眠状态(输出,低电平)。此输出被断言在CPU执行了HALT或SLP指令之后,操作前等待不可屏蔽或可屏蔽中断可以继续。halt还与m1和st信号一起用于解码CPU计算机周期的状态。

国际。屏蔽中断请求0(输入,低电平)。这个信号是由外部I/O设备生成。CPU在最后接受这个请求只要NMI和BUSREQ信号不活动。CPU用一个中断确认周期。在这个循环中,m1和iorq信号激活。

国际1,国际2。屏蔽中断请求1和2(输入,低电平)。

此信号由外部I/O设备生成。CPU尊重这些当前指令周期结束时的请求,只要NMI,BUSREQ和INT0信号未激活。CPU承认这些具有中断确认周期的中断请求。不像对int0的确认,在此循环期间,m1或iorq都不是信号激活。

IORQ公司。I/O请求(输出,低激活,3状态)。IORQ表示地址总线包含用于I/O读取或I/O写入的有效I/O地址操作。iorq也与m1一起在对INT0输入信号的确认,以指示中断响应向量可以放在数据总线上。这个信号是类似的Z64180的IOE信号。

M1号。机器循环1(输出,低激活)。连同mreq,m1指示当前周期是指令执行。与iorq一起,m1表示电流循环用于中断确认。它也用于刹车和用于解码CPU机器循环状态的ST信号。这个信号是类似于Z64180的LIR信号。

先生。内存请求(输出,低激活,3状态)。mreq表示地址总线为内存读取或内存保留有效地址写操作。这个信号类似于Z64180的ME信号。

NMI公司。不可屏蔽中断(输入,负边缘触发)。NMI有优先级高于int,并且总是在指令,不管中断使能触发器的状态如何。这个信号强制CPU在位置0066H继续执行。

读取(输出激活低,3状态)。rd表示cpu需要从存储器或I/O设备读取数据。寻址I/O或存储器设备必须使用此信号将数据传送到CPU数据总线。

RFSH。刷新(输出,活动低)。与MREQ、RFSH一起指示当前CPU计算机周期和地址总线必须用于动态存储器的刷新。低阶地址总线(A7–a0)的8位包含刷新地址。

该信号类似于Z64180的参考信号。

PRT通道1。这条线路与地址总线的A18多路复用。txa0,txa1。传输数据0和1(输出,高电平)。这些信号是来自asci信道的传输数据。传输数据变化与发送时钟的下降沿有关。

TXS。时钟串行传输数据(输出,高电平)。这条线是从CSIO通道传输的数据。

等待。等待(输入;有效低)。wait向cpu指示地址存储器或I/O设备未准备好进行数据传输。这个输入用于将额外的时钟周期引入当前机器循环。等待输入在t2的下降沿取样(和随后的等待状态)。如果输入采样低,则插入等待状态,直到对等待输入进行高采样,此时时间执行继续。

总重。写入(输出,低电平,3态)。wr表示cpu数据总线保存要存储在地址I/O或内存位置的有效数据。

XTAL公司。晶体(输入,高活性)。晶体振荡器连接。这个如果使用外部时钟而不是晶体,则插针必须保持打开状态。这个振荡器输入不是TTL电平(参考直流特性)

建筑

Z8x180结合了一个高性能CPU内核和多种系统和I/O资源在广泛的应用中非常有用。中央处理器核心由五个功能模块组成:时钟发生器、总线状态控制器(包括动态存储器刷新)、中断控制器、存储器管理单元(MMU)和中央处理器(CPU)。这个集成I/O资源构成其余四个功能块:•直接内存访问(DMA)控制(2个通道)

•异步串行通信接口(ASCI,2通道)表2.多路复用管脚描述多路复用

管脚说明

复位时,该引脚初始化为18引脚。如果定时器控制寄存器(TCR)的TOC1或TOC0位为设为1时,选择TOUT功能。如果toc1和toc0位清除为0,则选择A18功能。

CKa0/德雷克0复位期间,该引脚初始化为CKa0别针。

如果dma模式寄存器(dmode)中的dm1或sm1是设置为1时,始终选择DREQ0函数。

CKA1/趋势0复位时,该引脚初始化为CKA1引脚。如果asci控制寄存器ch 1(cntla1)中的cka1d位设置为1,选择Tend0功能。如果cka1d位设置为0,选择CKA1功能。

RXS/CTS1型在重置期间,此pin初始化为rxs pin。如果CTS1E位在ASCI状态寄存器中,ch 1(stat1)被设置为1,cts1函数被选中。如果cts1e位为0,则选择rxs函数。

Z 8018X家用手动UM005001-ZMP0400型

•可编程重新加载计时器(PRT,2通道)

•时钟串行I/O(CSIO)通道。

其他Z8x180家庭成员(如Z80183、Z80S183、Z80185/195)除这些模块外,还包括其他外围设备和在相关产品规范中时钟发生器该逻辑从外部晶体或时钟输入。外部时钟除以2,并提供给两者内部和外部设备。

总线状态控制器此逻辑执行所有相关的状态和总线控制活动有CPU和一些片上外设。这包括等待状态计时、重置周期、DRAM刷新和DMA总线交换。

中断控制器此块监视和优先处理内部和外部的各种中断和陷阱以提供来自CPU的正确响应。到与Z80 CPU保持兼容,有三种不同的中断模式支持。

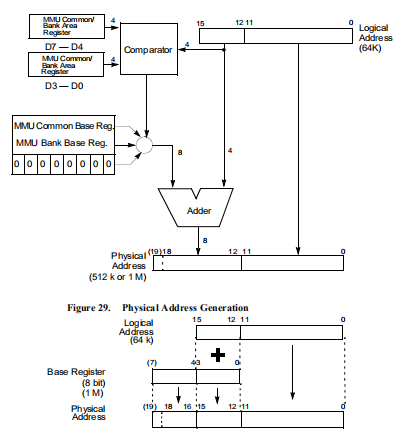

存储器管理单元mmu允许用户映射cpu使用的内存(逻辑上仅64K)进入Z8x180支持的1MB寻址范围。这个mmu目标代码的组织特性与z80的兼容性CPU,同时提供对扩展内存空间的访问。这种能力通过使用有效的公共区域库区域来完成计划。

UM005001-ZMP0400型

中央处理器

CPU是微编码的,以提供与目标代码兼容的核心使用Z80 CPU。它还提供了Z80指令集的超集,包括8位乘法和除法。这个核心已经得到增强,允许许多指令在更少的时钟周期内执行。

DMA控制器

DMA控制器在存储器和I/O设备。支持的传输操作是内存到内存,内存到/从I/O和I/O到I/O。支持的传输模式有请求、突发和循环窃取。DMA传输可以访问完整的1MB寻址范围,块长度高达64KB,可以交叉超过64K边界。

异步串行通信接口asci逻辑提供两个独立的全双工uart。每个信道包括可编程波特率发生器和调制解调器控制信号。asci通道还可以支持多处理器通信格式。

可编程重新加载定时器(PRT)这个逻辑由两个独立的通道组成,每个通道包含一个16位计数器(定时器)和计数重新加载寄存器。计数器的时基是在到达计数器。PRT通道1提供一个可选输出,允许波形生成。

时钟串行I/O(CSIO)CSIO通道提供半双工串行发射器和接收器。

此通道可用于简单的高速数据连接另一个微处理器或微型计算机

CPU计时

•指令(操作码)获取定时

•操作数和数据读/写定时

•I/O读/写计时

•基本指令(获取和执行)计时

•重置计时

•BUSREQ/BUSACK总线交换定时基本的cpu操作由一个或多个机器周期(mc)组成。

一个机器周期由三个系统时钟组成:T1、T2和T3,访问内存或I/O,或由一个系统时钟(T1)组成CPU内部操作。系统时钟是晶体振荡器(即,8兆赫晶体产生4兆赫或250毫微秒)。

用于连接慢速内存或外围设备,可选等待状态(TW)可插入T2和T3之间。

指令(操作码)不等待的获取时间国家。当m1输出引脚低。

在T1的前半部分,地址总线(a0–a19)由程序计数器(PC)的内容。这个地址总线是Z8x180片上MMU的地址输出。

在T1的后半段,MREQ。(内存请求)和rd(读取)信号被断言为低,从而启用内存。

MMU和复位

复位时,CBAR的CA字段的所有位都设置为1,而所有位cbar的ba字段中,cbr和bbr重置为0。逻辑64KB地址空间与第一个64kb 0000h到ffffh直接对应)1024kb00000h.到fffff h)物理地址空间。因此,在复位后,Z8x180在逻辑和物理地址0开始执行。

mmu寄存器访问定时当数据写入CBAR、CBR或BBR时,该值有效从紧接着更新的I/O写入周期之后的周期这些登记册。

在mmu编程期间,确保cpu程序的执行不是中断。mmu寄存器编程后的下一个循环是通常是从新翻译的地址获取操作码。一个技术是将所有mmu编程例程本地化为始终启用的区域。

物理地址生成