VSP2267是一个完整的混合信号集成电路

日期:2019-11-22介绍

1.1说明

采用CCD时序发生器和a/D转换器对CCD信号进行处理。系统同步主时钟、HD和VD。VSP2267支持CCD和垂直驱动器所需的所有信号终端,以及外部触发的机械快门和选通功能。R驱动和H驱动同步A/D转换器的时钟相位,以实现理想的性能。CCD通道通过相关双采样(CDS)从CCD输出信号中提取图像信息。数字控制增益曲线以分贝为单位呈线性,范围从-6分贝到42分贝。黑电平箝位电路保证了准确的黑电平基准和增益变化后的快速黑电平恢复。可使用带有CDS偏移调整功能的输入信号夹紧。

1.2特点

VSP2267支持以下功能:

CCD信号处理:

–相关双采样(CDS)

–可编程黑色水平夹紧

带R和H驱动器的定时发电机

可编程相位控制:

–精细步长:0.6 ns

–宽台阶:8 ns

可编程增益放大器(PGA):–6分贝至42分贝增益范围

12位数字数据输出:

–最高25 MHz转换率

–无缺失代码

信噪比:79分贝

便携式操作:

–低压:3.0 V至3.6 V

–低功率:3.0 V时为138兆瓦,3.0 V和25 MHz时为20兆赫151兆瓦

–待机加省电模式:34兆瓦

–MCLK关闭模式:6兆瓦

推荐CCD:MN39470、MN39471、MN39472、MN39473、MN39474(松下)

终端分配

操作理论

简介

VSP2267是一种高分辨率的混合信号集成电路,包含与数字静态相机(DSC)中的CCD信号处理相关联的关键特性。VSP2267集成了模拟前端(AFE)和CCD定时发生器(TG)以及H和R驱动器。

AFE模块包括相关双采样器(CDS)、14位模数转换器(ADC)、数字增益放大器、黑电平箝位回路、输入箝位、CDS定时发生器和电压基准。内置TG不仅生成水平(H-速率)定时,还生成几个特定CCD模型的垂直(V-速率)定时。通过串行接口选择CCD的型号和工作模式,生成优化的时序。

定时发电机(TG)

TG产生H-速率定时和V-速率定时。

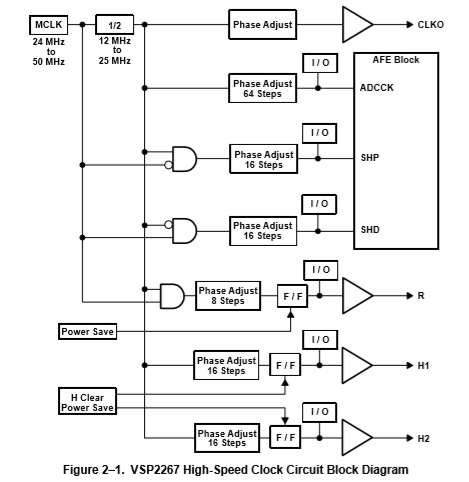

TG的高速定时块。该部分产生六个用于H-速率定时的高速脉冲,如R、H1/H2、SHP/SHD和ADCCK。这些高速脉冲由主时钟产生,主时钟的速度是像素速率的两倍。串行接口以16步(R为8步)设置这些高速脉冲的相位调整量,最小间距为0.6 ns(R为4步0.6 ns,R为4步1.2 ns)。电源模式控制输出驱动器启用/禁用。片上解码器根据CCD模型和工作模式计算H clear。H1、H2和R可以直接驱动CCD。ADCCK、SHP、SHD、R、H1和H2脉冲可以选择内部生成模式或外部供应模式。

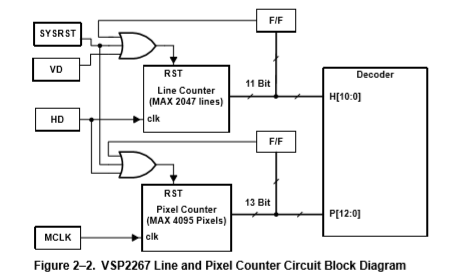

VSP2267高速时钟电路框图片上V速率定时发生器产生特定CCD图像传感器所需的所有信号。TG包含用于生成V速率定时的行计数器和像素计数器。测线和像素计数器电路的框图。在时间尺度上支持最多2047行和每行4095像素。

VSP2267线像素计数器电路框图

V-速率定时发生器框图。在CCD读出前1小时(水平线),用户必须完成串行数据传输,数据必须加载到包含CCD型号、工作模式、积分时间和电子变焦区域信息的寄存器中。就在CCD读出之前,寄存器中的信息被自动提供给解码器,解码器使用行计数器和像素计数器数据生成V速率信号。不仅支持用于CCD的信号,还支持选通光控制信号。CPOB、CLPD和PBLK可以选择内部发电模式或外部供电模式。

VSP2267垂直速率定时电路框图

模拟前端

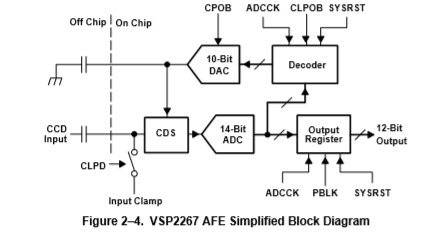

VSP2267的简化AFE框图。AFE电路包括相关双采样器(CDS)、14位模数转换器(ADC)、数字增益放大器、黑电平箝位回路、输入箝位、CDS定时发生器和电压基准。在CCD输出和VSP2267 CCDIN输入之间需要一个片外发射器跟随器缓冲器或前置放大器。

相关双采样器(CDS)

CCD图像传感器的输出信号在一个像素周期内采样两次:在参考间隔内采样一次,在数据间隔内采样一次。减去这两个样本,提取像素的视频信息,去除低频噪声kTC和CCD复位噪声。

CDS通过片外耦合电容器C驱动(对于C,建议使用0.1μF电容器)。强烈建议使用交流耦合,因为CCD输出信号的直流电平通常过高(几伏),CDS无法正常工作。CDS的适当共模电压约为0.5v–1.5v。在SHP激活时执行基准电平采样,电压电平保持在SHP后缘的采样电容器C上。数据电平采样在SHD激活时进行,电压电平保持在SHD后缘的采样电容器C上。然后通过开关电容放大器对两个电平进行相减。片外发射极跟随器或等效缓冲器必须能够驱动10 pF以上,因为在输入端可以看到10 pF采样电容器。(通常存在少量pF的附加杂散电容)VSP2267的模拟输入信号范围约为1vp-p

输入线夹

缓冲CCD输出电容耦合到VSP2267。输入钳位恢复输入信号的直流分量,该直流分量因交流耦合而丢失,并为CDS建立所需的直流偏置点。图2-5还显示了输入钳位的框图。在虚拟像素间隔期间,输入电平被钳制到内部参考电压CM(1.5v)。更具体地说,当CLPD和SHP都处于活动状态时,夹紧功能变为活动状态。

4位A/D转换器

ADC采用全差分流水线结构,每级1.5位,非常适合低功耗、低电压和高速应用。ADC为整个刻度提供14位分辨率。ADC的每级1.5位结构有利于在较小的信号电平下实现更好的线性度。改进的线性发生是因为大的线性误差倾向于在满标度的特定点处发生,并且对于低于任何这样的特定点的信号电平,线性改善。

数字可编程增益放大器(DPGA)

DPGA增益的特性。DPGA提供-6分贝到42分贝的增益范围,这是线性分贝。增益由具有10位分辨率的数字代码控制,可通过串行接口进行设置;有关详细信息,请参阅串行接口定时规范(第3节)。增益控制代码的默认值为128(PGA增益=0 dB)。

通电后,增益控制值待定。因此,必须使用串行接口将其设置为适当的值,或通过敲击SYSRST终端将其重置为默认值。

AFE操作时间

CDS和ADC由SHP、SHD及其内部片上时序发生器产生的派生时序时钟操作。DPGA输出寄存器和解码器由ADCCK操作。数字输出数据与ADCCK同步。CCD信号、SHP、SHD、ADCCK和输出数据之间的时序关系如VSP2267时序规范所示。CPOB在OB像素间隔期间激活黑电平钳制循环,CLPD在虚拟像素间隔期间激活输入钳制。

黑色电平钳位回路和10位DAC

为了正确地提取视频信息,CCD信号必须参考一个公认的黑电平。VSP2267有一个自动调零回路(校准回路),用于使用CCD光学黑色(OB)像素建立黑色水平。图2-7显示了这个循环的框图。来自OB像素的输入信号电平被识别为真正的黑色电平,并且在该期间(实际上在CPOB=活动期间)环路闭合。当自动零环闭合时,对ADC输出码之间的差异进行评估并应用于解码器,然后解码器控制10位电流DAC。电流DAC可以在COB处对外部电容器充电或放电,这取决于码差的符号。环路调整COB处的电压,COB设置CDS的偏移量,使码差为零。因此,ADC输出码在CPOB=ACTIVE期间收敛到黑电平,并在循环收敛后保持从OB像素导出的黑电平。CPOB同时执行两个信道的OB钳位。

为了确定环路时间常数,需要一个片外电容器,并应连接到COB端子。

其中C是连接到C OB的电容值,I是OB电平钳位回路中控制DAC的最小电流(0.15μA),0.15μA等于DAC输出电流的1lsb。当C为0.1μF时,ADC输出码的时间常数T为40.7μs,从0 LSB到1543 LSB(收敛曲线变成指数)。最小值

对于高于1543 LSB的输出码,电流DAC注入恒定(最大)电流到电容器,并且收敛曲线变为线性。

其中C是连接到COB的电容值。在OB电平箝位环中,I是控制DAC的最大电流(153μA),153μA相当于DAC输出电流的1023 LSB。马克斯

一般来说,高速的OB电平箝位会产生箝位噪声。但是,通过增大C可以降低噪声。另一方面,一个大的C需要更长的时间才能从省电模式恢复,或者在电源接通后立即恢复。因此,0.1μF至0.22μF被认为是C的合理值。如果应用环境要求此范围之外的值,建议通过试错法进行仔细调整。

OB钳位(基座位)可通过串行接口编程;详细信息请参见串行接口定时规范(第3节)。有关输入代码和OB钳位电平之间的关系,另请参阅串行接口时序规范一节。

黑电平箝位环路不仅消除了CCD的黑电平偏移,而且还消除了VSP2267 CDS和ADC本身的偏移。

预消隐和数据延迟

VSP2267具有预消隐功能。当PBLK=低时,数字输出在ADCCK的第九上升沿处全部变为零,从PBLK变低时开始计数,以适应VSP2267的时钟延迟。

此设备的数据延迟为七个时钟周期。数字输出数据以七个时钟周期的延迟在ADCCK的上升沿上输出。

一些ccd在消隐间隔期间具有大的瞬态输出信号。如果输入电压高于供电轨或低于接地轨0.3 V,则保护二极管打开,限制输入电压。这种高摆幅信号会对VSP2267造成设备损坏,应避免。

节电模式

为了省电,VSP2267可以通过串行接口命令进入待机加省电模式。在该模式下,通过配置串行接口命令,所有功能块被禁用,A/D输出全部归零,TG输出进入高或低状态。电流消耗降至34毫安。由于所有旁路电容器在此模式下放电,因此需要相当长的时间(通常为200-300 ms)才能从待机加省电模式恢复。

附加输出延迟控制

VSP2267可以通过串行接口设置寄存器来控制输出数据的延迟时间。在某些情况下,输出数据的转换会影响模拟性能。通常,通过调整ADCCK的定时来避免这种情况。在ADCCK定时不能调整的情况下,附加的输出延时控制对减小瞬态噪声的影响是有效的。有关详细信息,请参阅串行接口定时规范(第3节)。

参考电压

设备上使用的所有参考电压和偏置电流都是由内部带隙电路产生的。

CDS和ADC主要使用三种参考电压:REFP(1.75v)、REFN(1.25v)和CM(1.5v)。REFP和REFN在芯片上缓冲。CM被导出为内部连接REFP和REFN的电阻链的中间电压。ADC满标度范围由REFP和REFN之间的电压差的两倍确定。

REFP、REFN和CM应使用适当的电容器严重解耦。

操作模式

场模式允许垂直相邻像素的总和。

帧模式支持每个像素输出。

×2速度模式启用输出间隔线。

×2监视模式可分别为CCDs 2A或2B输出2×8线或2×10线。

场模式、帧模式和×2速度模式在偶数/奇数帧之间进行交错操作。

功能

长积分功能根据串行数据指令的定义,在一帧结束时停止CCD读出(CH1、CH2、CH3、CH4脉冲)。

省电功能通过串行数据指令停止所有时钟并保持高电平或低电平。

频闪灯功能允许外部频闪灯操作通过串行数据指令同步电子快门定时。

电子变焦功能启用电子变焦,根据串行数据指令选择连续的行。

电子快门功能通过串行数据指令启用电子快门操作。

分站1/4步功能允许通过串行数据指令从一条线上的四个点中选择子脉冲位置。

TG垂直速率操作

现场模式操作

运行大纲

CCD的水平输出是通过对彼此垂直相邻的像素求和,并依次对每个CCD像素列重复求和而产生的。奇数场或偶数场都是可选的。

操作顺序

设置串行数据地址000100位6–5=00。

通过VD和HD的关系或串行地址000100位8–7来定义奇数/偶数。

静止功能

运行大纲

读出定时由TRG输入选择。与机械快门同步的拖影转储操作可用。

子输出由串行数据指令和外部TRG信号控制。

SUBSW级别遵循静止模式条件。当使用机械快门时,SUBSW可用于副偏压控制电路。建议在机械快门关闭后设置SUBW的切换位置。

1. 设置串行数据地址000101。

输入位2=H,并设置为静止模式。

选择触发信号EDGSL bit 3=L(VD)或bit 3=H(TRG)。

选择子输出STLSUB位4=L(用于TRG输入)或位4=H(用于串行数据输入)。

(在这种情况下,子输出由TRG输入定义。要使用串行数据指令,集成时间由ES 000111定义,可在以下步骤2之后完成。)

2. 输入一个脉冲到SLOAD并发送串行数据。

3. 设置串行数据地址001010。输入STVV数据(0–5位),用于子波上升时间定义。数据在读出操作前1h存储在寄存器中。在进入静止模式时,在读出操作之前的水平扫描时间内,每H产生一个子输出,并且电荷被耗尽。

4. 必要时输入TRG下降沿信号。TRG下降沿由内部HD_flg锁定。下一个水平空白后,子输出变高,开始电荷积分。见注1。

5. 输入TRG上升沿或VD信号。SUBSW在串行数据定义的位置变高。通过计算TRG或VD上升沿后的HD脉冲数来确定SUBSW切换位置。应用一个垂直的高速脉冲,它大于一个场的行号。

6. 将串行数据输入地址000101处的位3=L,并在步骤5中启动的垂直高速脉冲操作期间释放触发器选择功能。

7. 一场CCD输出信号完成后,输入一个VD脉冲,使SUBSW保持高。

8. 输入串行数据用于地址000101和位2=L从静止模式退出。

9. 完成一个CCD输出信号场后,输入一个VD脉冲。潜艇在下一个高清上升沿下降。

笔记:

1. 在该模式下,机械快门在TRG输入低时打开。

2. 当SUBW高时,不要在静止模式下使用电子快门。

3. 对于VD到VD间隔,需要超过90个HD到HD间隔计数。

选通(STO输出)功能

运行大纲

STO输出由串行数据指令启动,包括STO信号位置和持续时间。

操作顺序

1. 在地址001010处为STO(选通)上升点指令设置数据位6=H。见注1。

2. 输入一个脉冲到SLOAD并传输串行数据。

3. 在地址000110处为STO(选通)上升点指令设置数据位0–9。在这种情况下,使用从HD上升沿(10t)开始的数据ST[9:0]的二进制代码,该上升沿在读出脉冲后2 H。ST的数据范围是0≤n1≤A–2,其中A是VD–VD之间的HD数。见注3。

4. 输入一个脉冲到SLOAD并传输串行数据。

5. 在地址000101处为SWT duration指令设置数据位5–9。在这种情况下,使用数据SWT[9:5]的二进制代码,从STO上升沿(10t)开始。见注3。

6. 输入一个脉冲到SLOAD并传输串行数据。数据在读出操作前1小时存储在电阻器中。STO在串行数据指令确定的点处变高。当STO高电平的持续时间在两个HD脉冲之间超过SWT时,STO变低。见注2。

注:

1. 选通功能可用于正常模式和静止模式。所以频闪手术对预防红眼是有用的。

2. STO的上升时间和下降时间为10t。

3. 调整STO位置和宽度,使STO在读出操作前变低2 HD。

电子变焦功能

运行大纲

垂直CCD传输可实现垂直图像提取。

水平图像提取和缩放过程需要在该设备外部进行信号处理。

此模式允许有限区域的高速图像输出。

操作顺序

1. 设置串行数据地址000101。同时,输入数据位1=H,设置电子变焦模式。使用二进制地址001011和数据位0–9中的代码设置传输级的数量。数据范围见注4。见注释1-5。

2. 输入一个脉冲到SLOAD并传输串行数据。根据串行数据级指令,实现V1到V4输出的高速垂直传输。在高速传输之后,对每个H进行V1到V4的标准垂直传输。在下一个VD中,V1到V4的高速垂直传输被输出大约一个场。见注2。

注:

1. 此模式不能与静止模式组合。

2. 在电子变焦功能中,用户指令仅涉及读出操作之后的垂直高速传输。在读出操作之前,每个CCD模型的垂直高速传输数是固定的。

3. 在切换到该模式并从该模式释放后的1个字段中,无法保证信号性能。

4. 传输阶段设置如下:

0 ≤n≤640级(奇偶选择0.5级节距),注意n必须除以2。

[2B电荷耦合器件]

0 ≤n≤610级(奇偶选择0.5级节距),注意n必须除以5。

5. VD到VD之间的间隔必须大于90 HD。

读出功能

运行大纲

该模式可以控制垂直传输CCD中混合的一对像素。控制不是通过HD–VD阶段完成的,而是通过串行数据指令完成的。

操作顺序

1. 设置串行数据地址000100。同时,输入数据位7=H,设置串行数据控制模式。在这种情况下,读出定时由位8数据定义。当位8=L时,读取奇数字段;当位8=H时,读取偶数字段。

2. 输入一个脉冲到SLOAD并发送串行数据。

注:

如果位7=L,奇数/偶数读出识别由HD–VD相位差进行。

省电1功能说明

运行大纲

停止H1,R,V3,V4,CH1,CH2,CH3,CH4,SUB,SHP,SHD,CPOB,CLPDM,可省电,

PBLK=固定高

H1,ADCCK,V1,V2=固定低

操作顺序

1. 设置串行数据000100。将数据位PWSV1=H设置为进入省电模式。

2. 为SLOAD输入一个脉冲并传输串行数据。

笔记:

1. 从该模式释放后,1V期间信号性能无法保证。

2. 不要同时使用省电模式1和2。

省电-2功能说明

运行大纲

停止H1、H2、R、SHP、SHD、ADCCK、V1-V4、CH1-CH4、SUB、CPOB、CLPDM、PBLK以节省电力。

TG像素速率操作

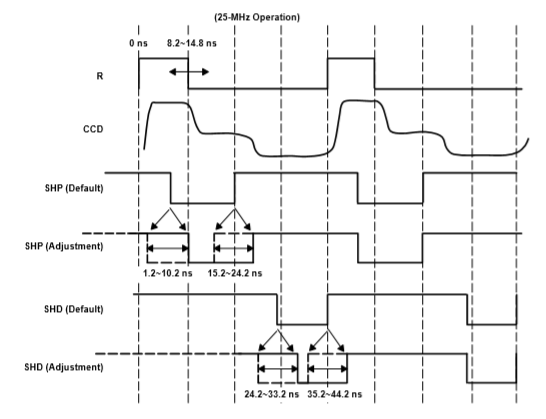

1高速脉冲调整

对于高速脉冲,CCD信号采样时间可调(见001100至010110的串行数据地址)。

高速时钟定时可调范围

默认计时值

R:标准复位持续时间为周期的25%。

SHP:基于3 ns CCD信号延迟,标准上升点为循环的50%。实际延迟取决于系统。

SHD:标准上升点为100%周期,基于3 ns CCD信号延迟。实际延迟取决于系统。

H1:标准持续时间为周期的50%。

H1和H2是互补的。H1上升沿和H2下降沿的交叉点应高于VDD/2。

H2:标准持续时间为循环的50%。

ADCCK:基于3 ns CCD信号延迟,标准上升点和下降点分别为周期的25%和75%。