AD7874是一个四通道同时采样的12位数据采集系统

日期:2019-12-7特征

四个On-C hip Track/Hold Am钳;4个C通道的同步采样;带8的快速12位ADCms转换时间e/C通道;所有四个C通道的29 kHz倍率;髋关节参考;610 V输入范围;65伏电源。

应用

苏纳尔;马达控制器;自适应滤波器;数字信号处理。

一般说明

AD7874是一个四通道同时采样的12位数据采集系统。该部分包括一个高速12位ADC、片上基准、片上时钟和四个跟踪/保持放大器。后一个特性允许同时对四个输入信道进行采样,从而保留四个输入信道的相对相位信息,如果所有四个信道共享一个单轨/保持放大器,则这是不可能的。这使得AD7874非常适合于相控阵声纳和交流电机控制器等相对相位信息非常重要的应用。

四个跟踪/保持放大器的孔径延迟很小,并且规定了最小和最大限度。这允许多个ad7874同时采样多个输入信道,而不会在连接到多个设备的信号之间产生相位误差。参考输出/参考输入设备还允许从同一参考源驱动多个AD7874。

除了线性、满标度和偏移误差等传统的直流精度规范外,AD7874还充分规定了包括失真和信噪比在内的动态性能参数。

AD7874采用模拟器件的线性兼容CMOS(LC2MOS)工艺制造,这是一种将精密双极电路与低功耗CMOS逻辑相结合的混合工艺。该部件有28针、0.6英寸宽的塑料或密封双列直插式封装(DIP)、28端无铅陶瓷芯片载体(LCCC)和28针SOIC。

产品亮点

1、四个输入通道的同时采样。四个输入通道,每个通道都有自己的跟踪/保持放大器,允许同时采样输入信号。跟踪/保持捕获时间为2微秒,每个信道的转换时间为8微秒,允许所有四个信道的29 kHz采样率。

2、紧密孔径延迟匹配。

每个通道的孔径延迟较小,四个通道之间的孔径延迟匹配小于4ns。此外,孔径延迟规范具有允许多个ad7874采样四个以上信道的上限和下限。

3、快速微处理器接口。

AD7874的高速数字接口允许直接连接到所有现代16位微处理器和数字信号处理器。

术语

采集时间

采集时间是跟踪/保持放大器输出达到其最终值所需的时间,在±1/2范围内LSB,在INT下降沿之后(track/holds返回track模式的点)。这包括开关延迟时间、旋转时间和满量程电压变化的稳定时间。

孔径延迟

孔径延迟定义为内部开关从输入端断开保持电容所需的时间。这在采样定时中产生有效延迟。它是由应用步进输入并调整CONVST输入位置,直到输出代码跟随步进输入更改。

孔径延迟匹配

孔径延迟匹配是跨越四个片上跟踪/保持放大器的孔径延迟的最大偏差。

孔径抖动

孔径抖动是由于内部噪声和开关阈值随信号电平变化而引起的孔径延迟的不确定性。

下降率

下垂率是由泄漏电流引起的保持模拟电压的变化。

通道间隔离

信道间隔离度是测量信道间串扰水平的一种方法。它是通过对其他三个输入应用满标度1khz信号来测量的。给出的数字是所有四个频道中最坏的情况。

信噪比、THD、IMD

参见动态规格部分。

转换器详细信息

AD7874是一个完整的12位4通道数据采集系统。它由一个12位逐次逼近。ADC,四个高速跟踪/保持电路,一个四通道模拟多路复用器和3伏齐纳基准。ADC采用逐次逼近技术,并基于快速沉降,电压开关DAC,高速比较器,快速CMOS合成孔径雷达和高速逻辑。

转换在CONVST的上升沿启动。全部四个输入轨迹/保持在此边上从一个轨迹转到另一个轨迹。转换首先在通道1输入电压上执行,然后在通道2被转换等等。这四个结果存储在片上登记册。当所有四个转换都完成时,INT变低表示可以从这些位置读取数据。转换序列采用78或79个上升时钟边缘取决于CONVST与CLK的同步。内部延迟和重置时间带来总转换时间从一个2.5 MHz的外部时钟从高到低到32.5的最大值。AD7874使用隐式寻址方案,其中对同一内存位置按顺序访问四个数据字。第一次读取访问通道1数据,第二次读取访问通道2数据等。单个数据寄存器不能独立访问。

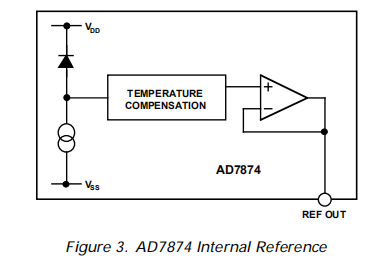

内部参考

AD7874有一个芯片内温度补偿埋置齐纳基准,工厂将其调整为3 V±10 mV(见图3)。参考电压在REF OUT引脚处提供。该参考电压可用于为ADC和双极偏置电路提供参考电压。这是通过将REF OUT连接到REF IN来实现的。

该基准还可以用作其他组件的基准,并且能够向外部负载提供高达500微安的电流。在使用多个AD7874的系统中,使用一个设备的REF OUT为其他设备提供REF In确保所有AD7874之间的良好满标度跟踪。由于AD7874 REF In被缓冲,每个AD7874对参考呈现高阻抗,因此一个AD7874 REF OUT可以驱动多个AD7874 REF In。

最大推荐电容

正常操作为50 pF。如果其他系统使用需要参考,则应使用200Ω电阻与10μF钽电容器和0.1μF陶瓷电容器的并联组合将其与AGND分离。

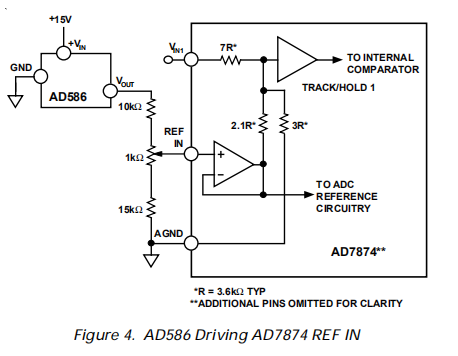

外部参照

在一些应用中,用户可能需要系统参考或一些其他外部参考来驱动AD7874参考输入。图4显示了如何使用AD586 5 V参考电压提供AD7874参考电压所需的3 V参考电压。

轨道保持放大器

AD7874的每个模拟输入端上的跟踪和保持放大器允许ADC将20 V p-p振幅的输入正弦波精确转换为12位精度。即使当ADC以其最大吞吐率操作时,跟踪/保持放大器的输入带宽也大于ADC的奈奎斯特速率。小信号3db截止频率通常出现在500khz。

四个跟踪/保持放大器同时对各自的输入通道进行采样。轨道/保持电路的孔径延迟很小,更重要的是,在一个设备上的四个轨道/保持之间匹配良好,并且在每个设备之间匹配良好。这使得不同输入通道之间的相对相位信息得以准确地保留。它还允许多个AD7874同时采样四个以上的信道。

跟踪/保持放大器的操作对用户基本上是透明的。一旦开始转换,四个通道将自动转换,无需选择要数字化的通道。

模拟输入

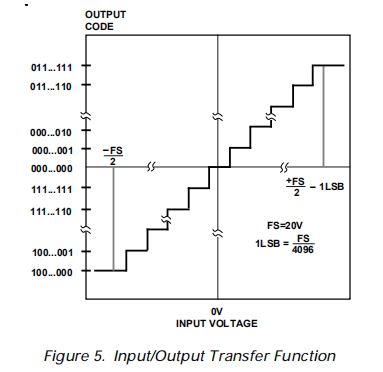

AD7874的通道1的模拟输入如图4所示。模拟输入范围为±10 V,输入电阻通常为30 kΩ。设计的代码转换发生在连续整数LSB值(即1/2 LSB、3/2 LSB、5/2 LSB)之间的中间。. . FS–3/2 LSB)。输出代码为2s补码二进制,1lsb=FS/4096=20v/4096=4.88mv。理想的输入/输出传递函数如图5所示。

偏移和满刻度调整

在大多数数字信号处理(DSP)应用中,偏移量和满标度误差对系统性能影响很小或没有影响。通过交流耦合,可以消除模拟域中的偏移误差。满标度误差效应是线性的,只要输入信号在ADC的全动态范围内,就不会引起问题。一些应用程序总是要求输入信号跨越整个模拟输入动态范围。在这种应用中,必须将偏移量和满标度误差调整为零。

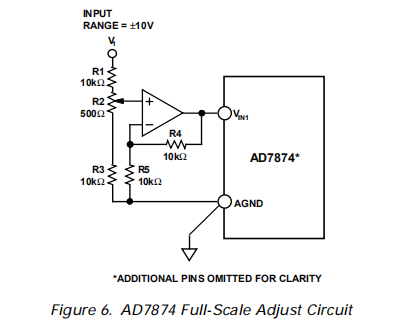

图6显示了可用于调整AD7874上的偏移和满标度误差的电路(所示的信道1仅用于示例目的)。当需要调整时,必须在满标度误差之前调整偏移误差。当输入电压低于模拟地1/2 LSB时,通过微调驱动AD7874的模拟输入的运算放大器的偏移量来实现。微调程序如下:在图6中的V1处施加-2.44 mV(–1/2 LSB)的电压,并调整运放偏移电压,直到ADC输出代码在1111 1111 1111和0000 0000 0000之间闪烁。

增益误差可以在第一次代码转换(ADC负满标度)或最后一次代码转换(ADC正满标度)时调整。两种情况下的修整程序如下:

正满标度调整

在V1处施加+9.9927 V(FS/2–3/2 LSBs)的电压。调整R2,直到ADC输出代码在0111111111110-ic/" title="0111111111110">0111111111110和0111111111之间闪烁。

负满标度调整

在V1处施加-9.9976 V(–FS+1/2 LSB)的电压,并调整R2,直到ADC输出代码在1000 0000和1000 0000 0001之间闪烁。

在使用外部基准的系统中,调整满标度误差的另一种方案是调整REF in pin处的电压,直到调整出任何信道的满标度误差为止。通道的良好满标度匹配将确保其他通道的小满标度误差。

时间和控制

通过断言转换输入。这个CONVST输入是一个独立于ADC时钟的异步输入。这对于在时间上进行精确采样非常重要的应用来说是必不可少的。在这些应用中,信号采样必须以完全相等的间隔进行,以最小化由于采样不确定性而产生的误差或者抖动。在这些情况下,CONVST输入由定时器或精确的时钟源驱动。一旦转换开始,在所有四个通道上的转换完成之前,不应再次断言CONVST。

在精确时间间隔采样不重要的应用中-cal,CONVST脉冲可以由微处理器写或读线路产生,该线路用解码地址选通(与AD7874 CS地址不同)。CONVST不应仅从解码地址派生,因为它非常短CONVST脉冲(在某些微处理器系统中,由于地址总线在指令周期开始时发生变化)可以启动转换。

所有四个声道/保持放大器在CONVST脉冲上升沿上从一个声道到另一个声道保持。四个声道/保持放大器在转换所有四个声道时保持其保持模式。CONVST的上升沿还启动通道1输入电压(VIN1)的转换。当在通道1上完成转换时,其结果存储在数据寄存器1中,数据寄存器1是用于存储转换结果的四个片上寄存器之一。当存储第一次转换的结果时,在磁道/保持2保持的电压上启动转换。当在轨道/保持4保持的电压上完成转换时,其结果是存储在数据寄存器4中,INT变低表示转换过程已完成。

发生信道转换的序列由AD7874自动处理。这意味着用户不必向AD7874提供地址线,也不必担心选择要数字化的信道。

从设备读取数据包括对同一微处理器地址的四次读取操作。四个片上数据寄存器的寻址再次由公元7874年。转换后对AD7874的第一次读取操作总是从数据寄存器1访问数据(即,转换结果从VIN1输入)。INT在在第一次读取操作期间执行RD。第二次读取总是从数据寄存器2访问数据,以此类推。地址指针重置为指向数据寄存器1的上升沿康斯特。转换期间不应尝试对AD7874执行读取操作。AD7874转换序列的时序图如图7所示。

AD7874动态规格

AD7874被指定并100%测试动态性能规范以及传统的直流规范,如积分和微分非线性。这些交流规范是相控阵声纳、自适应滤波器和频谱分析等信号处理应用所必需的。这些应用需要有关ADC对输入信号光谱含量影响的信息。因此,规定AD7874的参数包括信噪比、谐波失真、互调失真和峰值谐波。这些术语将在下面的章节中详细讨论。

信噪比

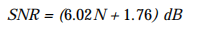

SNR是在ADC输出端测得的信噪比。信号是基波的有效值大小。噪声是所有非基本信号的均方根和,不包括直流电,其最大值为采样频率(fs/2)的一半。信噪比取决于数字化过程中使用的量化级别的数量;级别越多,量化噪声越小。正弦波输入的理论信噪比由:

其中N是位数。因此,对于理想的12位转换器,信噪比为74分贝。

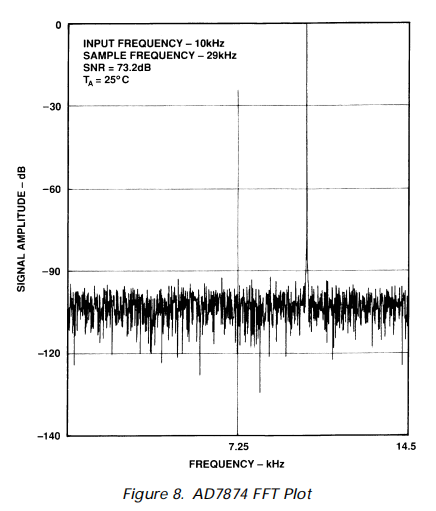

通过对以29 kHz采样率采样的车辆识别号输入应用非常低失真的正弦波信号来评估来自ADC的输出频谱。生成一个快速傅里叶变换(FFT)图,从中可以获得信噪比数据。图8显示AD7874BN的典型2048点FFT图,输入信号为10 kHz,采样频率为29 kHz。由该图得到的信噪比为73.2db。在计算信噪比时应考虑谐波。

有效位数

方程1中给出的公式将信噪比与比特数联系起来。重写公式,如在等式2中,可以得到以有效比特数(N)表示的性能度量。

一个设备的有效位数可以直接从其测量的信噪比计算出来。

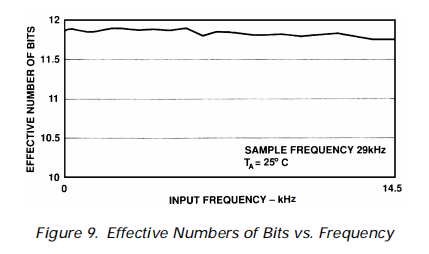

图9显示了采样频率为29 kHz的AD7874BN的有效比特数与频率的典型关系图。有效比特数通常在11.75到11.87之间,对应于72.5db的SNR数字和73.2分贝。

总谐波失真(THD)

总谐波失真(THD)是谐波的均方根和基波的均方根值之比。对于AD7874,THD定义为:

其中,V 1是基波的均方根振幅,V 2、V3、V4、V5和V6是二次谐波到六次谐波的均方根振幅。THD也由ADC输出频谱的FFT图导出。

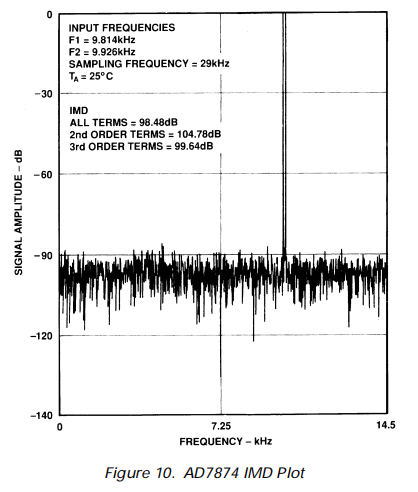

互调失真

当输入由两个频率(fa和fb)的正弦波组成时,任何具有非线性的有源器件都会在mfa±nfb的和频和差频产生畸变产物,其中m,n=0,1,2,3。……等。互调项是指m或n都不等于零的互调项。例如,二阶项包括(fa+fb)和(fa-fb),三阶项包括(2fa+fb),(2fa-fb),(fa+2fb)和(fa-2fb)。

使用CCIF标准,其中使用接近输入带宽顶端的两个输入频率,二阶和三阶项具有不同的重要性。二阶项通常在频率上与原始正弦波相距较远,而三阶项通常在接近输入频率的频率上。因此,二阶和三阶术语是分开指定的。互调失真的计算是根据THD规范进行的,其中它是单个失真产品的rms和与以dBs表示的基波的rms振幅的比值。在这种情况下,输入由两个等幅低失真正弦波组成。图10显示了AD7874的典型IMD图。

峰值谐波或杂散噪声

谐波或杂散噪声被定义为ADC输出频谱中下一个最大分量(最高fs/2,不包括dc)的均方根值与基波的均方根值之比。通常,本规范的值将由频谱中最大的谐波确定,但对于谐波埋入噪声层的部分,峰值将是噪声峰值。

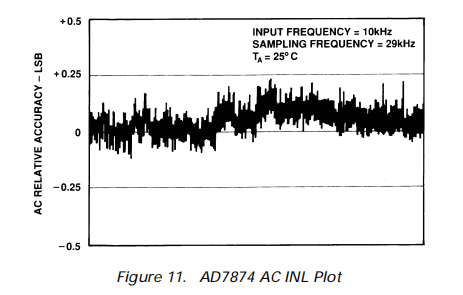

交流线性图

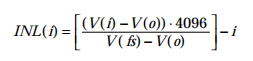

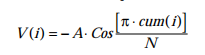

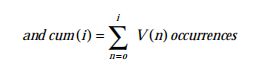

当对AD7874的VIN输入施加指定频率的正弦波并采集数百万个样本时,可以生成显示4096 ADC码中每个码的出现频率的直方图。从该直方图数据可以生成如图11所示的ac积分线性图。这显示了AD7874在10 kHz输入频率下非常好的积分线性性能。图中无大峰值显示良好的差分线性。所用公式的简化版本概述如下:

其中INL(i)是代码i处的积分线性度。V(fs)和V(o)是估计的满标度和偏移跃迁,V(i)是第i个代码的估计跃迁。

V(i)估计的代码转换点导出如下:

其中A是峰值信号幅度,N是直方图样本数:

微处理器接口

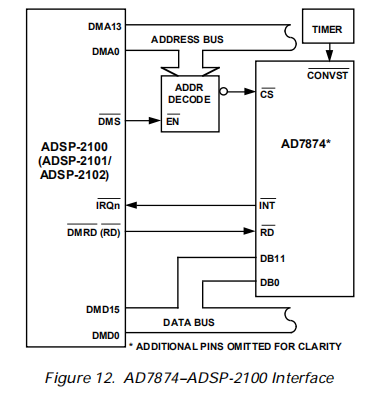

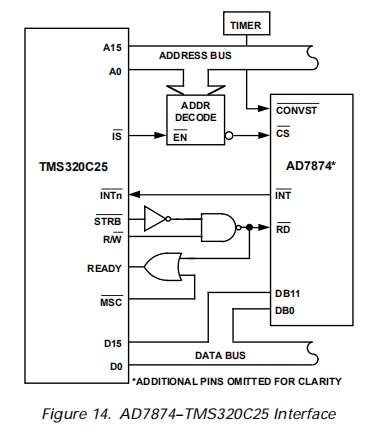

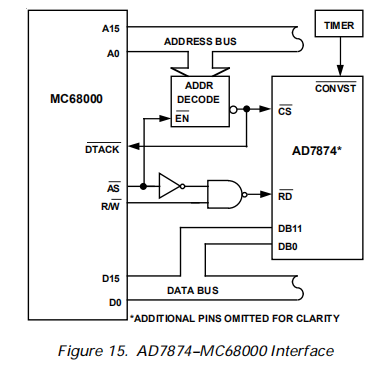

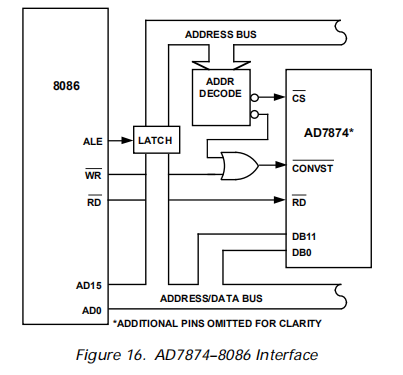

AD7874高速总线定时允许直接连接到DSP处理器以及现代16位微处理器。适当的微处理器接口如图12至16所示。

AD7874–ADSP-2100接口

图12显示了AD7874和ADSP-2100之间的接口。转换是使用一个定时器启动的,它允许非常精确地控制所有4个通道上的采样瞬间-内尔斯。当转换在所有四个通道上完成时,AD7874 INT线向ADSP2100提供中断。然后,可以使用对相同存储器地址的四次连续读取从AD7874读取四个转换结果。以下指令读取四个结果中的一个(此指令重复四次以按顺序读取所有四个结果):MR0=DM(ADC);其中MR0是ADSP-2100 MR0寄存器,ADC是AD7874地址。

AD7874–ADSP-2101/ADSP-2102接口

图12所示的接口也构成了AD7874和ADSP-2101/ADSP-2102之间接口的基础。ADSP-2101/ADSP-2102的读取线标记为RD。在这个接口中,处理器的RD脉冲宽度可以使用数据存储器等待状态控制寄存器进行编程。用于读取四个结果之一的指令如ADSP-2100所述。

AD7874–TMS32010接口

AD7874和TMS32010之间的接口如图13所示。再次使用外部定时器启动转换,当所有四个转换完成时,TMS32010中断。以下指令用于从AD7874读取转换结果:IN D,ADC;其中D是数据存储器地址,ADC是AD7874地址。

AD7874–TMS320C25接口

图14显示了AD7874和TMS320C25之间的接口。与前两个接口一样,转换是用定时器启动的,当转换序列完成时,处理器被中断。TMS320C25没有具有单独的RD输出以直接驱动AD7874 RD输入。这必须由处理器STRB和R/W输出加上一些逻辑门。RD信号与MSC信号一起被选通,以提供正确接口定时所需的读取周期中的一个等待状态。使用以下指令从AD7874读取转换结果:IN D,ADC;其中D是数据存储器地址,ADC是AD7874地址。

有些应用程序可能要求由微处理器而不是外部计时器启动转换。一种选择从地址总线解码AD7874转换器,以便写入操作开始转换。数据像以前一样在转换序列的末尾读取。图16显示了使用此方法启动转换的示例。注意,对于所有接口,在转换期间不应尝试读取操作。

AD7874–MC68000接口

AD7874和MC68000之间的接口如图15所示。与以前一样,转换是使用外部定时器。AD7874整型线可用于中断处理器,或者,软件延迟可确保在尝试读取AD7874之前已完成转换。由于其中断的性质,68000需要额外的逻辑(图15中没有显示)来允许它被正确中断。有关68000中断的更多信息,请参阅68000用户手册。

MC68000 AS和R/W输出用于生成分离AD7874的RD输入信号。CS用于驱动68000 DTACK输入,以允许处理器对AD7874执行正常的读取操作。使用以下68000指令读取转换结果:MOVE.W ADC,D0;其中D0是68000 D0寄存器,ADC是AD7874地址。

AD7874–8086接口

图16显示了AD7874和8086之间的接口微处理器。与前面的接口示例不同,微处理器启动转换。这是通过将8086 WR信号与解码地址输出(不同于AD7874 CS地址)。AD7874整型线用于在转换序列完成时中断微处理器。使用以下指令从AD7874读取数据:MOV AX,ADC;其中AX是8086累加器,ADC是AD7874地址。

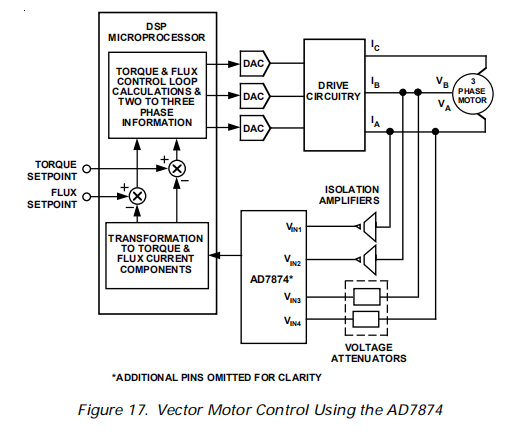

应用矢量电机控制

电动机的电流可以分成两部分:一部分产生转矩,另一部分产生磁通量。为了使电动机达到最佳性能,这两个部件应该独立控制。在控制三相电动机的传统方法中,提供给电动机的电流(或电压)和驱动器的频率是基本的控制变量。然而,转矩和磁通量都是电流(或电压)和频率的函数。这种耦合效应会降低电机的性能,因为例如,如果通过增加频率来增加转矩,磁通往往会减小。

交流电动机的矢量控制除了控制驱动和电流频率外,还包括控制相位。控制电机的相位需要转子相对于电机内旋转磁场位置的反馈信息。利用这一信息,矢量控制器数学地将三相驱动电流转换为单独的转矩和磁通分量。AD7874具有四通道同时采样能力,非常适合用于矢量马达控制应用。

使用AD7874的矢量马达控制应用程序的框图如图17所示。磁场的位置是通过确定电动机每相的电流来确定的。只需要测量两相电流,因为如果两相已知,则可以计算第三种电流。AD7874的信道1和信道2用于将该信息数字化。

同时采样对于保持两个通道之间的相对相位信息至关重要。在电机和AD7874之间使用电流感应隔离放大器、变压器或霍尔效应传感器。转子信息是通过测量电机两个输入端的电压获得的。AD7874的信道3和信道4用于获取该信息。这两个通道的相对相位同样重要。利用DSP微处理器对AD7874反馈的信息进行数学变换和控制回路计算。

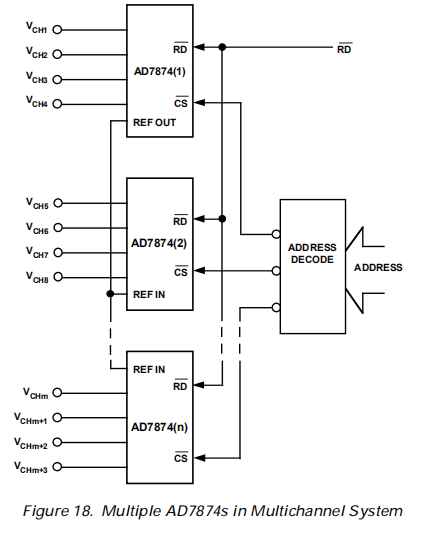

多个AD7874

图18显示了一个系统,其中可以配置多个AD7874来处理多个输入通道。这种类型的配置在声纳、雷达等应用中是常见的。AD784指定孔径延迟的最大和最小限制。这意味着用户知道在所有通道之间的采样瞬间的最大差异。这允许用户维护不同通道之间的相对相位信息。

微处理器的公共读取信号驱动所有AD7874的RD输入。每个AD7874被指定一个由地址解码器选择的唯一地址。的参考输出AD7874数字1用于驱动图18所示电路中所有其他AD7874的参考输入。一个参考输出引脚可驱动多个AD7874参考输入引脚。或者,可以使用外部或系统引用来驱动所有REF-IN输入。一个共同的参考确保所有通道之间良好的全尺寸跟踪。

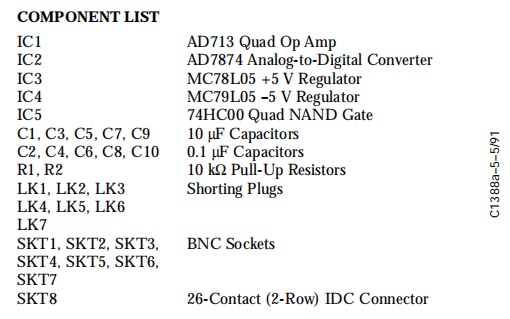

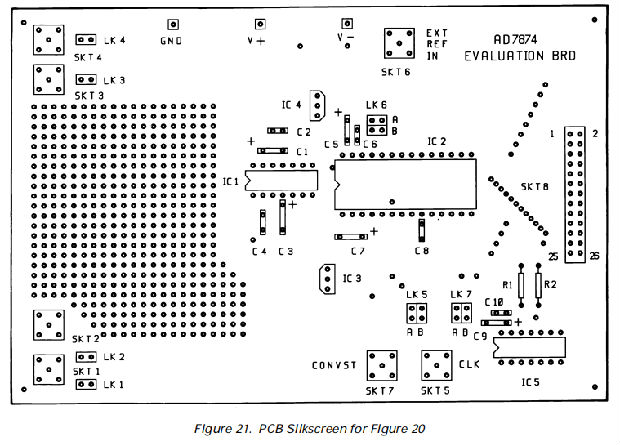

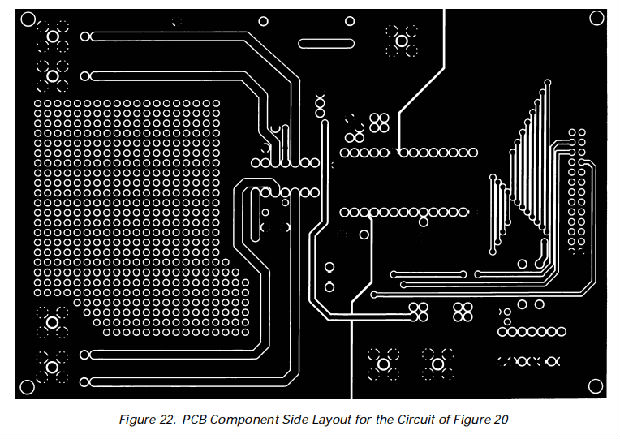

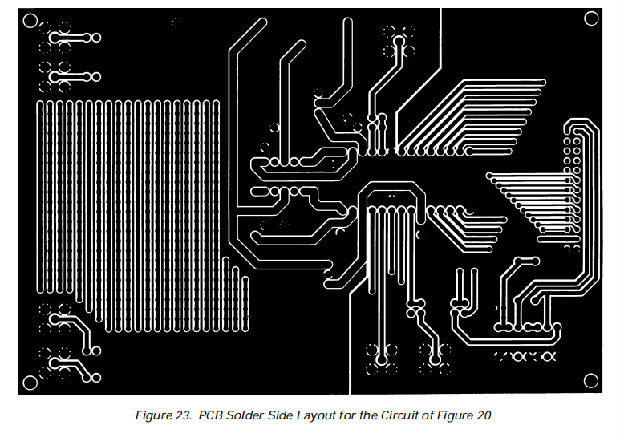

数据采集板

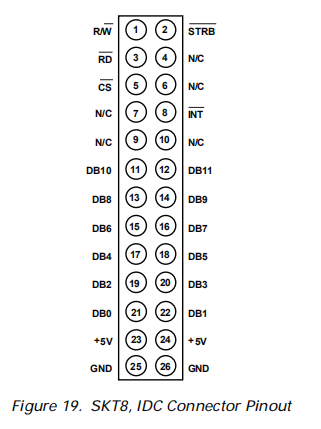

图20显示了数据采集电路中的AD7874。相应的印刷电路板(PCB)布局和丝网如图21至23所示。一个26触点的IDC连接器提供了一个微处理器到板的连接。

在PCB上的模拟输入端附近提供元件栅极,该元件栅极可用于为模拟输入通道提供抗混叠滤波器或提供信号调节电路。为了便于选择,在模拟输入端提供四个短路插头(在PCB上标记为LK1到LK4),每个输入端一个插头。如果使用特定信道的短路插头,则输入信号连接到驱动ADC的模拟输入的缓冲放大器。如果省略了短路插头,则可以使用导线连接将输入信号连接到PCB元件网格。

微处理器通过26触点IDC连接器SKT8与电路板连接,插脚如图19所示。此连接器包含AD7874的所有数据、控制和状态信号(CLK输入除外以及通过SKT5和分别为SKT7)。它还包含解码的R/W和STRB输入,这是TMS32020接口所必需的(也包括68000接口,尽管68000上的pin标签是dif-费伦特)。注意,AD7874 CS输入必须在AD7874评估板之前解码。

SKT1、SKT2、SKT3和SKT4分别为VIN1、VIN2、VIN3和VIN4提供输入。假设LK1至LK4已到位,则在将这些输入信号应用于AD7874之前,先将其馈送至四个缓冲放大器IC1。外部时钟源的使用是可选的;AD7874 CLK输入上有一个短路插头(LK5),必须连接到–5 V(对于ADC自己的内部时钟)或SKT5。SKT6和SKT7分别提供参考和CONVST输入。短路插头LK6提供使用外部参考或ADC自身内部参考的选项。

电源连接

PCB需要两个模拟电源和一个5v数字电源。模拟电源标有V+和V-两种电源的电压范围为12 V至15 V(见图23中的丝网)。通过SKT8连接到5V数字电源。AD7874所需的+5 V电源和-5 V电源由V+和V-电源上的电压调节器(IC3和IC4)产生。

短路插头选项

在使用电路板之前,必须设置七个短路插头选项。概述如下:

LK1–LK4将模拟输入连接到缓冲放大器。模拟输入也可以连接到用于信号调节的组件网格。

LK5选择AD7874内部时钟或外部时钟源。

LK6选择AD7874内部参考源或外部参考源。

LK7将AD7874 RD输入直接连接到SKT8的RD输入或解码的STRB和R/W输入。此短路插头设置取决于微处理器,例如,TMS32020和68000需要解码的RD信号。