cd4013中文资料

日期:2019-3-4CD4013是CMOS双D触发器,内部集成了两个性能相同,引脚独立(电源共用)的D触发器,采用14引脚双列直插塑料封装,是目前设计开发电子电路的一种常用器件,它的使用相当灵活方便且易掌握,受到许多电子爱好者的喜爱。

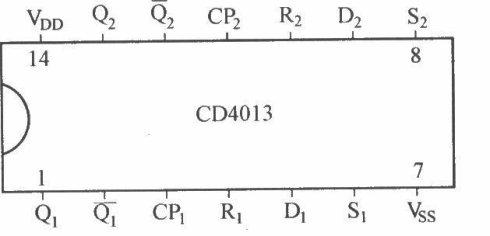

CD4013引脚图及引脚功能

1Q:逻辑正输出

1Q:逻辑负输出

1CP:时钟输入(低到高时钟触发沿有效)

1CD:异步复位输入(高电平有效)

1D:数据输入

1SD:异步置位输入(高电平有效)

VSS:系统地(0V)

2SD:异步置位输入(高电平有效)

2D:数据输入

2CD:异步复位输入(高电平有效)

2CP:时钟输入(低到高时钟触发沿有效)

2Q:逻辑负输出

2Q:逻辑正输出

VDD:系统电源

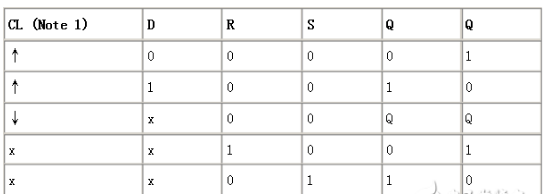

CD4013是一双D触发器,由两个相同的、相互独立的数据型触发器构成。每个触发器有独立的数据、置位、复位、时钟输入和Q及Q输出,此器件可用作移位寄存器,且通过将Q输出连接到数据输入,可用作计算器和触发器。在时钟上升沿触发时,加在D输入端的逻辑电平传送到Q输出端。置位和复位与时钟无关,而分别由置位或复位线上的高电平完成。

CD4013工作原理

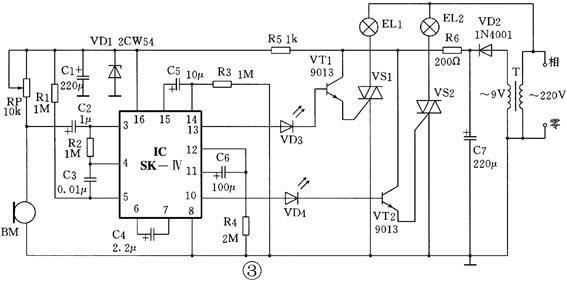

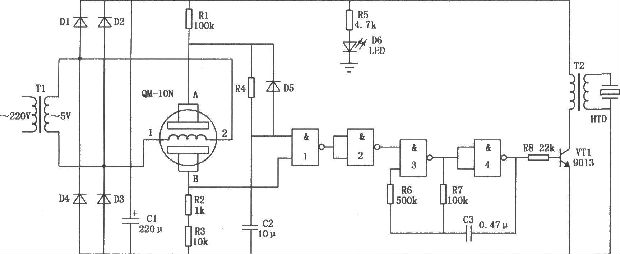

设电路初始状态均在复位状态,Q1、Q2端均为低电平。当fi信号输入时,由于输入端异或门的作用(附表是异或门逻辑功能表),其输出还受到触发器IC2的Q2端的反馈控制(非门F2是增加的一级延迟门,A点波形与Q2相同)。在第1个fi时钟脉冲的上升沿作用下,触发器IC1、IC2均翻转。由于Q2端的反馈作用使得异或门输出一个很窄的正脉冲,宽度由两级D触发器和反相门的延时决定。当第1个fi脉冲下跳时,异或门输出又立即上跳,使IC1触发器再次翻转,而IC2触发器状态不变。这样在第1个输入时钟的半个周期内促使IC1触发器的时钟脉冲端CL1有一个完整周期的输入,但在以后的一个输入时钟的作用下,由于IC2触发器的Q2端为高电平,IC1触发器的时钟输入跟随fi信号(反相或同相)。本来IC1触发器输入两个完整的输入脉冲便可输出一个完整周期的脉冲,现在由于异或门及IC2触发器Q2端的反馈控制作用,在第1个fi脉冲的作用下得到一个周期的脉冲输出,所以实现了每输入一个半时钟脉冲,在IC1触发器的Q1端取得一个完整周期的输出。