DDC112:双电流输入20位模数转换器

日期:2019-3-29DDC112是一款双输入,宽动态范围,电荷数字化模数(A / D)转换器,具有20位分辨率。低电平电流输出设备(如光电传感器)可以直接连接到其输入。当每个输入使用两个积分器时,电荷积分是连续的; 一个是数字化,另一个是整合。

DDC112的两个输入中的每一个都结合了电流 - 电压转换,连续积分,可编程满量程范围,A / D转换和数字滤波,以实现精确,宽动态范围的数字结果。除内部可编程满量程范围外,外部积分电容还允许额外的用户可设置满量程范围,最高可达1000pC。

为了提供单电源供电,内部A / D转换器使用差分输入,正输入连接到V REF。当积分电容在每个积分周期开始时复位时,电容充电至V REF。该电荷与输入电流成比例地去除。在积分周期结束时,将剩余电压与V REF进行比较。

保存最后一次转换结果的高速串行移位寄存器可以配置为允许级联多个DDC112单元,从而最大限度地减少互连。DDC112采用SO-28或TQFP-32封装,提供两种性能等级。

在DDC112模数转换器中,它提到它适用于低电平电流输出器件,如光电传感器,并可直接连接到其输入端。

操作理论

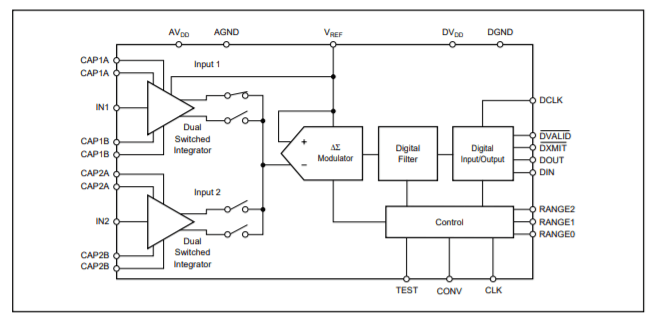

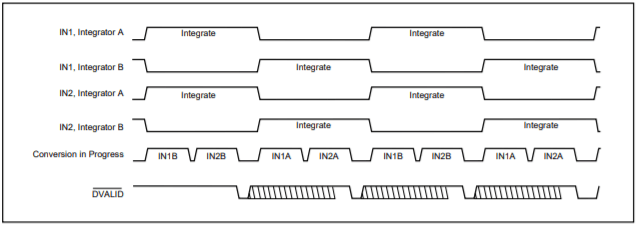

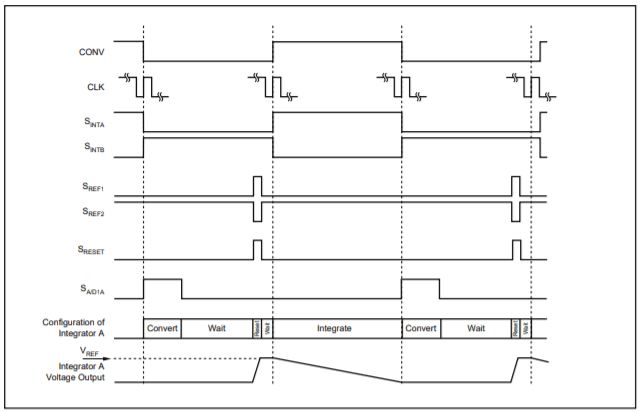

DDC112的基本操作如图1所示。设备包含两个相同的输入通道,其中每个通道执行电流-电压集成功能,然后进行多路模数(A/D)转换。每个输入都有两个积分器,以便电流与电压集成可以在时间上连续进行。四个的输出积分器被切换到一个delta sigma(?∑)转换器。通过一个四输入多路复用器。当DDC112处于连续积分模式时,积分器的输出来自两个输入端都将数字化,而另两个输入端积分器处于集成模式,如图2中的时序图。这种集成和A/D转换过程由系统时钟CLK控制。用一个10MHz系统时钟,积分器与Deltasigma转换器结合,在约220μs。来自A侧和B侧的结果每个信号输入都存储在一个串行输出移位寄存器中。当移位寄存器包含有效数据。

DDC112的数字接口提供数字结果通过一个由数据组成的同步串行接口时钟(DCLK),传输使能管脚(DXMIT),有效数据管脚

(dvalid)、串行数据输出引脚(dout)和串行数据输入引脚(DIN)。DDC112仅包含一个A/D转换器,因此转换过程在两个输入,如图2所示。整合和转换过程基本上独立于数据检索过程。因此,CLK频率和DCLK频率不必相同。仅使用DIN当多个转换器层叠并应绑定到否则。取决于色调、CLK和DCLK,它是可在100个转换器上形成菊花链。这很大在有大量转换器的情况下,简化数字输出的互连和路由需要。

图1:

图2:

设备操作

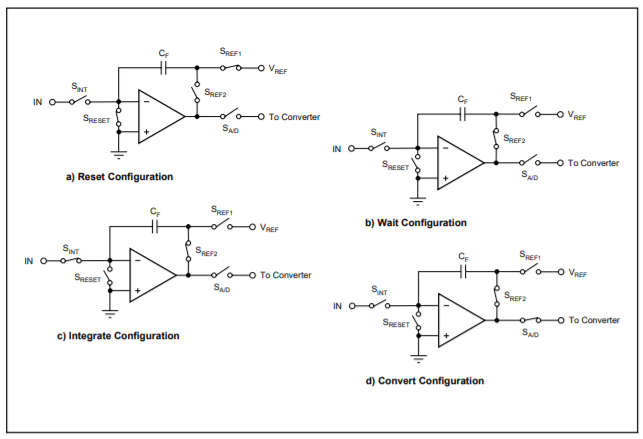

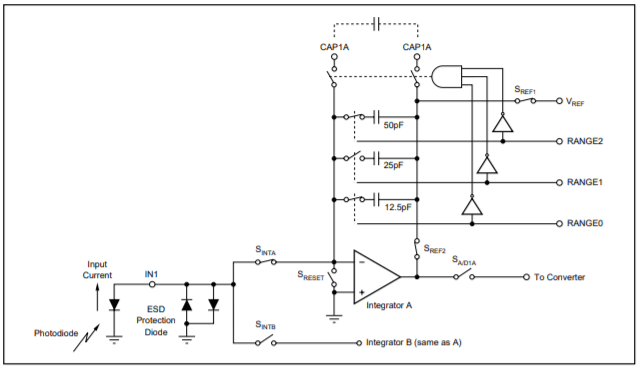

基本集成周期DDC112前端的基本拓扑结构是一种典型的模拟积分器,如图3所示。在这图中只显示输入1。此代表输入级包括一个可选择的运算放大器反馈电容网络(CF),以及几个开关实现集成周期。时间关系图3所示的所有开关如图4。图4用于概念化DDC112的积分器输入级,不应用作设计的精确定时工具。方块图DDC112积分器部分的复位、集成、转换器和等待状态如图5所示。这个内部交换网络由外部控制convert命令(conv),范围选择pins(range0-Range2)和系统时钟(CLK)。为了最好的噪音性能,conv必须与上升同步CLK的边缘。建议在±10ns内转换开关在CLK的上升边缘。积分器的非反向输入是内部的参考地面。因此,DDC112模拟

地面应尽可能干净。档位开关,与内部和外部电容器(CF)一起在反向输入和输出之间平行显示运算放大器。表一显示了每个范围的集成电容器(CF)。在A转换、开关SA/D、SINTA、SINTB、SREF1、SREF2,并设置了sreset(见图4)。在A/D转换完成时,用SREF1和重新设置(见图4和5a)。这是在重置过程中完成的时间。这样,选定的电容器充电到参考电压,Vref.一旦集成电容器充电、SREF1和SRESET被切换,因此VREF为否在放大器电路等待开始时连接更长时间积分(见图5b)。随着conv的上升边缘,Sinta关闭,开始整合通道A。将积分器阶段置于其集成模式(请参见图5C)。输入信号的电荷在积分时被收集。使放大器的电压输出减少。下降沿转换通过将输入信号从A侧切换到B侧(SINTA和SnTb)。在conv下降沿之前,侧面的信号B被A/D转换器转换并在A面正在积分的时间。有着转换,B侧开始整合输入信号。现在给出了A侧运算放大器的输出电压输入?∑A/D转换器(见图5d)。

图3:

图4:

图5: