CAT25256内部是一个EEPROM串行256-Kb

日期:2019-6-17CAT25256内部是一个EEPROM串行256-Kb SPI器件组织为32Kx8位。这具有64字节的页面写缓冲区和支持串行外设接口(SPI)协议。该设备是通过片选(CS)输入启用。另外,还需要总线

信号是时钟输入(SCK),数据输入(SI)和数据输出(SO)线。HOLD输入可用于暂停任何串行与CAT25256设备通信。该设备功能软件和硬件写保护,包括部分以及全阵列保护。片上ECC(纠错码)使设备适用用于高可靠性应用。

特征

兼容20 MHz(5 V)SPI

1.8 V至5.5 V电源电压范围

SPI模式(0,0)和(1,1)

64字节页面写入缓冲区

具有永久写保护的附加标识页

自定时写周期

硬件和软件保护

块写保护- 保护1 / 4,1 / 2或整个EEPROM阵列

低功耗CMOS技术

1,000,000个编程/擦除周期

100年数据保留

工业和扩展温度范围

8引脚SOIC,TSSOP和8焊盘UDFN封装

该器件无铅,无卤素/ BFR,RoHS

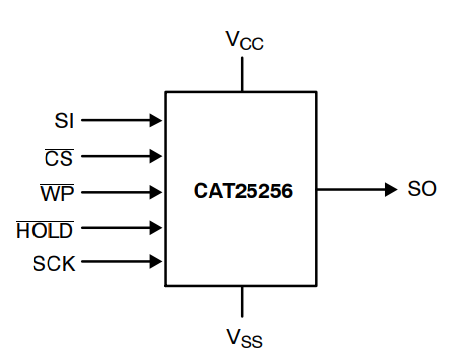

功能符号图

PIN配置图

引脚说明

SI:串行数据输入引脚接受操作码,地址和数据。在SPI模式(0,0)和(1,1)中,输入数据被锁存在SCK时钟输入的上升沿。

SO:串行数据输出引脚用于传输数据装置。在SPI模式(0,0)和(1,1)中,数据被移出在SCK时钟的下降沿。

SCK:串行时钟输入引脚接受提供的时钟由主机用于同步通信主机和CAT25256之间。

CS:芯片选择输入引脚用于启用/禁用CAT25256。当CS为高电平时,SO输出为三态(高电平)

阻抗)并且设备处于待机模式(除非内部写操作正在进行中)。每次沟通主机和CAT25256之间的会话必须以a开头从高到低的过渡,从低到高结束CS输入的转换。

WP:写保护输入引脚将允许所有写操作高电平时对设备的操作。当WP引脚是低电平和状态寄存器中的WPEN位(参见状态寄存器描述,在本数据手册的后面部分)设置为“1”,禁止写入状态寄存器。

HOLD:HOLD输入引脚用于暂停传输主机和CAT25256之间,无需重新传输整个序列在以后的时间。要暂停,HOLD必须是采取低和恢复它必须带回高,与两次转换期间SCK输入为低电平。什么时候不用暂停时,建议将HOLD输入绑定VCC,直接或通过电阻器。

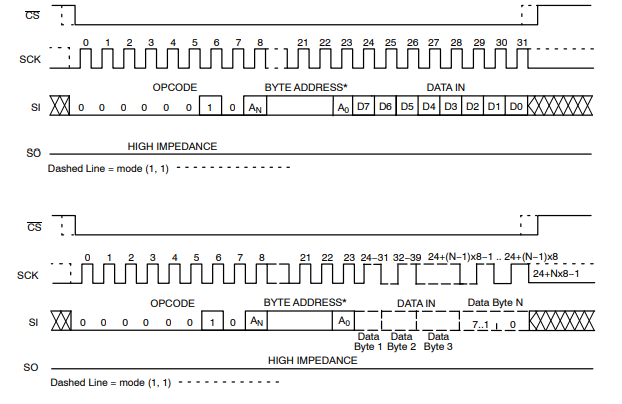

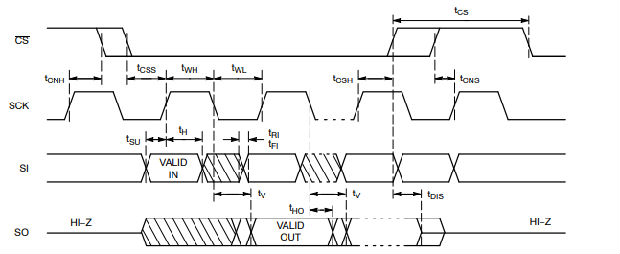

同步数据时序图

CAT25256器件支持串行外设接口(SPI)总线协议,模式(0,0)和(1,1)。该器件包含一个8位指令寄存器。指示读取存储在CAT25256中的数据是通过以下方式完成的只需提供READ命令和地址即可。除WRITE外,写入CAT25256命令,地址和数据,也需要启用用于写入的设备首先设置状态中的某些位注册,将在后面解释。在CS输入引脚上经过高电平到低电平的转换后,

CAT25256将接受六条指令中的任何一条通信协议如上图的时序。

CAT25256,新产品Rev E具有附加标识页(64字节)即可在IPL位时访问读取和写入操作从状态寄存器设置为“1”。用户也可以选择使标识页永久写入保护。

一旦设置了WEL位,用户就可以执行写操作序列,通过发送WRITE指令,一个16位地址和数据如图5所示。只有15个重要地址位用于CAT25256。第16个地址位不是,注意如下表所示。内部编程将开始在CS转换为低到高之后。在内部写入期间循环,所有命令,RDSR除外(读状态注册)将被忽略。 RDY位将指示是否内部写周期正在进行(RDY为高电平)或器件准备接受命令(RDY低)。将第一个数据字节发送到主机CAT25256可以继续发送数据,最多64个字节,按照图6所示的时序。每个数据字节后,低位地址位自动递增,而高阶地址位(页面地址)保留

不变。如果在此过程中页面结束超过,然后加载将“翻转”到的第一个字节页面,因此可能会覆盖以前加载的数据。完成写周期后,CAT25256就是自动返回写入禁用状态。虽然内部写周期正在进行中,RDSR命令会仅输出RDY(就绪)位状态(即数据输出= FFh)。写识别页面

额外的64字节标识页(IP)可以使用相同的Write命令写入用户数据用于页面写入主存储器阵列的序列必须设置状态寄存器中的IPL位(IPL = 1)在尝试之前使用WRSR指令写入IP。

地址位[A15:A6]是Do not Care和[A5:A0]位定义了字节内的字节地址鉴定页面。此外,字节地址必须指向到BP1定义的保护区外的位置,状态寄存器中的BP0位。当满满的记忆数组被写保护(BP1,BP0 = 1,1),写入不接受和不执行对IP的指令。此外,如果LIP位来自,则不接受对IP的写入状态寄存器设置为1(页面被锁定只读模式)。