TLV1548M低压10位模拟-数字转换器,带串行控制和4/8模拟输入

日期:2019-7-30转换时间10到10位分辨率ADC可编程断电模式我很抱歉。1.2.7 V dc至5.5 V dc宽范围单电源操作0 V至VCC内置模拟多路复用器,8个模拟输入通道TMS320 DSP和微处理器SPI和QSPI兼容串行接口在自检模式下,扩展采样硬件I/O时钟相位调整输入的可编程功率和转换率异步启动转换

描述

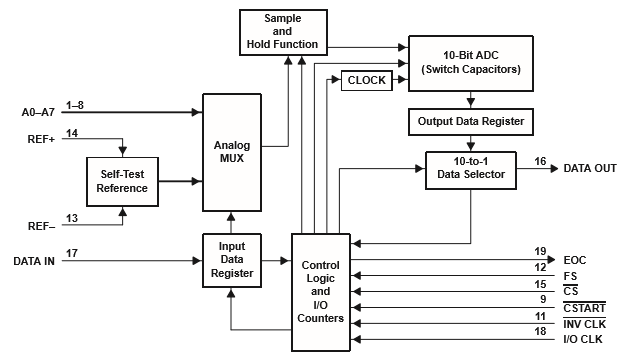

TLV1544和TLV1548是CMOS 10位开关电容逐次逼近(SAR)模数转换器。每个设备都有一个芯片选择(CS)、输入输出时钟(I/O CLK)、数据输入(数据输入)和串行数据输出(数据输出),提供主机微处理器的直接4线同步串行外围接口(SPI 63722;,QSPI 63722;)端口。当与TMS320 DSP接口时,额外的帧同步信号(fs)指示串行数据帧的开始。这些设备允许从主机高速传输数据。INV CLK输入为串行接口提供了进一步的定时灵活性。

除了一个高速转换器和多功能控制能力,该设备有一个片上11通道多路复用器,可以选择八个模拟输入中的任意一个或三个内部自检电压中的任意一个。采样保持功能是自动的,除了扩展的采样周期,其中采样周期由异步CStart的下降沿启动。在A/D转换结束时,转换结束(EOC)输出变高,表示转换完成。TLV1544和TLV1548设计用于在极低功耗的大范围电源电压下工作。通过软件编程的断电模式和转换率进一步增强了节电功能。该装置中的转换器具有不同的高阻抗参考输入,有助于比例转换、缩放和隔离模拟电路与逻辑和电源噪声。开关电容设计允许在整个工作温度范围内进行低误差转换。

说明(续)

TLV1544有四个模拟输入通道,而TLV1548有八个模拟输入通道。TLV1544C和TLV1548C的特点是在0°C到70°C的温度范围内工作。TLV1544I和TLV1548I的特点是在-40°C到85°C的全工业温度范围内工作。TLV1548M的特点是在-55°C的全军事温度范围内工作。o 125摄氏度。

功能框图

详细描述

最初,当CS高(非活动)时,数据输入和输入/输出CLK被禁用,数据输出处于高阻抗状态。当串行接口接收到CS低(激活)时,转换序列从启用I/O CLK和数据输入和从高阻抗状态中删除数据开始。然后主机向数据输入提供4位通道地址,向I/O CLK提供I/O时钟序列。在这种传输过程中,主机串行接口还接收来自数据输出的前一个转换结果。I/O CLK接收来自主机的输入序列,该序列的长度为10到16个时钟。前四个有效的I/O CLK周期使用数据上的4位输入数据加载输入数据寄存器,以选择所需的模拟通道。接下来的六个时钟周期提供对模拟输入采样的控制时间。模拟输入的采样在十个时钟的第一个有效I/O CLK序列之后保持。第十个时钟边缘也将EOC调低并开始转换。I/O时钟边缘的确切位置取决于操作模式。

串行接口

TLV1548与通用微处理器串行接口(如SPI和QSPI)和TMS320 DSP串行接口兼容。通过对CS下降沿的fs状态进行采样,生成内部锁存标志if_模式。当fs在cs下降沿高时,如果_模式设置为1(对于微处理器),当fs在cs下降沿低时,如果_模式清除为0(对于dsp)。此标志控制I/O CLK的多路复用和状态机重置功能。与微处理器接口时,fs被拉高。

I/O时钟

当可以快速输入/输出时,在大多数电压范围内,I/O CLK可高达10兆赫。对于2.7 V的电源电压范围,最大I/O CLK限制为2.8 MHz。表1列出了所有不同电源电压范围的最大I/O CLK频率。这也取决于输入源阻抗。例如,如果输入源阻抗小于1 kΩ,则可以实现高于2.39 MHz的I/O CLK速度。

表1.最大I/O CLK频率

VCC公司

最大输入电阻(最大)

源阻抗输入/输出时钟

27V 5公里

1千欧2.39兆赫

2.7伏5千

100欧2.81兆赫

45V 1千

1千欧7.18兆赫

4.5伏1千伏

100欧姆10兆赫

微处理器串行接口

当设备处于微处理器接口模式时,如果INV CLK保持高位,则来自数据输入的输入数据位在I/O CLK序列的前四个上升沿上被打卡。如果INV CLK保持在低位,则输入数据位在I/O CLK序列的前四个下降沿上打卡。前一个转换的MSB出现在cs的下降沿上的data out上。剩余的9位在I/O CLK的下9个边缘(取决于INV CLK的状态)上移出。10位数据通过数据输出传输到主机。

转换开始至少需要9.5个时钟脉冲。在第十时钟上升沿,EOC输出变低,并在转换完成后返回到高逻辑电平;然后主机可以读取结果。在第十个时钟下降沿,内部逻辑取低数据,以确保剩余的位值为零,如果I/O CLK传输超过十个时钟长。

在串行I/O CLK传输之间,CS处于非活动状态(高)。每次传输至少需要10个I/O CLK周期。CS的下降沿通过从高阻抗状态中删除数据开始序列。CS的上升沿在规定的延迟时间内将数据返回到高阻抗状态,以此结束序列。此外,CS的上升沿在设置时间内禁用I/O CLK和数据输入。直到第十个I/O CLK上升沿才开始转换。

在进行中的循环中,在指定的时间内,CS上的高到低转换将中止循环,并且设备将返回到初始状态(输出数据寄存器保留先前的转换结果)。由于输出数据可能被破坏,在转换完成之前不应将cs取低。

DSP接口

TLV1544/1548还可以通过串行端口与TMS320系列的DSP接口。模数转换器(ADC)是一个从设备,其中DSP提供fs和串行I/O CLK。发送和接收操作是并发的。fs的下降沿必须在cs下降沿之后的七个I/O CLK周期内出现。

DSP I/O周期与微处理器I/O周期的区别如下:

当与DSP接口时,输出数据MSB在fs↓后可用。剩余的输出数据在I/O CLK的上升沿发生变化。输入数据在fs↓后和inv clk高时,或在fs↓后和inv clk低时,在I/O clk的前四个下降沿上采样。当与微处理器接口时,此操作是反向的。

在FS上升沿之后,在I/O CLK上升沿开始了一个新的DSP I/O循环。当fs高时,在I/O CLK的每个下降沿上重置内部状态机。当与微处理器接口时,此操作是相反的。

当与DSP接口时,TLV1544/1548支持16时钟周期。在DSP模式下运行时,输出数据用6个尾随零填充。

输入数据位

数据输入内部连接到4位串行输入数据寄存器。输入数据选择不同的模式或选择不同的模拟输入通道。主机首先向数据字提供MSB。每个数据位在I/O CLK序列的边缘(上升或下降取决于INV CLK和FS的状态)上时钟。输入时钟可通过接地INV CLK倒转

TLV1544/1548软件编程操作模式

输入数据字节

功能选择A3–A0注释

二进制十六进制

TLV1548的模拟通道a0为TLV1544选择了00000b 0h通道0

用于TLV1548的模拟通道A1选择了0001B 1H

模拟通道A2用于TLV1548选择0010B 2H通道1用于TLV1544

用于TLV1548的模拟通道A3已选择0011B 3H

用于TLV1548的模拟通道A4选择用于TLV1544的0100B 4H通道2

用于TLV1548的模拟通道A5选择了0101B 5H

模拟通道A6用于TLV1548选择0110B 6H通道3用于TLV1544

用于TLV1548的模拟通道A7选择0111B 7H

软件掉电设置1000B 8H无转换结果(任何访问清除)

快速转换率(10微秒)设置1001B 9H无转换结果(设置为快速清除)

慢速转换率(40微秒)设置1010B Ah无转换结果(通过设置为慢速清除)自检电压(VREF–VREF–)/2选择1011B BH输出结果=200H自检电压VREF选择1100B CH输出结果=000H自检电压VREF选择1101B DH输出结果=3FFH重置rved 1110b eh无转换结果

保留1111b fh无转换结果

模拟输入和内部测试电压

11通道多路复用器根据输入数据位选择8个模拟输入和3个内部测试输入,如表3所示。输入多路复用器是一种先断后合的类型,以减少由于信道切换而产生的输入到输入噪声注入。

该装置可以在两种不同的采样模式下工作:正常采样模式(固定采样时间)和扩展采样模式(灵活采样时间)。当CStart保持在高位时,装置以正常采样模式运行。在正常采样模式下操作时,模拟输入的采样从微处理器接口模式下第四个I/O CLK脉冲的上升沿开始(在DSP接口模式下,从I/O CLK的第四个下降沿开始)。采样持续6个I/O CLK周期。在微处理器接口模式下,样本被保存在第十个I/O CLK脉冲的下降沿上。在DSP接口模式下,将采样保持在第十个I/O CLK脉冲的下降沿上,将三个测试输入应用于多路复用器,然后以与外部模拟输入相同的方式进行采样和转换。

转换器

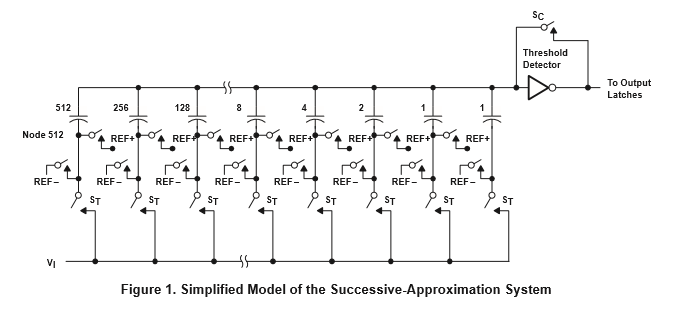

逐次近似转换系统中的CMOS阈值检测器通过检查一系列二进制加权电容器上的电荷来确定每个位的值(见图1)。在转换过程的第一阶段,模拟输入通过同时关闭SC开关和所有ST开关进行采样。此动作将所有电容器充电至输入电压。

在转换过程的下一个阶段中,所有ST和SC开关打开,阈值检测器开始通过识别每个电容器上相对于参考电压的电荷(电压)来识别位。在开关序列中,对10个电容器分别进行检查,直到识别出所有10位,然后重复电荷转换序列。在转换阶段的第一步中,阈值检测器查看第一个电容器(重量=512)。该电容器的512节点被切换到REF+电压,梯架上所有其他电容器的等效节点被切换到REF–。如果求和节点处的电压大于阈值检测器的触发点(约为VCC的一半),则输出寄存器中会有一个位0,512重量电容器会切换到REF–。如果求和节点处的电压小于阈值检测器的触发点,则在寄存器中放置一个位1,512重量电容器通过后续近似过程的剩余部分保持与ref+的连接。对256重量的电容器、128重量的电容器等重复此过程,直到所有位都计数为止。

在逐次近似过程的每一步中,初始电荷在电容器之间重新分配。转换过程依赖于电荷再分配来计算和权衡从MSB到LSB的位。

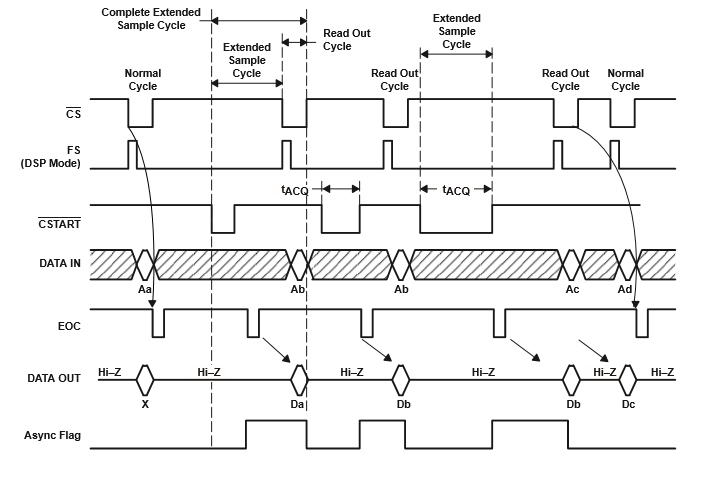

扩展采样,异步开始采样:CStart操作

扩展采样操作模式对采样保持电路的采集时间(TACQ)进行编程。这允许设备的模拟输入直接连接到广泛的输入源阻抗。扩展采样模式根据所选采样周期的持续时间消耗更高的功率。

CStart控制采样周期并开始转换。CStart的下降沿启动预设通道的采样周期。CSTART的低时间控制输入采样保持电路的采集时间。样品保存在CSTART的上升边缘。断言CStart使转换器在预设的有效MUX通道(八个通道之一)上执行新的信号采样,并丢弃准备输出的当前转换结果。只要CStart激活(阴性),采样就会继续。CStart的上升沿结束了采样周期。转换周期在CStart上升沿之后启动两个内部系统时钟。

一旦转换完成,处理器就可以启动一个正常的I/O循环来读取转换结果,并为下一个转换设置mux地址。由于内部标志asyncFlag设置为高,因此此标志设置指示循环为输出循环,因此在循环期间不执行转换。内部状态机在CS的下降沿上测试AsyncFlag。AsyncFlag在CStart的上升沿设置为高,在每个CS的上升沿重置为低。只有当AsyncFlag在CS的下降沿测试为低时,转换周期才会遵循采样周期。异步I/O周期可以通过两个连续的正常I/O周期来除去。

延长采样周期

扩展采样操作

参考电压输入

有两个参考输入用于TLV1544/TLV1548、REF+和REF–。这些电压值建立模拟输入的上限和下限,分别产生满刻度和零刻度读数。参考+参考-和模拟输入的值不应超过正电源或低于与指定绝对最大额定值一致的GND。当输入信号等于或高于参考+时,数字输出处于满刻度;当输入信号等于或低于参考-时,数字输出处于零。

可编程转换率

当不需要高速操作时,TLV1544/TLV1548提供两种转换率,以最大限度地延长电池寿命。转换速率可编程。一旦选择了转换速率,它将在同一周期内立即生效,并保持相同的速率,直到选择了其他速率。应在通电时设置转换率。断电状态的激活和停用(数字逻辑激活)对预设转换率没有影响。

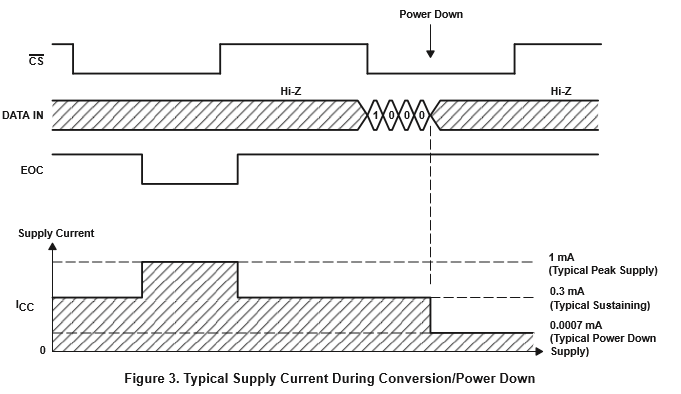

可编程断电状态

通过将8h写入数据,设备进入关机状态。在下一次活动访问期间,通过将CS拉低,恢复通电状态。在设备进入关机状态之前选择的转换速率不受关机模式的影响。断电可以实现更低的功耗。这是因为持续功率(不转换时)最大值仅为1.3 mA,备用功率最大值仅为1微安。(通过求平均值,当转换吞吐量较低时,功耗可以大大低于1 mA峰值。)

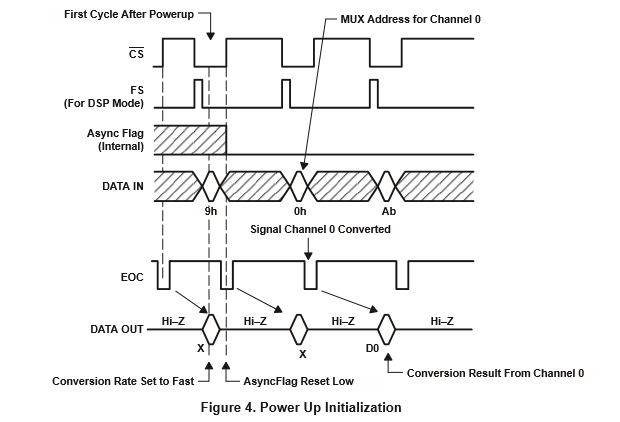

通电和初始化

通电后,如果在DSP模式下运行,则CS和FS必须从高到低开始I/O循环。EOC初始值高,输入数据寄存器设置为所有零。输出数据寄存器的内容是随机的,第一个转换结果应该被忽略。对于操作期间的初始化,CS被设为高电平,并返回低电平,以开始下一个I/O循环。设备从关机状态返回后的第一次转换可能无效,应忽略不计。

当设备首次通电时,必须对转换率进行编程,并且内部异步标志必须降低一次。然后,同一循环的CS上升沿将异步标志设为低。

通电初始化

输入时钟反转–INV CLK

输入数据寄存器使用I/O CLK作为采样时钟的源。这个时钟可以倒转以提供更多的设置时间。inv clk可以反转时钟。当INV CLK接地时,输入数据寄存器的输入时钟反转。这允许输入数据设置时间有一个额外的半I/O CLK周期。这对一些串行接口很有用。当输入采样时钟反转时,输出数据在对输入数据进行采样的同时发生变化。