ADS8341是一款4通道,16位采样模拟 - 数字(A / D)转换器

日期:2019-8-15ADS8341是一款4通道,16位采样模拟 - 数字(A / D)转换器,具有同步串行接口。在100kHz吞吐量下,典型功耗为8mW速率和+ 5V电源。参考电压(VREF)可以是在500mV和VCC之间变化,提供相应的输入电压范围为0V至VREF。该设备包括一个关闭模式,将功耗降低到低于15μW。ADS8341的工作电压低至2.7V。低功耗,高速度和板载多路复用器ADS8341非常适合电池供电系统,如个人数字助理,便携式多通道数据记录器和测量设备。 串行接口也是为远程数据采集提供低成本隔离。该ADS8341采用SSOP-16封装,工作在-40°C至+ 85°C温度范围。

特征

PIN码与ADS7841的PIN码

单电源:2.7V至5V

4通道单端或

2通道差分输入

最高100kHz转换速率

86dB SINAD

串行接口

SSOP-16包装

应用

数据采集

测试和测量

工业过程控制

个人数字助理

电池供电系统

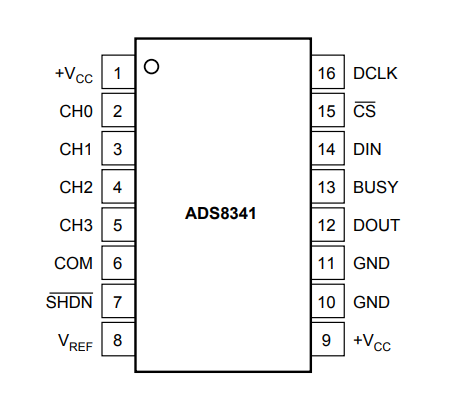

PIN配置图

PIN名称说明

1 + VCC电源,2.7V至5V

2 CH0模拟输入通道0

3 CH1模拟输入通道1

4 CH2模拟输入通道2

5 CH3模拟输入通道3

6 COM模拟输入的接地参考。在单端模式下设置零代码电压。将此引脚连接到地或参考地点。

7 SHDN关机。当为低电平时,器件进入极低功耗关断模式。

8 VREF参考电压输入。有关范围,请参见电气特性表。

9 + VCC电源,2.7V至5V

10 GND地。连接到模拟地

11 GND地。连接到模拟地。

12 DOUT串行数据输出。数据在DCLK的下降沿移位。当CS为高电平时,此输出为高阻抗。

13 BUSY忙输出。当CS为高电平时,此输出为高阻抗。

14 DIN串行数据输入。如果CS为低电平,则数据在DCLK的上升沿锁存。

15 CS片选输入。控制转换时序并启用串行输入/输出寄存器。

16个DCLK外部时钟输入。该时钟运行SAR转换过程并同步串行数据I / O.最大输入时钟频率

等于2.4MHz,实现100kHz采样率。

运作理论

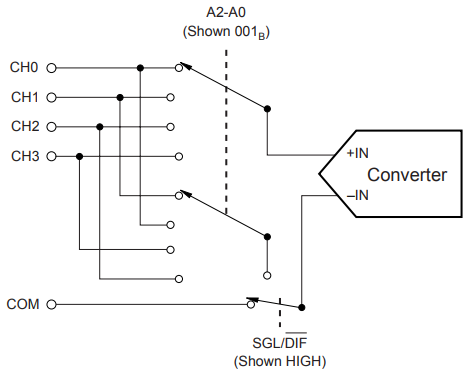

ADS8341是一款经典的逐次逼近型寄存器(SAR)A / D转换器。该架构基于电容再分配,其本质上包括采样和保持功能。转换器制造在0.6μmCMOS工艺。ADS8341的基本操作如下图所示。该设备需要外部参考和外部参考时钟。它采用2.7V至5.25V的单电源供电。外部参考可以是500mV之间的任何电压和+ VCC。参考电压的值直接设定转换器的输入范围。平均参输入电流取决于转换率ADS8341。转换器的模拟输入是差分输入通过四通道多路复用器提供。 输入可以是提供COM引脚上的电压(其中通常使用四个中的两个来区分或差分输入通道(CH0 - CH3)。具体配置是可通过数字接口选择。

模拟输入

图2显示了输入多路复用器的框图ADS8341。转换器的差分输入是从参考COM的四个输入之一派生而来四个输入中的一个或两个。该控制位通过DIN引脚串行提供,请参见本数据手册的数字接口部分了解更多详情。当转换器进入保持模式时,电压+ IN和-IN输入之间的差异,如图所示下图是在内部电容阵列上捕获的。该-IN输入上的电压限制在-0.2V和-0.2V之间

1.25V,允许输入拒绝小信号+ IN和-IN输入共有。 + IN输入有范围为-0.2V至+ VCC +0.2V。

参考输入

外部参考设置模拟输入范围。该ADS8341的工作范围为500mV至+ VCC。请记住,模拟输入是

+ IN输入和-IN输入之间的差异,请参阅上图.例如,在单端模式下,为1.25V参考,COM引脚接地,选择输入通道(CH0-CH3)将正确数字化信号范围为0V至1.25V。如果COM引脚连接到0.5V,所选通道的输入范围为0.5V至1.75V。关于参考,有几个关键项目输入及其宽电压范围。作为参考电压降低,每个数字输出的模拟电压权重代码也减少了。这通常被称为LSB

(最低有效位)大小并且等于参考电压除以65,536。固有的任何偏移或增益误差在LSB方面,A / D转换器中的增加似乎会增加尺寸,随着参考电压的降低。例如,如果给定转换器的偏移量为2LSB,带2.5V基准电压,那么它通常是10LSB,带有0.5V参考电压。在每种情况下,器件的实际偏移量是相同的,76μV。同样,数字化输出的噪声或不确定性将会随着LSB尺寸的减小而增加。参考电压为500mV,LSB尺寸为7.6μV。这个级别低于设备的内部噪音。结果,数字输出代码将不稳定,并且在a的平均值附近变化LSB的数量。输出代码的分配将是通过简单的平均可以降低高斯噪声和噪声连续转换结果或应用数字滤波器。使用较低的参考电压时,应注意提供干净的布局,包括足够的旁路,干净(低噪声,低纹波)电源,低噪声参考,和低噪声输入信号。因为LSB尺寸较小,转换器对附近的数字也会更敏感

信号和电磁干扰。进入VREF输入的电压不是直接缓冲的驱动电容数模转换器(CDAC)

ADS8341的一部分。通常,输入电流为13μA,2.5V基准电压。此值将因此而异微安取决于转换结果。该参考电流直接随两次转换而减小速率和参考电压。作为当前的参考在每个位决定上绘制,为转换器提供更多时钟在给定的转换期内快速不会减少参考电流的总电流消耗。

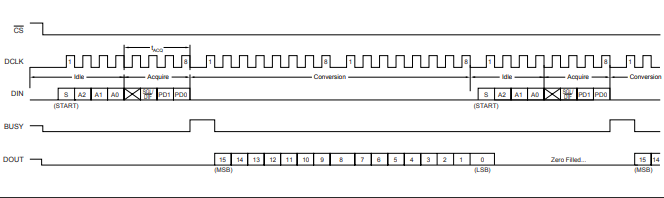

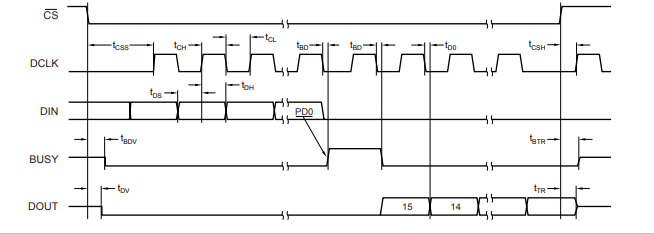

数字接口

下图显示了ADS8341的典型操作数字接口。这个图假定了源的数字信号是微控制器或数字信号处理器带有基本的串行接口(注意数字输入是过压容限高达5.5V,无论+ VCC如何)。每

处理器和转换器之间的通信由八个时钟周期组成。一次完整的转换即可通过三个串行通信来完成DCLK输入上共有24个时钟周期。前八个周期用于提供控制字节通过DIN引脚。转换器有足够的信息时关于以下转换来设置输入多路复用器个时钟周期,控制字节完成和转换器进入转换模式。此时,输入采样保持进入保持模式。接下来的16时钟周期完成实际的模数转换。控制字节下图中还显示了该位置和顺序控制字节内的控制位。表III和IV给出有关这些位的详细信息。第一位,'S'bit,必须始终为HIGH并指示开始控制字节。 ADS8341将忽略DIN上的输入引脚直到检测到起始位。

时钟模式

ADS8341可与外部串行时钟或内部时钟执行逐次逼近转换。在两种时钟模式下,外部时钟都会移位数据进出设备。选择内部时钟模式当PD1为高电平且PD0为低电平时。如果用户决定从一种时钟模式切换到另外,在此之前需要额外的转换周期ADS8341可以切换到新模式。额外的周期是需要,因为PD0和PD1控制位需要在更改时钟模式之前写入ADS8341。首次向ADS8341供电时,用户必须使用设置所需的时钟模式。可以通过编写PD1来设置对于内部时钟模式,PD0 = 0,对于外部时钟模式,PD0 = 1,PD0 = 1。 在启用所需的时钟模式后,才应将ADS8341设置为

转换之间的掉电(即,PD1 = PD0 = 0)。ADS8341保持之前的时钟模式进入省电模式。

外部时钟模式

在外部时钟模式下,外部时钟不仅会移位数据输入和输出ADS8341,它还控制A / D.转换步骤。BUSY将在一个时钟周期内变为高电平在控制字节的最后一位移入之后。进行逐次逼近位决定并出现在DOUT在接下来的16个DCLK下降沿中的每一个(参见上图)。下图显示了外部时钟模式下的BUSY时序。由于串行时钟的一个时钟周期被消耗忙碌起来(在MSB做出决定的时候),必须给出16个额外的时钟来输出所有16位数据的;因此,一次转换至少需要25个时钟循环以完全读取数据。由于大多数微处理器在8位传输中进行通信,这意味着额外的

必须进行转移以捕获LSB。处理此要求有两种方法。一个是如上图所示,其中下一个控件的开头字节在LSB被输出的同时出现ADS8341。此方法允许最大吞吐量和每次转换24个时钟周期。

另一种方法如下图2所示,它使用32个时钟每次转换的周期; 最后七个时钟周期在DOUT线上移出零。 BUSY和DOUT进入CS变高时的高阻态; 在下一个CS之后下降沿,BUSY将变为低电平。

内部时钟模式

在内部时钟模式下,ADS8341会自行生成内部转换时钟。这减轻了微处理器必须产生SAR转换时钟和允许在处理器处读回转换结果方便,任何时钟频率从0MHz到2.0MHz。BUSY在转换开始时变为低电平然后返回转换完成后为高电平。在转换期间,BUSY将保持低电平最多8μs。也,在转换期间,DCLK应保持低电平以实现最佳的噪音性能。转换结果已存储

在内部登记册;数据可能会被淘汰出局转换完成后随时注册。如果在转换后BUSY变为低电平时CS为低电平,则外部串行时钟的下一个下降沿将变为低电平在DOUT线上写出MSB。剩下的比特(D14-D0)将在每个连续的时钟周期内输出跟随MSB。当BUSY变为低电平时CS为高电平

然后DOUT线将保持三态,直到CS进入LOW,如下图所示.CS不需要保留转换开始后为低。请注意,BUSY不是CS在内部时钟模式下变为高电平时为三态。数据可以按时钟速率移入和移出ADS8341超过2.4MHz,前提是最小收购时间tACQ,保持在1.7μs以上。