OPAx625高带宽、高精度、低THD+N、16位和18位模数转换器(ADC)驱动器—OPA625, OPA2625

日期:2020-10-13特征

•高驱动模式:

–千兆瓦(G=100):120兆赫

–转换速率:115 V/μs

–4-V步进16位稳定:280 ns

–低压噪声:10 kHz时为2.5 nV/√Hz

–低输出阻抗:1 MHz时为1Ω

–偏移电压:±100μV(最大)

–偏移电压漂移:±3μV/oC(最大值)

–低静态电流:2 mA(典型值)

•低功耗模式:

–千兆瓦:1兆赫

–低静态电流:270μA(典型值)

•电源可扩展功能:

–从低功耗到高驱动的超快转换模式:170 ns

•高交流和直流精度:

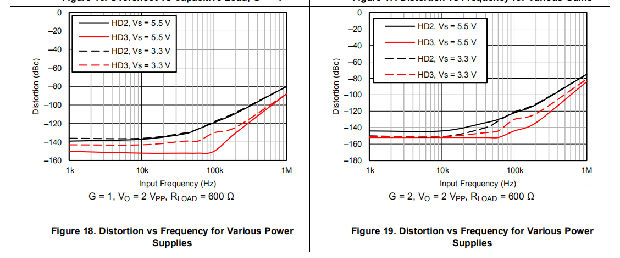

–低失真:100 kHz时,HD2为-122 dBc,HD3为-140 dBc

–输入共模范围包括负轨

–轨间输出

–宽温度范围:完全规定为-40°C至+125°C

应用

•精密SAR ADC驱动器

•精密参考电压缓冲器

•可编程逻辑控制器

•测试和测量设备

•电力敏感数据采集系统

说明

OPAx625系列运算放大器是出色的16位和18位SAR ADC驱动器,具有高精度、低THD和噪声,允许独特的功率可扩展解决方案。这一系列设备的特点和规定的16位稳定时间为280纳秒,使真正的16位有效位数(ENOB)成为可能。除了仅100μV偏置电压的高直流精度、120MHz的宽增益带宽积、2.5nV/√Hz的低宽带噪声外,该系列还优化用于驱动高吞吐量、高分辨率的SAR ADC,如SAR ADC的ADS88xx系列。

OPAx625具有两种工作模式:高驱动和低功耗。在创新的低功耗模式下,OPAx625跟踪输入信号,允许OPAx625在170 ns内以16位ENOB从低功耗模式过渡到高驱动模式。

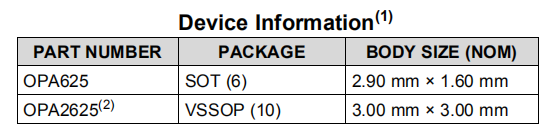

OPAx625系列有6针SOT和10针VSSOP封装,并指定在-40°C至+125°C的温度下工作。

SAR ADC驱动程序

(1)、有关所有可用的软件包,请参阅数据表末尾的订购附录。

(2)、OPA2625是产品预览版。

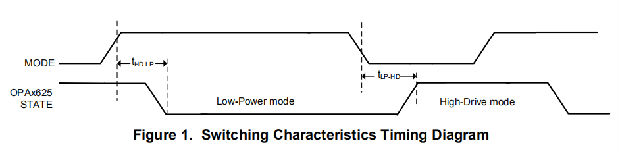

开关特性

在TA=25°C时,(V+)=5V,(V-)=0V,模式引脚连接到V引脚,G=1,VCOM=VO=2.5V,CLOAD=20pF,RLOAD=1KΩ,连接到2.5V(除非另有说明)。

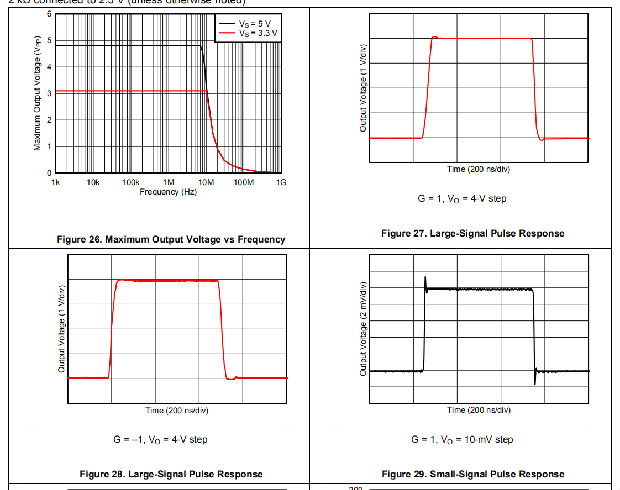

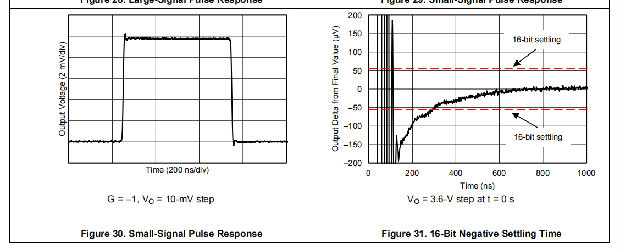

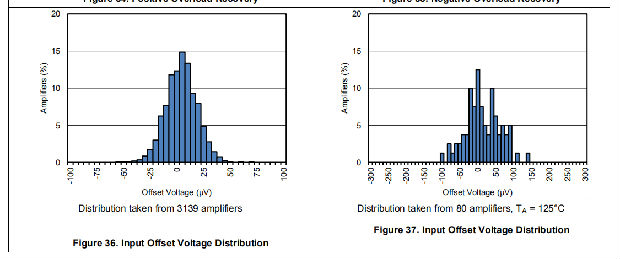

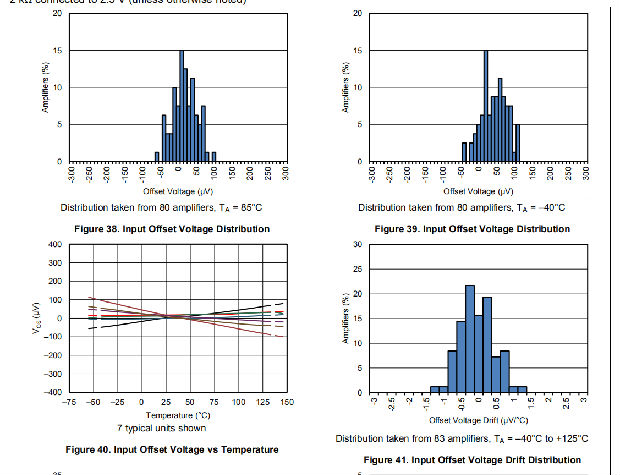

典型特征

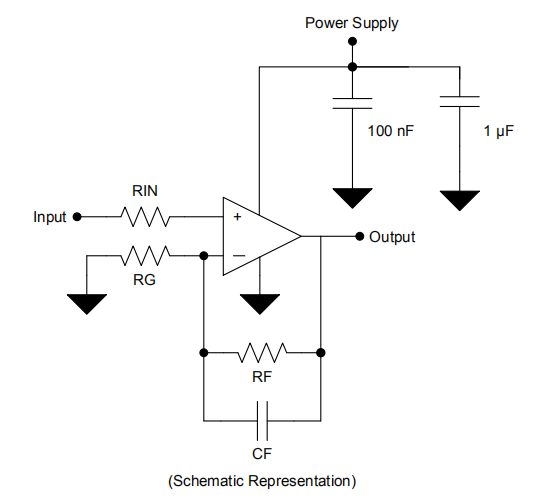

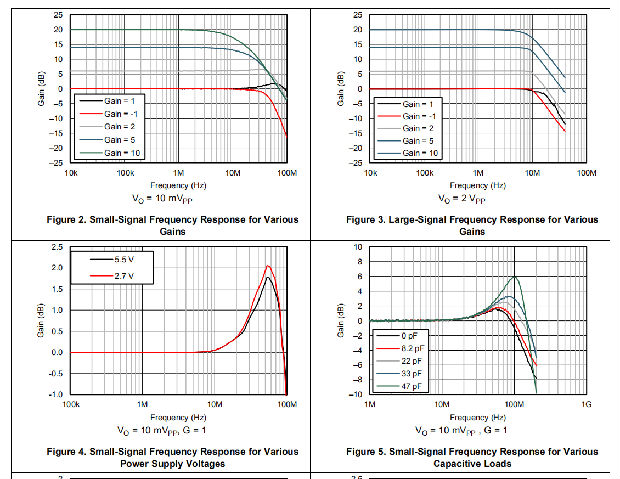

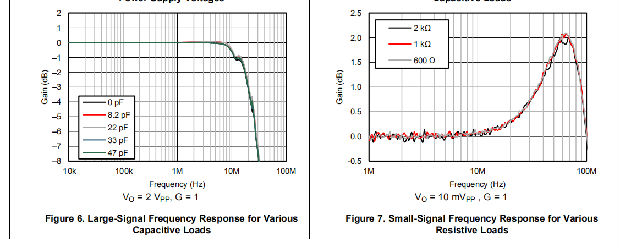

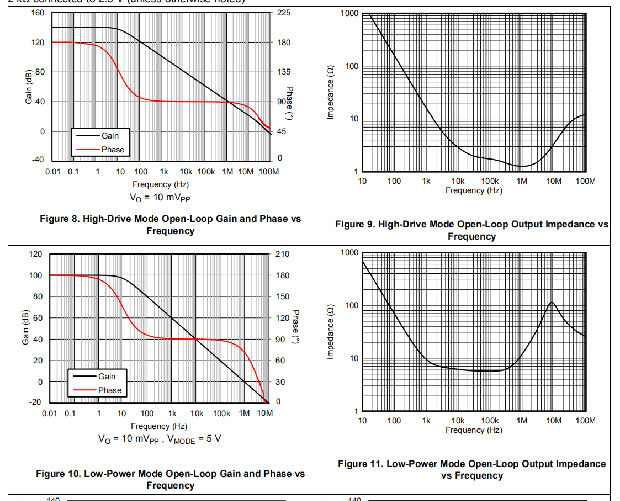

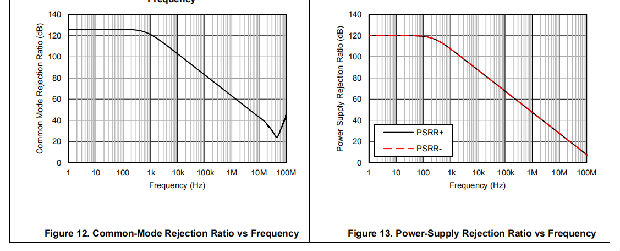

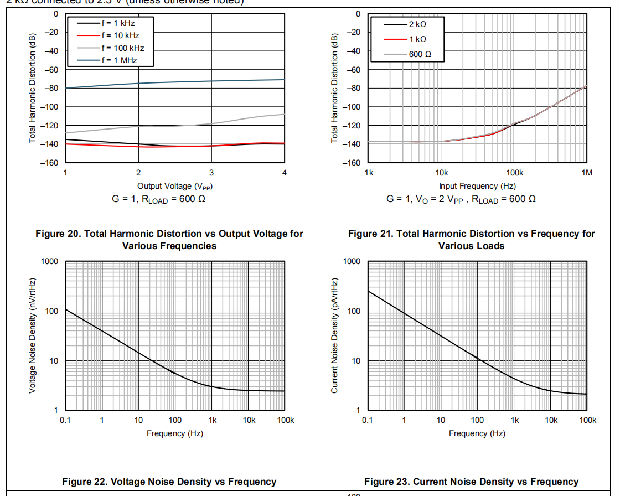

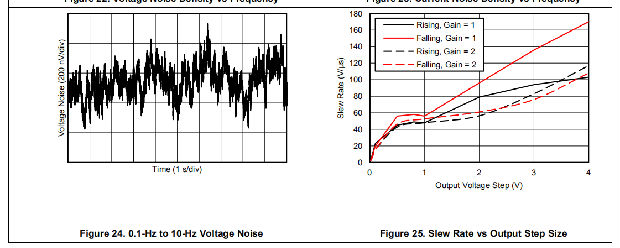

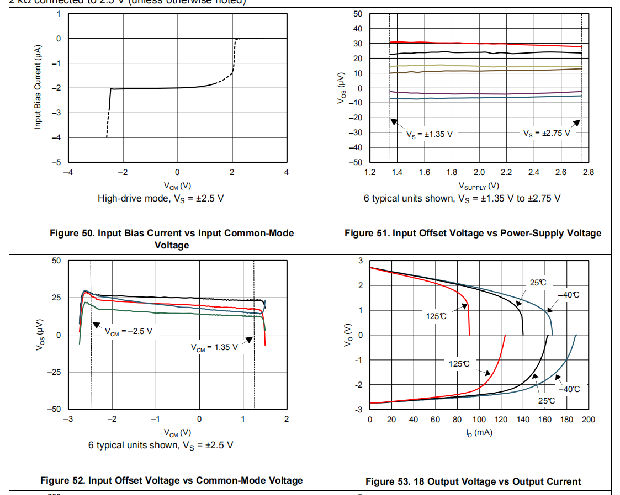

在TA=25°C,V+=5 V,V–=0 V,模式=V-,VCOM=VO=2.5 V,G=2,RF=1 kΩ,CF=2.7 pF,CLOAD=20 pF,RLOAD=2 kΩ,连接到2.5 V(除非另有说明)。

参数测量信息

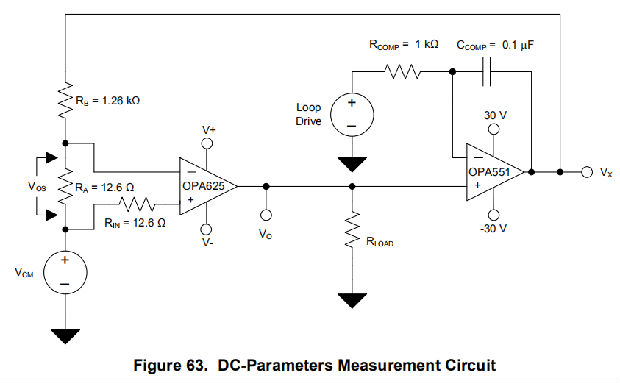

直流参数测量

图63所示电路用于测量OPAx625的直流输入偏移相关参数。该电路可以测量输入失调电压、电源抑制比、共模抑制比和开环增益。基本测试程序要求将输入(电源电压VS和共模电压VCM)设置为所需值。通过调整VO的测量值来驱动环路。配置所有输入后,在VX测量点测量输入偏移。将测量结果除以101,计算输入偏移电压。改变不同输入端的电压会改变输入偏移电压。输入参数可根据式1至式5所示的关系进行测量。

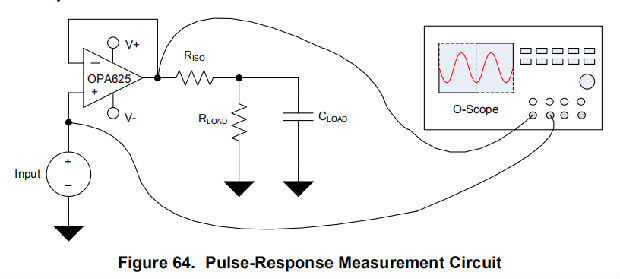

瞬态参数测量

图64所示电路用于测量OPA625的瞬态响应。配置V+,V–,RISO、RLOAD和CLOAD。监控示波器或其他信号分析仪上的输入和输出电压。使用该电路测量大信号和小信号瞬态响应、转换率、超调量和容性负载稳定性。

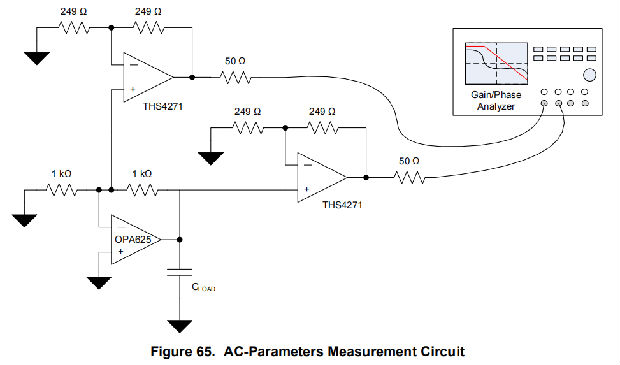

交流参数测量

图65所示电路用于测量OPA625的交流参数。根据需要配置V+、V-和CLOAD。THS4271用于缓冲OPA625的输入和输出,以防止增益相位分析仪加载。监控增益相位分析仪上的输入和输出电压。使用该电路测量增益带宽积,以及开环增益对频率对电容性负载的影响。

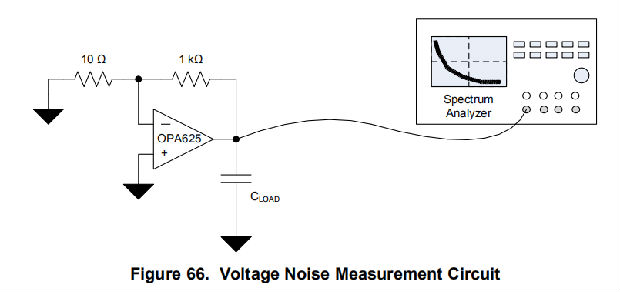

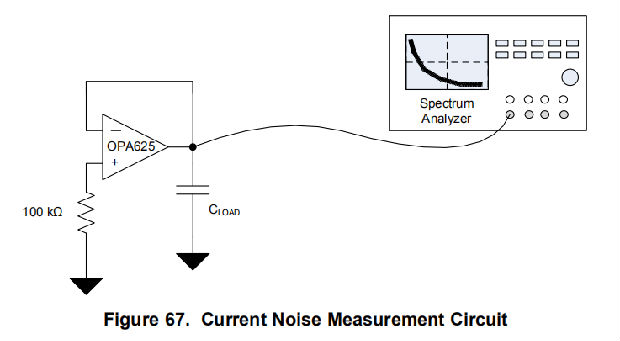

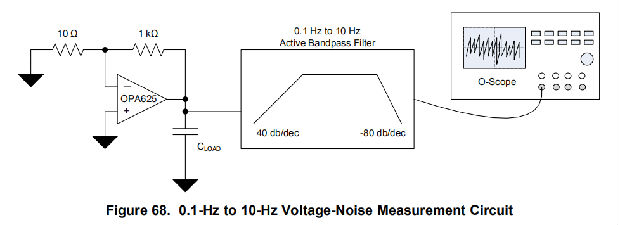

噪声参数测量

图66所示电路用于测量OPA625的电压噪声。根据需要配置V+、V-和CLOAD。

图67所示电路用于测量OPAx625的电流噪声。根据需要配置V+、V-和CLOAD。

图68所示电路用于测量OPAx625 0.1-Hz至10 Hz电压噪声。根据需要配置V+、V-和CLOAD。

详细说明

概述

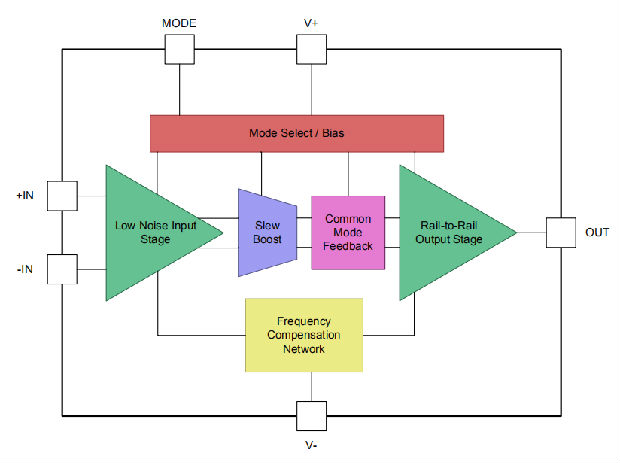

OPA625是一种快速稳定、高转换率、高带宽、电压反馈运算放大器。低偏移和低偏移漂移结合了优越的动态性能和极低的输出阻抗,从而产生了一个适用于驱动16位SAR adc的放大器,并在工业应用中缓冲精确的基准电压。OPAx625由低噪声输入级、旋转升压级和轨道环行输出级组成。模式偏差选择功能允许OPA625配置在高驱动模式和低功率模式。在ADC信号采集期间,当驱动SAR ADC时使用高驱动模式。OPAx625也可以在低功耗模式下配置,而SAR ADC正在转换采集的信号,从而节省了整个系统的功率。为了促进从低功耗模式到高驱动模式的快速转换,OPAx625在低功耗模式下不会完全关闭;相反,该设备仍然是一个具有较低带宽(1 MHz)和宽松的直流规格的有源放大器。

功能框图

特性描述

SAR ADC驱动器

OPAx625设计用于以高达1 MSPS的采样率驱动精度(16位和18位)SAR ADC。低输出阻抗、低THD、低噪声和快速稳定时间的组合使OPAx625成为驱动SAR ADC输入和ADC参考输入的理想选择。内部转换升压电路增加了作为输入信号量的函数的转换率,导致在280ns内从4v阶跃输入稳定到16位电平。低输出阻抗(1兆赫时为1Ω)确保电容性负载稳定性,同时实现最小的过冲。

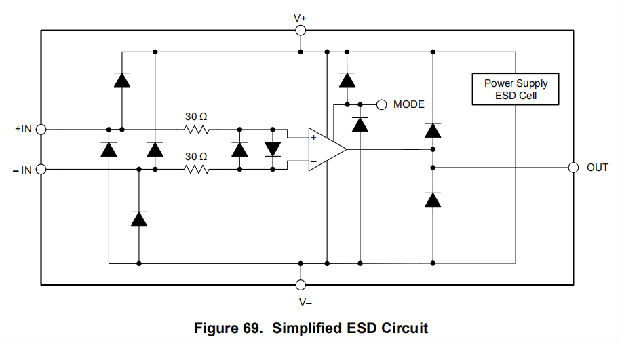

电气过应力

设计者经常会问运算放大器承受电过应力(EOS)的能力。这些问题往往集中在设备输入上,但可能涉及电源电压引脚,甚至输出引脚。每一种不同的引脚功能都具有由特定半导体制造工艺和连接到引脚的特定电路的电压击穿特性决定的电应力极限。此外,内部静电放电(ESD)保护内置在这些电路中,以防止在产品装配之前和过程中发生意外的ESD事件。对这种基本的ESD电路及其与电气过应力事件的相关性有很好的理解。关于OPA625中包含的ESD电路的图示,请参见图69。ESD保护电路包括几个电流控制二极管,这些二极管从输入和输出引脚连接,并返回内部电源线,二极管在吸收装置或电源ESD单元处汇合,后者位于运算放大器内部。该保护电路旨在在正常电路操作期间保持非活动状态。

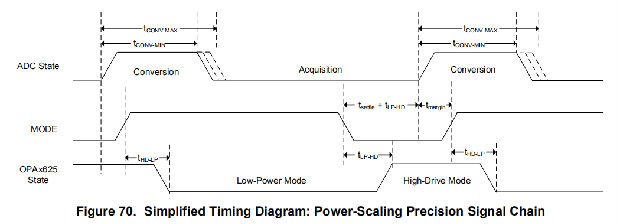

设备功能模式

OPAx625有两种功能模式:高驱动和低功耗。在低功耗模式下,OPAx625的静态电流降低到270μA(典型值),从而显著降低带宽、更高噪声和更低的输出电流驱动。OPAx625在170 ns内从低功耗模式过渡到高驱动模式。

高驱动模式

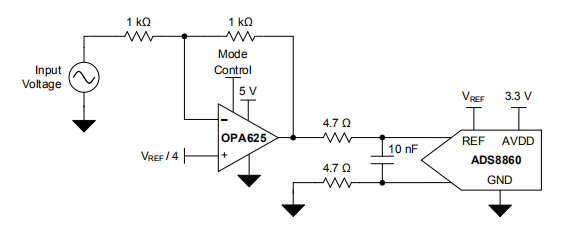

通过对模式引脚应用低逻辑电平,将OPAx625置于高驱动模式。模式引脚可以由系统控制器的通用输入/输出(GPIO)驱动,也可以由离散逻辑门驱动,或者直接连接到V引脚。不要让模式引脚浮动。当从微控制器GPIO驱动模式引脚时,确保GPIO没有处于高阻抗状态。将GPIO置于高阻抗状态会导致模式引脚基本上浮动,不建议这样做。驱动模式引脚的电压不要低于V引脚的电压;有关驱动模式引脚的允许电压,请参阅绝对最大额定值。使用模式引脚强制OPA625进入高驱动模式或低功率模式。OPAx625具有120MHz的增益带宽,2.5-nV/√Hz输入参考噪声,在高驱动模式下仅消耗2ma的静态电流。此外,OPA625还具有100μV(最大)的偏移电压和1μV/°C(典型值)的偏移电压漂移。这种高精度、高速度和低噪声的组合使得该设备适合用作高精度、高吞吐量的SAR ADC(如SAR ADC的ADS88xx系列)的输入驱动器,如图72所示。

在高驱动模式下,OPAx625完全被指定为宽带、低噪声、低失真的精密放大器。在转换周期开始之前的信号采集期间,当驱动SAR ADC的输入时,高驱动模式是OPAx625的主要工作模式。在采集周期结束之前和转换周期开始之前,将OPA625置于highdrive模式,可使OPA625在转换前设置为最终值。当ADC正在转换输入信号,因此不再采集信号时,将OPA625置于低功耗模式以降低系统功率。使用低功耗模式允许OPAx625功耗直接随采样率缩放。

OPAx625的独特之处在于,模式之间的切换发生在170纳秒(典型值)。这种快速切换是由OPAx625的体系结构在低功耗模式下实现的;有关更多信息,请参阅低功耗模式部分。

低功率模式

通过在模式引脚上应用高逻辑电平来设置OPAx625低功耗模式。模式管脚可以由系统控制器的GPIO驱动,也可以从离散逻辑门驱动,也可以直接连接到V+管脚。不要让模式引脚浮动。当从微控制器GPIO驱动模式引脚时,确保GPIO没有处于高阻抗状态。将GPIO置于高阻抗状态会导致模式引脚基本上浮动,不建议这样做。不要让模式引脚电压超过V+引脚的电压;请参阅驱动模式引脚的允许电压的绝对最大额定值。

在低功耗模式下,OPAx625完全被指定为通用运算放大器。可以控制模式信号,以便在ADC进入采集阶段之前,OPAx625被置于高驱动模式。此配置确保在采集周期完成之前,抗混叠滤波器电容器上的电压稳定到所需的精度。以这种方式运行时,OPAx625消耗的功率与系统的吞吐量成比例。此功能在功率关键型应用程序和可变吞吐量数据采集系统中非常有用。

OPAx625的独特之处在于,模式之间的切换发生在170纳秒(典型值)。这种快速切换是由OPAx625的结构在低功耗模式下实现的。大多数放大器在断电或关机模式下消耗的功率非常小,但也不是以线性方式工作。例如,一个典型放大器的输出,当被禁用时,可以被置于高阻抗状态,从而无法驱动任何负载。从关机状态切换到线性状态需要将内部电容和偏压点充电到线性工作范围内的水平。通常,此开关可能需要几微秒或更长时间。这个问题用OPAx625解决了。OPAx625在低功耗模式下作为线性运算放大器工作,输出跟踪输入信号,但带宽较低,偏移和噪声稍高。从低功率模式切换到高驱动模式并稳定到16位电平在170纳秒(典型值)内发生,这是因为在每个模式的持续时间内以线性方式保持操作。此配置允许动态功率扩展,同时仍保持高吞吐量。

应用与实施

注意:以下应用章节中的信息不是TI组件规范的一部分,TI不保证其准确性或完整性。TI的客户负责确定组件的适用性。客户应验证和测试其设计实现,以确认系统功能。

申请信息

OPAx625是一款高精度、高速、电压反馈运算放大器。快速稳定到16位电平,低THD和低噪声使OPA625适合于驱动SAR ADC输入和缓冲精密电压参考。OPA625的电源电压范围从2.7伏到5.5伏,工作温度从-40摄氏度到+125摄氏度,适用于各种高速工业应用。以下各节显示OPAx625的应用程序信息。为了简单起见,电源去耦电容器不在这些图中显示。

典型应用

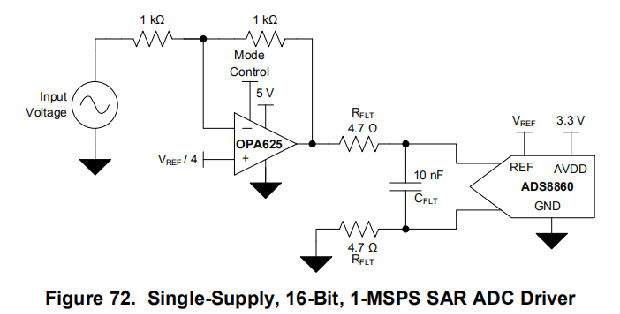

单电源,16位,1-MSPS SAR ADC驱动器

设计要求

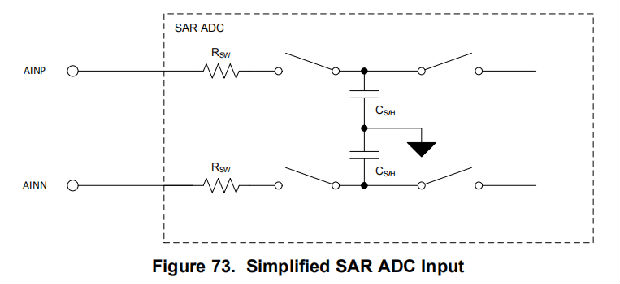

SAR adc,如ADS8860,在数据转换器输入端使用采样电容器。在信号采集阶段,这些采样电容通过一组开关连接到ADC模拟输入端子AINP和AINN。采集周期结束后,内部采样电容器从输入端子断开,并通过第二组开关连接到ADC的输入端,在此期间,ADC正在进行模数转换。图73说明了这种架构。

SAR ADC输入和采样电容器必须在ADC采集时间内由OPA625驱动到16位电平。在图72所示的例子中,OPA625被用来以1 MSPS的采样率驱动ADS8860。

详细设计程序

图72所示的电路由SAR ADC驱动器、低通滤波器和SAR ADC组成。SAR ADC驱动电路由OPA625组成,其反转增益为1。滤波器由RFLT和CFLT组成,连接在OPA625的输出端和ADS8860的输入端。为这些无源元件中的每一个选择合适的值对于从ADC获得最佳性能至关重要。电容器CFLT用作电荷库,向ADC采样电容器提供必要的电荷。ADC提供的动态负载在滤波器电容器CFLT上产生故障。若要最小化此故障的大小,请为CFLT选择一个足够大的值,以保持故障振幅小于100 mV。在放大器输出端保持如此低的故障幅度可以确保放大器保持在线性工作区,并导致最小的稳定时间。使用方程式6,选择10 nF电容器用于CFLT。

将10nF电容器直接连接到OPA625的输出会降低OPA625的相位裕度,并导致稳定性和稳定时间问题。为了正确驱动10nF电容器,使用串联电阻器(RFLT)将电容器CFLT与OPA625隔离。RFLT的大小必须基于多个约束条件。为了确定合适的RFLT值,考虑RFLT与ADC输入电路的开关电阻(RSW)反应产生的分压器效应对THD的影响,以及输出阻抗对放大器稳定性的影响。在本例中,选择了4.7Ω电阻器。在这个设计示例中,图16可用于估计RISO的合适值。RISO表示与CFLT串联的总电阻,在本例中相当于2×RFLT。

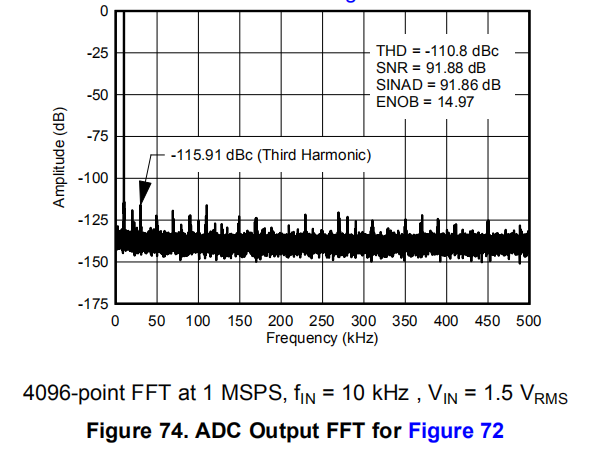

应用曲线

图74说明了图72所示电路的性能。

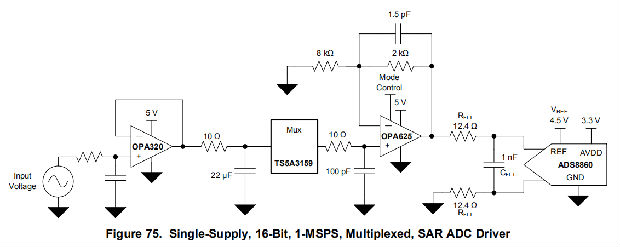

单电源,16位,1-MSPS,多路复用,SAR ADC驱动器

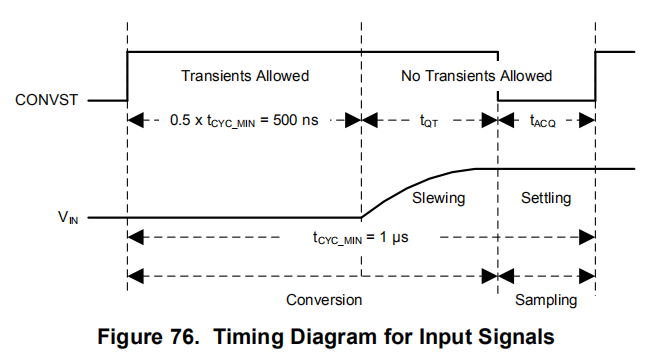

为了在最大吞吐量下操作高分辨率16位ADC,满标度电压阶跃必须在指定的最小采集时间(tACQ)内稳定在ADC输入处的16位精度以上。这种设置对驱动放大器在大信号带宽、转换速率和稳定时间方面提出了非常严格的要求。图75说明了一个使用OPA625的典型多路ADC驱动程序应用程序。

设计要求

为了优化该电路的性能,这种设计不允许在驱动电路的输入端出现任何大信号输入瞬变,直到上一次转换结束时的一个小的安静时间段(tQT)。输入阶跃电压从转换开始(CONVST上升沿)到半周期(0.5×tCYC)的任何时间都可能出现。在最坏的情况下,输入步骤上的定时限制允许ADC输入在所需精度范围内的最小稳定时间(tQT+tACQ)。这为放大器的输出提供了更多的时间,以便在下一次转换开始之前在所需精度范围内进行转换和稳定。图76说明了这个时序。

详细设计程序

ADC输入驱动电路主要由驱动放大器和飞轮RC滤波器两部分组成。放大器用于输入电压的信号调节,其低输出阻抗在信号源和ADC输入之间提供缓冲。RC滤波器有助于衰减ADC的开关电容输入级的采样电荷注入,也可以作为抗混叠滤波器,对前端电路产生的宽带噪声进行频带限制。ADC输入驱动器的设计涉及优化电路带宽,主要由以下要求驱动:

•RFLTCFLT滤波器带宽应较低,以限制输入ADC输入的噪声,从而提高系统的信噪比(SNR)。

•整个系统带宽应足够大,以适应转换开始前ADC输入处输入信号的最佳设置。

根据方程式7选择CFLT。CFLT选择为1nf。

将1-nF电容器直接连接到OPA625的输出会降低OPA625的相位裕度,并导致稳定性和稳定时间问题。为了正确驱动1-nF电容器,使用串联电阻器RFLT将电容器CFLT与OPA625隔离。RFLT的大小必须基于多个约束条件。为了确定合适的RFLT值,系统设计者必须考虑RFLT与ADC输入电路的开关电阻RSW反应产生的分压器效应对THD的影响,以及输出阻抗对放大器稳定性的影响。在本例中,选择12.4Ω电阻器。在这个设计示例中,图15可用于估计RISO的合适值。RISO表示与CFLT串联的总电阻,在本例中相当于2×RFLT。

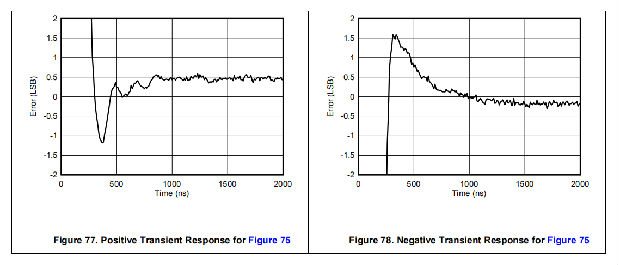

应用曲线

图77说明了图75所示电路的性能。

电源建议

OPAx625的工作电压为2.7 V至5.5 V(±1.35 V至±2.75 V);许多规范适用于-40°C至+125°C。典型特性中给出了与工作电压或温度相关的显著变化的参数。将旁路电容器放在电源引脚附近,以减少噪声或高阻抗电源的耦合误差。有关旁路电容器放置的详细信息,请参阅布局部分。

注意安全

大于6V的电源电压会对设备造成永久性损坏。请参阅绝对最大额定值部分。

布局

布局指南

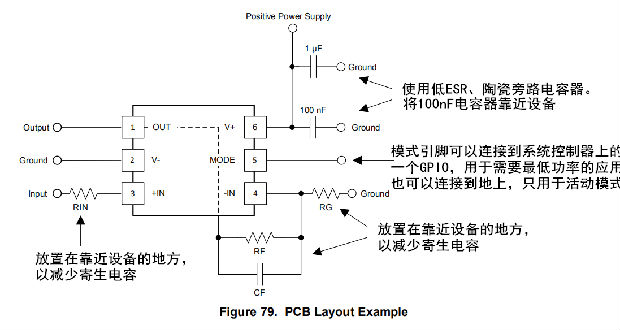

为获得设备的最佳操作性能,请使用良好的PCB布局实践,包括:

•使用旁路电容器来降低电源耦合的噪声。将低ESR、陶瓷、旁路电容器连接在电源引脚(V+和V-)和接地层之间。如图79所示,将旁路电容器放置在尽可能靠近装置的位置,并使100 nF的电容器离装置最近。对于单电源应用,不需要V引脚上的旁路电容器。

•电路模拟和数字部分的单独接地是最简单和最有效的噪声抑制方法之一。多层印刷电路板上的一层或多层通常用于接地层。接地板有助于分配热量并减少电磁干扰噪音。确保在物理上分离数字和模拟接地,注意接地电流的流动。有关更多详细信息,请参阅SLOA089,电路板布局技术。

•为了减少寄生耦合,输入轨迹应尽可能远离电源或输出轨迹。如果不可能使它们分开,最好垂直于敏感记录道,而不是与有噪声的记录道平行。

•尽量减少+IN和OUT之间的寄生耦合,以获得最佳交流性能。

•将外部组件尽可能靠近设备。如图79所示,保持RF、CF和RG接近逆变输入将使寄生电容最小化。

•输入记录道的长度应尽可能短。始终记住,输入轨迹是电路中最敏感的部分。

•建议在板组装后清洁PCB,以获得最佳性能。

•任何精密集成电路都可能因水分进入塑料包装而发生性能变化。在任何水性PCB清洁过程之后,烘烤PCB组件以去除清洁过程中引入设备包装的水分。在大多数情况下,在85°C下低温、清洁后烘烤30分钟就足够了。

布局示例