GS4911B/GS4910B HD/SD/带GENLOCK的图形时钟和定时发生器(1)

日期:2020-1-3视频时钟合成

生成任何高达165MHz的视频或图形时钟

为8个视频和13个图形时钟预先编程

自由运行时钟频率的精度仅受晶体参考

一个差分和两个单端视频/图形时钟输出

每个时钟可单独延迟以进行倾斜控制视频输出时钟可以直接连接到Gennum的SMPTE兼容HD-SDI输出的序列化程序音频时钟合成(仅限GS4911B)

三个音频时钟输出

产生高达512*96kHz的任何音频时钟

为7个音频时钟预先编程

定时生成

一次最多生成8个定时信号

从9个预先编程的定时信号中选择:H和V同步和消隐、F同步、F数字、AFS(仅GS4911B)、显示器启用、10FID和多达4个用户定义的定时信号预编程为35个不同视频生成计时格式和13种不同的图形显示格式

Genlock功能

时钟可以自由运行或锁定到输入端可变偏移步长为100-200ps的参考(取决于准确的时钟频率)

可变定时偏移步长为100-200ps,最多一帧输出可以交叉锁定到不同的输入参考失去参考时的冻结操作在应用参考时可选择碰撞或漂移锁定自动输入格式检测

一般特征

减少设计复杂度并节省板空间-9mm x9mm包装+水晶参考替代多个压控振荡器、锁相环和定时发生器无铅和符合RoHS低功率运行,通常为300mW1.8V核心和1.8V或3.3V I/O电源64针QFN封装

应用

摄像机;数字音频和/或视频录制/播放后台设备;数字音频和/或视频处理设备;计算机/视频显示器;DVD/MPEG设备;数字设备机顶盒;视频投影仪;高清视频系统;多媒体PC应用

说明

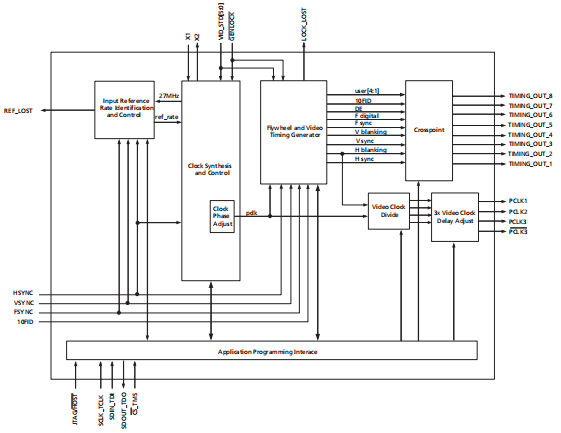

GS411B是一种高度灵活的数字控制时钟。具有genlock功能的合成电路和时序发生器。它可用于产生视频和音频时钟和定时信号,并允许多个设备被genlock到一个输入引用。GS4910B包含GS4911B的所有功能,但是不提供音频时钟或AFS脉冲产生。GS4911B/GS4910B将识别输入参考信号符合36种不同的视频标准和16种不同的图形格式,并将生成锁定输出计时信息传入的引用。GS4911B/GS4910B支持交叉锁定,允许将输出锁定到传入与输出视频标准不同的参考挑选出来的。用户可以选择输出8个不同的视频样本中的一个时钟速率或13种不同的图形显示时钟速率,或对13.5MHz到165MHz之间的任何时钟频率进行编程。所选择的时钟频率可以使用内部分频器,可用于两个视频时钟输出和一个LVDS视频时钟输出对。视频时钟是频率和相位锁定到水平定时基准,并且可以相对于时钟的定时输出单独延迟倾斜控制。提供八个用户可选择的定时输出,可以自动产生35的以下定时信号不同的视频格式和13种不同的图形格式:HSync,Hblanking、VSync、Vblanking、F sync、F digital、AFS(GS4911B仅限)、DE和10FID。这些定时输出可以锁定到用于genlock定时的输入参考信号,可以是相位通过内部寄存器调整。此外,GS4911B还提供三个音频采样时钟输出可产生频率范围高达512fs的音频时钟从9.7千赫到96千赫。音频到视频相位调整通过外部10FID输入参考,10FID信号通过内部寄存器,或用户编程的音频帧序列。GS4911B/GS4910B不含铅,且封装化合物不含卤化阻燃剂(RoHS合规)。

参考信号输入

信号电平与LVCMOS/LVTTL兼容。VSYNC外部参考信号通过应用层。当GS4911B/GS4910B在Genlock模式,设备感应VSYNC输入的极性自动,并引用前缘。如果用户希望选择一个预先编程的视频和/或设备提供的定时输出信号,则该信号必须遵循36个定义的视频或16个不同图形中的一个设备支持的显示标准。以这种方式操作时,VSYNC输入提供垂直扫描参考信号。VSYNC信号可能具有模拟定时,例如来自同步的分隔符,或者可以是数字的,例如来自SDI反序列化程序。第20页第1.4节介绍了GS4911B/GS4910B识别的36种视频格式和16种图形格式。50,62个IO U VDD–电源供应数字I/O信号的大多数正电源连接。连接到+1.8V DC或+3.3V DC。注意:所有5个IO U VDD引脚必须由相同的电压供电。19 FSYNC非同步的输入参考信号输入信号电平与LVCMOS/LVTTL兼容。FSYNC外部参考信号通过应用层。第一场被定义为第一个宽脉冲的场(也称为锯齿)位于直线的前半部分。FSYNC信号应在基于同步的第一个字段中设置为高参考文献。如果用户希望选择一个预先编程的视频和/或设备提供的定时输出信号,则该信号必须遵循36个定义的视频或16个不同图形中的一个设备支持的显示标准。以这种方式操作时,FSYNC输入提供奇偶字段输入参考资料。FSYNC信号可能具有模拟定时,例如来自同步的分隔符,或者可以是数字的,例如来自SDI反序列化程序。GS4911B/GS4910B识别的36种视频格式和16种图形格式。对于基于消隐的引用,FSYNC信号应设置为高在第二场比赛中。注意:如果输入引用格式不包括F sync信号,该引脚应保持在低位。

笔记:

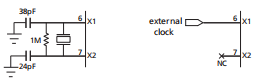

1.列出的电容值代表总电容,包括离散电容和寄生板电容。

2.X1用作一个输入,它也可以接受27MHz的时钟来源。为了适应这种情况,推荐使用不匹配的电容值。

图1-1:XTAL1和XTAL2参考电路

1.4预先编程认可的视频和图形标准表1-2描述了GS4911B/GS4910B。36种不同的视频格式和16种不同的图形下面列出的显示格式可以应用于GS4911B/GS4910B并自动由参考格式检测器检测。此外,除了VID_STD[5:0]=2、52、53或54,可通过设置定时输出引脚输出视频标准[5:0]针。除了表1-2中列出的预编程视频标准,自定义输出定时信号可由GS4911B/GS4910B产生。自定义定时当VID U STD[5:0]设置为62时,参数在主机接口中编程(参见第74页第3.10节)。将VID_STD[5:0]设置为63将导致设备产生输出格式与检测到的输入参考相同的定时。如果需要,可以通过设置视频控制寄存器,可通过主机接口的视频标准[5:0]寄存器(见第79页第3.12.3节)。虽然在这种情况下,外部视频标准[5:0]管脚将被忽略,它们不应保持浮动。

1.5输出定时信号表1-3描述了通过引脚向用户提供的输出定时信号计时1到计时8。用户可以输出下面列出的任何信号通过编程每个管脚上的输出选择寄存器,从主机接口。s公司表1-3:输出定时信号信号名称描述默认输出引脚H同步H同步信号在水平同步开始时有一个前缘脉搏。其长度由选定的视频标准决定,或根据主机接口。H同步输出脉冲的宽度由选定的视频决定标准。表1-2列出了每个预编程视频和图形标准GS4911B/GS4910B。自定义视频计时参数也可以是在主机接口中编程以定义唯一的H同步宽度在Genlock模式下,输出H Sync信号的前缘是名义上与参考的半振幅点同时HSYNC输入。此定时可以使用Genlock偏移寄存器进行偏移从主机接口的地址1Bh开始。默认情况下,系统复位后,H同步信号输出的极性将积极低调。极性可选择为高活性在主机接口地址56h编程极性寄存器。计时1H消隐H消隐信号用于指示视频线的非包含活动视频数据。对于包含有效视频样本的视频线。信号将在行的第一个有效像素,以及行的最后一个有效像素之后的高像素。在整个水平消隐过程中,H消隐信号保持较高周期。此信号的宽度将由选定的视频标准决定,或根据主机接口。在Genlock模式下,输出H消隐信号将被锁相参考HSYNC输入。可以使用从主机接口地址1Bh开始的Genlock偏移寄存器。此信号的默认极性可以通过编程主机接口地址56h处的极性寄存器。

详细说明

3.1功能概述

GS411B/GS410B是一种高度灵活的数字控制时钟合成电路。以及具有genlock功能的定时发生器。设备有两种主要操作模式:Genlock模式和Free Run模式。在Genlock模式,视频时钟和定时输出,将被频率和相位锁定检测到的参考输入信号。在自由运行模式下,所有频率基于27MHz外部晶体参考。GS4911B/GS4910B将识别符合36的输入参考信号不同的视频标准和16种不同的图形格式。它支持交叉锁定,允许输出被genlock到不同于已选择输出视频标准。当设备处于Genlock模式并且删除了输入引用时GS4911B/GS4910B将进入冻结模式。在这种模式下,输出时钟和定时信号将保持其先前锁定的相位和频率在+/-下午2点。用户可以选择输出8个不同的视频采样时钟速率或13个不同的图形显示时钟频率,或可编程13.5MHz至165兆赫。所选择的时钟频率可以在内部进一步划分,并且可用两个视频时钟输出和一个LVDS视频时钟输出对。视频时钟可以对于时钟偏差的定时输出,也应单独延迟相位控制。提供八个用户可选择的定时输出,可自动产生跟踪35种不同视频格式和13种不同图形的定时信号格式:HSync、Hblanking、VSync、Vblanking、F sync、F digital、AFS(仅限GS4911B)、DE,和10个氢火焰离子化检测器。或者,可以在主机中编程定制输出定时信号接口。此外,GS4911B还提供三个音频采样时钟输出,可以产生音频时钟高达512fs,频率范围为9.7kHz至96kHz。音视频相位通过外部10FID输入参考,通过内部寄存器,或用户编程的音频帧序列。

3.2操作模式

GS4911B/GS4910B将在Genlock模式或Free Run模式下运行取决于GENLOCK pin的设置。如果需要,可以通过设置Genlock_控制寄存器(地址16h),以便Genlock可以通过主机接口。尽管外部GENLOCK pin将在这种情况下被忽略,它不应该保持浮动

3.2.1 Genlock模式

当应用层将GENLOCK pin设置为低并且设备已成功genlocked输出到输入引用,GS4911B/GS4910B将进入Genlock模式。在此模式下,所有时钟和定时发生器输出将是频率和相位锁定到检测到的输入参考信号。PCLK输出将锁定到H参考资料。在Genlock模式下,使用应用的参考信号。27MHz晶体基准是必要的;但是,晶体精度和晶体频率都没有变化(由于工作温度)将影响输出信号。例如,输出信号将以相同的精度生成27MHz参考晶体是否具有精度为10ppm或100ppm。GS4911B/GS4910B支持交叉锁定,允许将输出锁定到与所选输出视频标准不同的传入引用。注意:在设置之前,用户必须对设备的输入应用引用GENLOCK=低。如果GENLOCK引脚设置为低并且没有参考信号,则所生成的设备时钟和定时输出可对应于内部缺省值设置芯片直到应用参考。3.2.1.1 Genlock定时偏移默认情况下,时钟和超时信号的相位被genlocked到输入端参考信号。这些输出信号可以相对于输入进行相位调整通过编程主机接口进行参考。偏移量为按时钟相位、水平相位和垂直相位分别编程(即像素、像素和线条的分数)。Genlock定时偏移可用于对设备的输出进行同步包含GS4911B/GS4910B,其他设备的输出位于位置。离开包含GS4911B/GS4910B的设备的信号在到达之前,可能会经过具有明显固定延迟的处理设备切换器。这些延迟可以包括视频线延迟甚至场延迟。到补偿这些延迟,genlock定时偏移允许用户将设备相对于输入基准的输出。使用主机接口,一旦设备稳定锁定:时钟相位偏移(1Dh)-范围为0到1个时钟脉冲,增量为在时钟周期的1/64到1/512之间(取决于PCLK频率)。这个增量在100ps到200ps之间。所有时钟和定时输出信号将被该寄存器中编程的时钟相位偏移延迟。H_Offset(1Bh)-参考HSYNC信号和输出之间的差异时钟脉冲中的H同步和/或H消隐信号,控制范围为0到+1行。所有定时输出信号将被编程的水平偏移延迟在这个登记册里。