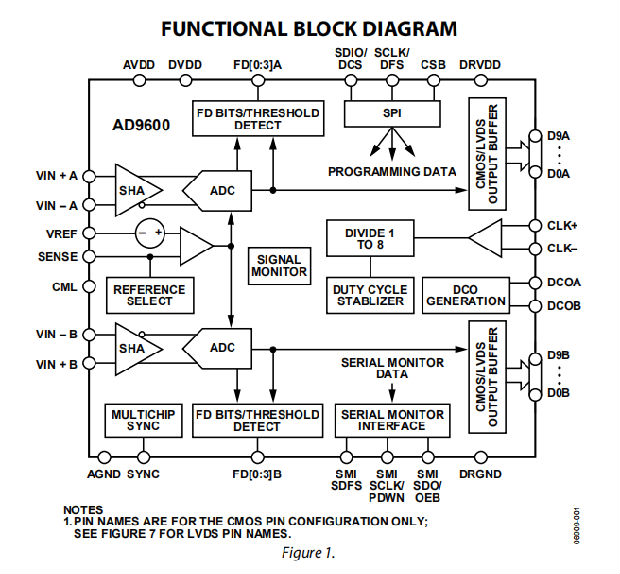

AD9600是10位,105 MSPS/125 MSPS/150 MSPS,1.8 V双模数转换器Ⅰ

日期:2020-4-6特征

信噪比=60.6dbc(61.6dbfs)至70mhz,150毫秒/秒;SFDR=81 dBc至70 MHz,150毫秒/秒;低功率:在150 MSPS时为825 mW;1.8V模拟电源操作;1.8 V至3.3 V CMOS输出电源或1.8 V LVDS电源;整数1到8输入时钟分配器;中频(中频)采样频率高达450兆赫;内部模数转换器(ADC)电压基准;集成ADC采样和保持输入;灵活的模拟输入:1 V p-p至2 V p-p范围;650兆赫带宽的差分模拟输入;ADC时钟占空比稳定器;95分贝信道隔离/串扰;串行端口控制;用户可配置的内置自检(BIST)功能;节能掉电模式;集成接收功能;快速检测/阈值位;复合信号监测仪。

应用

点对点无线电接收机(GPSK、QAM);分集无线电系统;I/Q解调系统;智能天线系统;数字预失真;通用软件无线电;宽带数据应用;数据采集;无损检测。

产品亮点

1、集成双10位150 MSPS/125 MSPS/105 MSPS模数转换器。

2、快速超量程检测和串行输出信号监测。

3、具有专用串行输出模式的信号监视器块。

4、专有的差分输入在高达450mhz的输入频率下保持良好的信噪比性能。

5、AD9600由一个1.8V电源供电,并具有一个单独的数字输出驱动电源,以适应1.8V到3.3V的逻辑系列。

6、标准串行端口接口支持各种产品特性和功能,例如数据格式化(偏移二进制、双倍补码或灰色编码)、启用时钟DCS、断电模式和电压参考模式。

7、AD9600与AD9627-11、AD9627和AD9640兼容,允许从10位简单地迁移到11位、12位或14位。

一般说明

AD9600是一个双10位105 MSPS/125 MSPS/150 MSPS ADC。它设计用于支持低成本、小尺寸和多功能性要求的通信应用。

双ADC核心采用多级差分流水线结构,集成了输出纠错逻辑。每个ADC具有宽带、差分采样和保持模拟输入放大器,支持多种用户可选择的输入范围。集成电压基准简化了设计考虑。提供占空比稳定器以补偿ADC时钟占空比的变化,从而使转换器保持优异的性能。

AD9600具有几个功能,可以简化通信接收器中的自动增益控制(AGC)功能。例如,快速检测特性允许以非常短的延迟输出四位输入级信息,从而实现快速超范围检测。

此外,可编程阈值检测器允许使用ADC的四个快速检测位以短延迟监测输入信号的幅度。如果输入信号电平超过可编程阈值,则精细阈值上限指示灯变高。由于此阈值是从四个msb设置的,因此用户可以快速调整系统增益以避免超范围情况。

AD9600的另一个与AGC相关的功能是信号监视器。该块允许用户监视输入信号的合成幅度,这有助于设置增益以优化整个系统的动态范围。

ADC输出数据可以直接路由到两个外部10位输出端口。这些输出可以设置为1.8 V至3.3 V CMOS或1.8 V LVD。此外,灵活的断电选项可以显著节省电力。

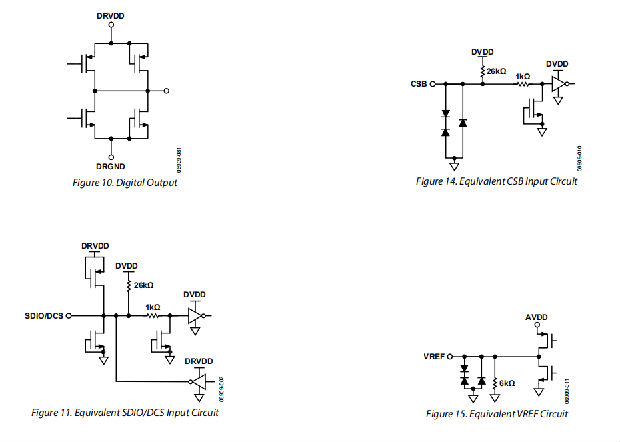

等效电路

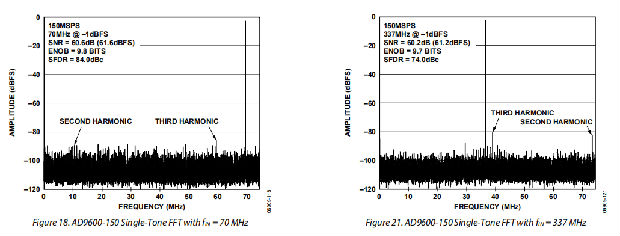

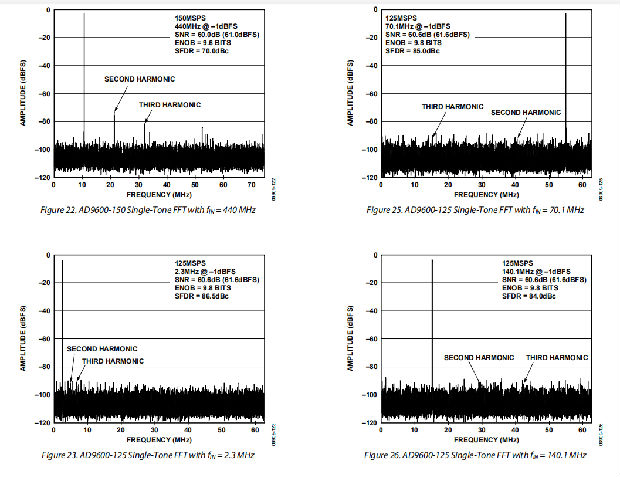

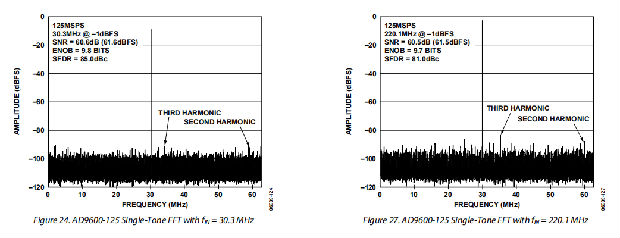

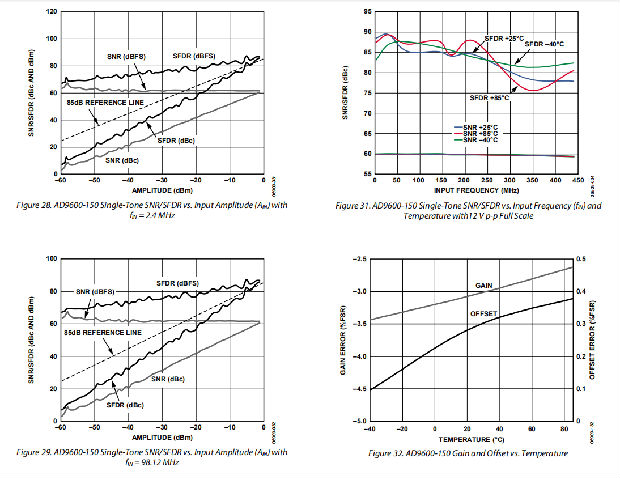

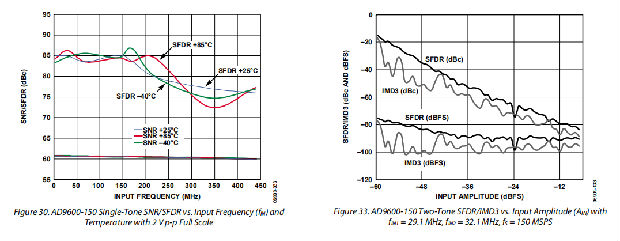

典型性能特征

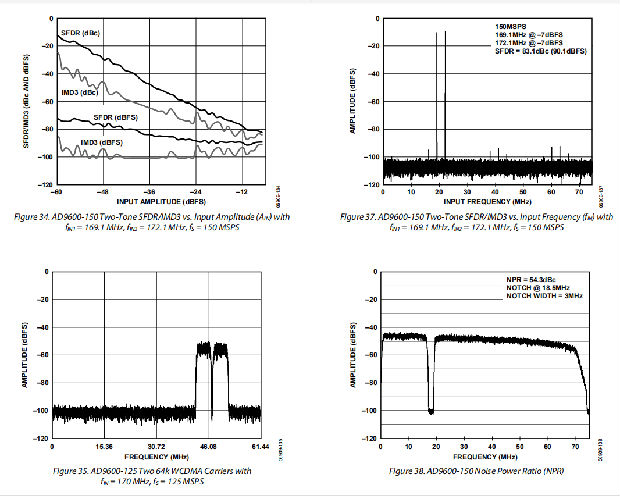

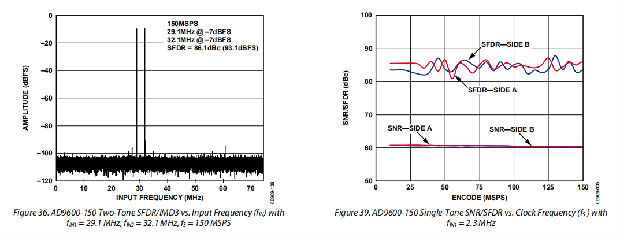

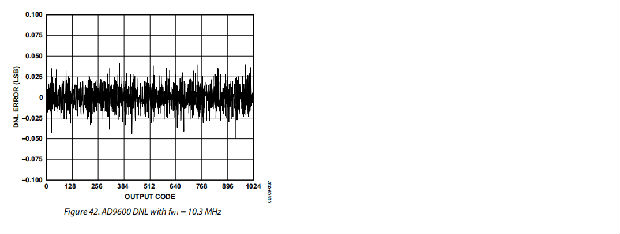

AVDD=1.8 V,DVDD=1.8 V,DRVDD=3.3 V,采样率=150 MSPS,启用DCS,1 V内部参考,2 V p-p差分输入,VIN=-1.0 dBFS,64k采样,T=25°C,除非另有说明。

操作理论

AD9600双ADC设计可用于信号的分集接收,其中ADC在同一个载波上相同地工作,但来自两个独立的天线。ADC也可以用独立的模拟输入操作。用户可以在ADC输入端使用适当的低通或带通滤波来采样从dc到200mhz的任何f/2频率段,而ADC性能损失很小。尽管允许高达450mhz的模拟输入工作,但在频率接近该范围的更高端时,ADC失真增加。

在非分散性应用中,AD9600可以用作基带接收器,其中一个ADC用于I输入数据,另一个用于Q输入数据。

提供同步功能以允许在多个信道或多个设备之间同步定时。

AD9600的编程和控制是使用3位SPI兼容串行接口完成的。

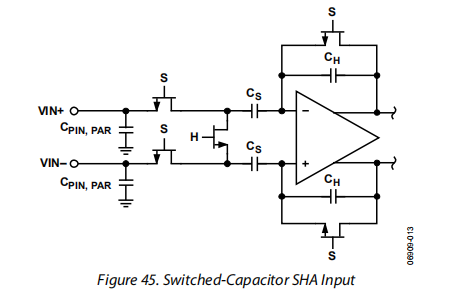

ADC架构

AD9600体系结构由双前端采样保持放大器(SHA)和流水线开关电容ADC组成。在数字校正逻辑中,来自每个级的量化输出被组合成最终的10位结果。流水线架构允许第一个阶段对新的输入样本进行操作,而其余阶段对前面的样本进行操作。采样发生在时钟的上升沿。

管道的每一级(不包括最后一级)包括一个连接到开关电容数模转换器(DAC)的低分辨率闪存ADC和一个级间剩余放大器(一个乘法数模转换器(MDAC))。剩余放大器放大重建的DAC输出和下一级流水线中的flash输入之间的差异。每个阶段使用一位冗余,以便于对闪存错误进行数字校正。最后一级由一个flash ADC组成。

每个通道的输入级包含一个差分SHA,该SHA可以在差分或单端模式下进行ac或dc耦合。输出暂存块对齐数据、更正错误并将数据传递到输出缓冲区。输出缓冲器由单独的电源供电,允许调整输出电压摆动。在断电期间,输出缓冲器进入高阻抗状态。

模拟输入注意事项

AD9600的模拟输入是一个差分开关电容器SHA,在处理差分输入信号时,该SHA被设计为具有最佳性能。

时钟信号交替地在采样模式和保持模式之间切换SHA(参见图45)。当SHA切换到采样模式时,信号源必须能够在半个时钟周期内为采样电容器充电并稳定下来。与每个输入串联的小电阻有助于降低驱动源输出级所需的峰值瞬态电流。并联电容器可以放置在输入端,以提供动态充电电流。这个无源网络在ADC的输入端创建一个低通滤波器;因此,精确值取决于应用程序。

在欠采样(如果采样)应用中,应减少任何并联电容器。与驱动源阻抗结合,并联电容器限制了输入带宽。见AN-742应用说明,开关电容ADC的频域响应;AN-827应用说明,A开关电容器与放大器接口的谐振方法ADC公司和模拟对话文章“宽带A/D转换器的变压器耦合前端”(第39卷,2005年4月)了解更多信息。一般来说,精确值取决于应用程序。

为了获得最佳的动态性能,驱动VIN+和VIN-的源阻抗应该匹配。

内部差分参考缓冲器产生正参考电压和负参考电压,定义ADC核心的输入范围。ADC核心的跨度由缓冲器设置为2×VREF。

输入共模

AD9600的模拟输入没有内部直流偏置。因此,在交流耦合应用中,用户必须在外部提供这种偏压。将设备设置为V=0.55×AVDD以获得最佳性能,但设备可以在更宽的范围内工作,并具有合理的性能(见图44)。设计中包括一个车载共模电压基准,可从CML引脚获得。当共模模拟输入的电压由CML引脚电压(通常为0.55×AVDD)设置。CML引脚必须通过0.1μF电容器与接地分离,如应用信息部分所述。

差分输入配置

在差分输入配置中驱动AD9600时实现最佳性能。对于基带应用,AD8138、ADA4937-2和ADA4938-2差分驱动器提供优异的性能和与ADC的灵活接口。AD8138的输出共模电压很容易用AD9600的CML引脚设置(见图46),并且驱动器可以配置成Sallen键滤波器拓扑结构,以限制输入信号的频带。

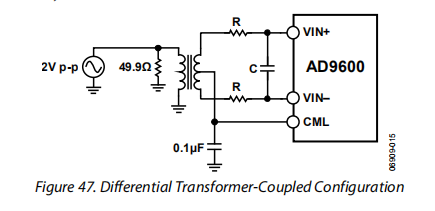

对于信噪比是一个关键参数的基带应用,差动变压器耦合是推荐的输入配置。示例如图47所示。CML电压可以连接到变压器二次绕组的中心抽头,以偏置模拟输入。

选择变压器时必须考虑信号特性。大多数射频变压器的饱和频率低于几兆赫。过大的信号功率会导致磁芯饱和,从而导致失真。

在第二奈奎斯特区及以上的输入频率下,大多数放大器的噪声性能不足以达到AD9600的真实信噪比性能。对于信噪比是一个关键参数的应用,推荐使用差分双巴仑耦合。示例如图49所示。

在第二奈奎斯特区及以上的输入频率下,大多数放大器的噪声性能不足以达到AD9600的真实信噪比性能。对于信噪比是一个关键参数的应用,推荐使用差分双巴仑耦合。举例说明了在第二奈奎斯特区的频率处使用变压器耦合输入的替代方案是使用AD8352差分驱动器。示例如图50所示。有关更多信息,请参阅AD8352数据表。

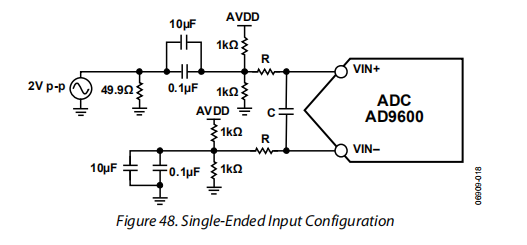

在任何配置中,并联电容器C的值取决于输入频率和源阻抗,可能需要减小或移除。表10列出了设置RC网络的建议值。但是,实际值取决于输入信号;因此,表10只应用作起始指南。

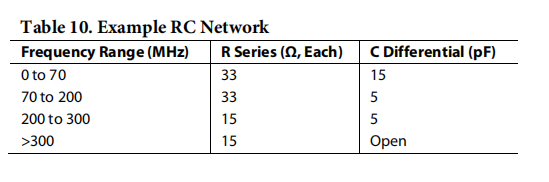

单端输入配置

单端输入可以在成本敏感的应用程序中提供足够的性能。在这种配置中,SFDR和失真性能由于大输入公共模式摆动而降低。如果每个输入端的源阻抗匹配,对信噪比性能的影响应该很小。图48详细说明了典型的单端输入配置。

电压基准

AD9600内置了稳定准确的电压基准。输入范围可以通过改变应用于AD9600的参考电压来调整,使用内部参考电压或外部应用的参考电压。ADC的输入范围跟踪参考电压的线性变化。本节总结了各种参考模式。参考解耦部分描述了参考的最佳PCB布局实践。

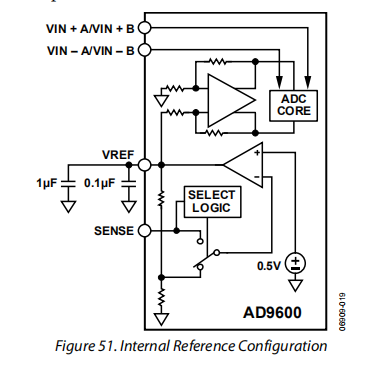

内部参考连接

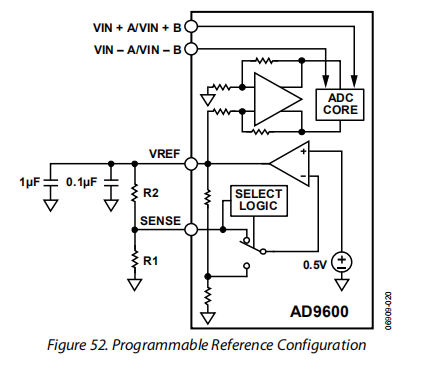

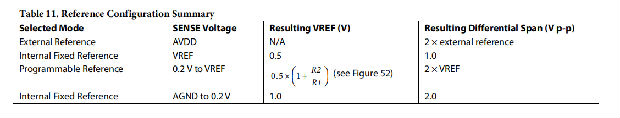

AD9600内的比较器检测传感管脚处的电位,并将参考配置为四种可能的模式,如表11所示。如果传感器接地,参考放大器开关连接至内部电阻分压器(见图51),将VREF设置为1.0 V。将传感器引脚连接至VREF将参考放大器输出切换至传感器引脚,完成回路并提供0.5 V参考输出。如图52所示,如果电阻分压器连接到芯片外部,开关将再次选择检测引脚。这使参考放大器处于非垂直模式,VREF输出定义为:

ADC的输入范围始终等于内部或外部参考的参考引脚电压的两倍。

如果使用AD9600的内部基准驱动多个转换器以改善增益匹配,则必须考虑其他转换器对基准的加载。图53描述了负载对内部参考电压的影响。

外部参照操作

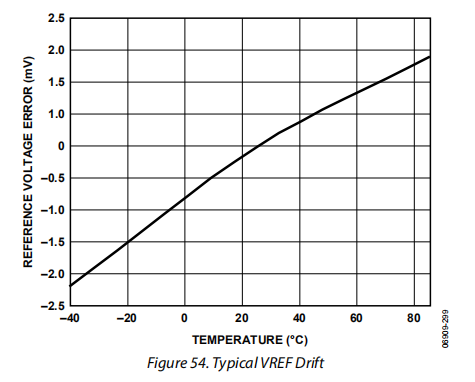

可能需要使用外部基准来提高ADC的增益精度或改善热漂移特性。图54显示了1.0V模式下内部基准的典型漂移特性。

当检测管脚绑定到AVDD时,内部引用被禁用,允许使用外部引用。内部参考缓冲器用等效的6 kΩ负载加载外部参考(见图15)。内部缓冲区为ADC核心生成正负满标度参考。因此,外部参考电压必须限制在最大1.0V。

时钟输入注意事项

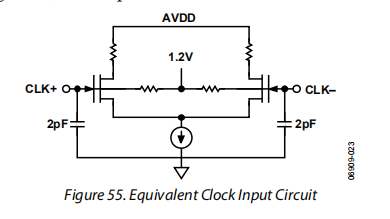

为了获得最佳性能,AD9600采样时钟输入(CLK+和CLK-)应使用差分信号计时。信号通常通过变压器或电容器交流耦合到CLK+和CLK-引脚。这些引脚内部偏置(见图55),不需要外部偏置。

时钟输入选项

AD9600具有非常灵活的时钟输入结构。时钟输入可以是CMOS、LVDS、LVPECL或正弦波信号。

无论所使用的信号类型如何,时钟源的抖动都是最受关注的,如抖动注意事项部分所述。

图56和图57显示了对AD9600进行时钟计时的首选方法(时钟频率高达625 MHz)。低抖动时钟源使用RF巴伦或RF变压器从单端信号转换为差分信号。

对于125兆赫至625兆赫之间的时钟频率,建议使用RF balun配置;对于10兆赫至200兆赫之间的时钟频率,建议使用RF变压器。通过二次变压器或巴伦的背靠背肖特基二极管将AD9600的时钟偏移限制在大约0.8V p-p差分。

这有助于防止时钟的大电压波动通过AD9600的其他部分馈送,同时保持对低抖动性能至关重要的信号的快速上升和下降时间。

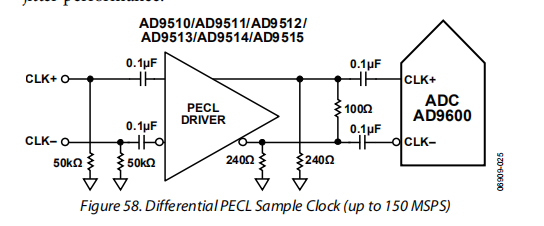

如果低抖动时钟源不可用,另一种选择是将差分PECL信号与采样时钟输入引脚进行交流耦合,如图58所示。AD9510/AD9511/AD9512/AD9513/AD9514/AD9515系列时钟驱动程序具有出色的抖动性能。

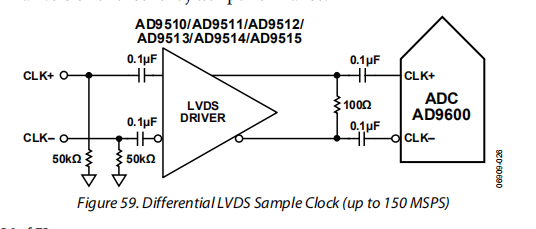

第三种选择是将差分LVDS信号与采样时钟输入引脚进行交流耦合,如图59所示。AD9510/AD9511/AD9512/AD9513/AD9514/AD9515系列时钟驱动程序具有出色的抖动性能。

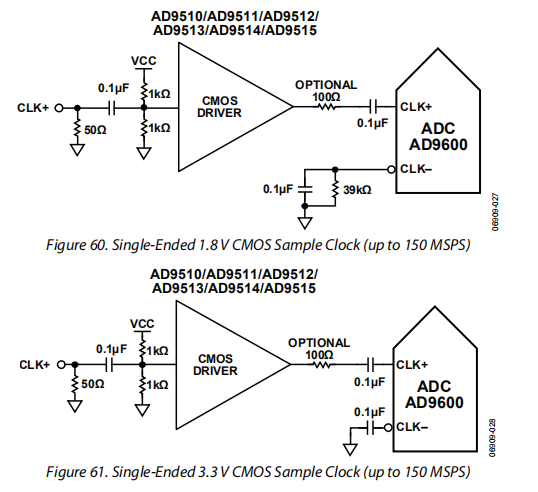

在某些应用中,可以使用单端CMOS信号驱动采样时钟输入。在这种应用中,CLK+应直接从CMOS栅极驱动,CLK-引脚应通过与39 kΩ电阻器并联的0.1μF电容器旁路接地(见图60)。尽管CLK+输入电路电源为AVDD(1.8 V),但该输入设计为可承受高达3.6 V的输入电压,因此可为驱动逻辑电压提供多种选择。

输入时钟分频器

AD9600包含一个输入时钟除法器,能够将输入时钟除以1到8之间的整数值。如果选择除1以外的分配比,则工作循环稳定器将自动启用。

AD9600时钟分配器可以使用外部同步输入进行同步。寄存器0x100的位1和位2允许在每个同步信号上或在寄存器写入后仅在第一个同步信号上重新同步时钟分配器。有效的同步会导致时钟分配器重置为其初始状态。此同步功能允许对齐多个设备的时钟分配器,以确保同时进行输入采样。

时钟占空比

典型的高速adc使用两个时钟边缘来产生各种内部定时信号。因此,这些adc可能对时钟占空比敏感。通常,时钟占空比需要±5%的公差,以保持动态性能特性。AD9600包含一个占空比稳定器(DC),它对非采样(或下降)边缘进行重定时,提供一个标称占空比为50%的内部时钟信号。这允许用户在不影响AD9600性能的情况下提供广泛的时钟输入占空比。当SDIO/DCS管脚用作DCS时,噪声和失真性能在很大的占空比范围内几乎是平坦的,如图43所示。

在输入上升沿的抖动是一个重要的问题,它并没有被内部稳定电路降低。占空比控制回路通常不适用于小于20 MHz的时钟频率。如果时钟速率可能动态变化,则需要考虑与环路相关联的时间常数。这需要在动态时钟频率增加或减少后1.5μs至5μs的等待时间,然后DCS回路重新锁定至输入信号。在此期间,回路未被锁定,DCS回路被旁路,内部装置定时取决于输入时钟信号的占空比。在这种应用中,可以适当地禁用工作时钟稳定器。在所有其他应用中,建议启用DCS电路,以最大限度地提高交流性能。

抖动注意事项

高速、高分辨率的adc对时钟输入的质量非常敏感。在给定的输入频率(f)下,由抖动(t)引起的信噪比下降可以计算为:

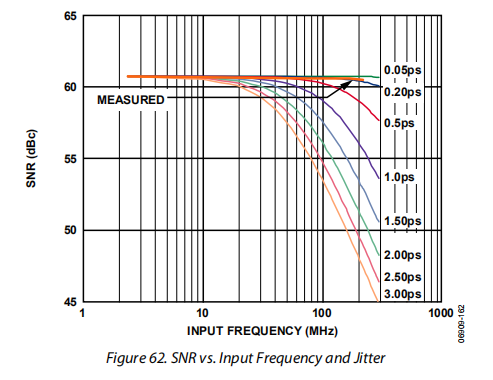

在这个方程中,rms孔径抖动表示所有抖动源的均方根,包括时钟输入、模拟输入信号和ADC孔径抖动。如果欠采样应用对抖动特别敏感(见图62)。

在孔径抖动可能影响AD9600的动态范围的情况下,时钟输入应被视为模拟信号。时钟驱动器的电源应与ADC输出驱动器电源分开,以避免用数字噪声调制时钟信号。低抖动,晶体控制振荡器是最好的时钟源。如果时钟是从另一种类型的源(通过选通、除法或其他方法)生成的,则在最后一步中应使用原始时钟对其进行重定时。

请参阅AN-501应用说明和AN-756应用说明,以获取有关ADC的抖动性能的更深入信息。

功耗和待机模式

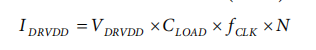

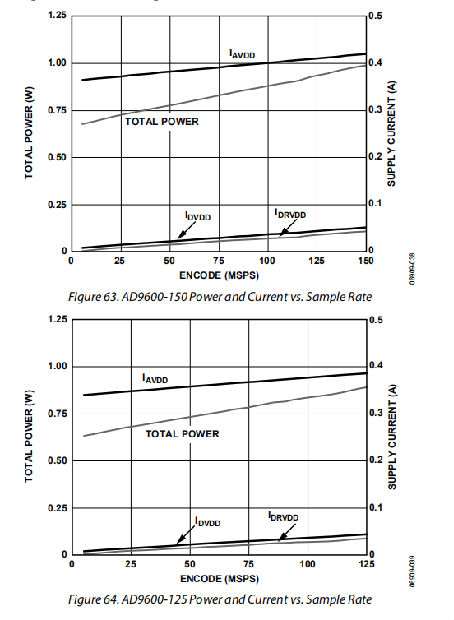

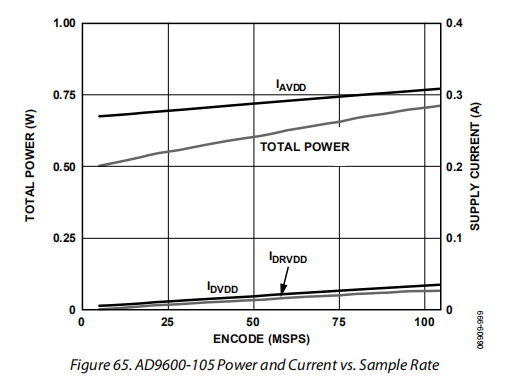

如图63所示,AD9600所消耗的功率与其采样率成正比。在CMOS输出模式下,数字功耗主要取决于数字驱动器的强度和每个输出位上的负载。

最大DRVDD电流(I)可计算为:

其中N是输出位的数目(在禁用快速检测输出管脚的AD9600的情况下为22)。

当每一个输出位在每一个时钟周期,即在奈奎斯特频率f/2下的一个满标度方波上切换时,就会出现这个最大电流。在实际应用中,DRVDD电流是由平均输出位数的开关量确定的,该开关量由采样率和模拟输入信号的特性决定。减少输出驱动器的电容负载可以使数字功耗最小化。图63中的数据是在与典型性能特征相同的操作条件下采集的,每个输出驱动器上有5 pF负载。

通过断言PDWN模式(通过SPI端口或通过断言PDWN pin高),AD9600被置于掉电模式。在这种状态下,ADC通常耗散2.5mw。断电时,输出驱动器处于高阻抗状态。断言PDWN引脚低将使AD9600返回其正常工作模式。注意,PDWN是指数字输出驱动电源(DRVDD),不应超过该电源电压。

在断电模式下,通过关闭参考、参考缓冲区、偏置网络和时钟来实现低功耗。内部电容器在进入断电模式时放电,恢复正常工作时必须重新充电。因此,唤醒时间与断电模式下花费的时间有关:断电周期越短,唤醒时间相应越短。

当使用SPI端口接口时,用户可以将ADC置于断电或待机模式。待机模式允许用户在需要更快唤醒时间时保持内部参考电路通电。有关详细信息,请参阅内存映射寄存器描述部分。

数字输出

AD9600输出驱动程序可配置为通过将DRVDD与接口逻辑的数字电源相匹配,与1.8 V至3.3 V逻辑系列接口。

在CMOS输出模式中,输出驱动器的大小可以提供足够的输出电流来驱动各种逻辑族。然而,大的驱动电流往往会导致电源上的电流故障,并可能影响转换器的性能。需要ADC驱动大电容负载或大扇形输出的应用可能需要外部缓冲器或锁存器。

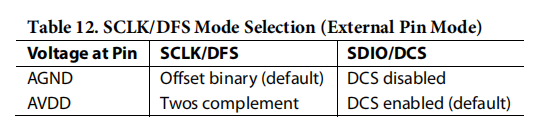

当在外部引脚模式下操作时,通过设置SCLK/DFS引脚,可以为偏移二进制或双倍补码选择输出数据格式(见表12)。如存储器映射寄存器描述部分所述,当使用SPI控制时,可以为偏移二进制、双倍补码或灰色代码选择数据格式。

数字输出启用功能(OEB)

AD9600对于数字输出管脚具有灵活的三态能力。三态模式可以通过使用SMI SDO/OEB引脚或SPI接口启用。如果SMI SDO/OEB引脚低,则启用输出数据驱动程序。如果SMI SDO/OEB管脚高,则输出数据驱动器处于高阻抗状态。此输出启用功能不用于快速访问数据总线。注意,OEB是指数字输出驱动电源(DRVDD),不应超过该电源电压。

当设备使用SPI接口时,通过使用寄存器0x14中的输出启用条位,每个通道的数据和快速检测输出管脚可以独立地进行三个声明。

时机

AD9600提供具有12个时钟周期的管道延迟的锁存数据。数据输出在时钟信号上升沿后的一个传播延迟(t)可用。

输出数据线的长度和负载应最小化,以减少AD9600内的瞬变。这些瞬态会降低转换器的动态性能。AD9600的最低典型转换速率通常为10 MSPS。当时钟速率低于10毫秒/秒时,动态性能可能会降低。

数据时钟输出(DCO)

AD9600提供两个数据时钟输出(DCO)信号,用于捕获外部寄存器中的数据。数据输出在DCO的上升沿上有效,除非通过SPI改变极性。有关更多信息,请参见图2和图3中所示的时序图。

ADC超量程和增益控制

在接收器应用中,期望有一种机制来可靠地确定转换器何时将被剪裁。标准溢出指示器提供了有关模拟输入状态的事后信息,但其作用有限。因此,有一个低于满标度的可编程阈值是有帮助的,该阈值允许在剪辑实际发生之前减少增益的时间。此外,由于输入信号可能具有显著的转换速率,因此该功能的延迟是主要关注的问题。高流水线转换器可能具有显著的延迟。一个很好的折衷办法是使用ADC第一级的输出位来实现这个功能。这些输出位的延迟非常低,总体分辨率不高。峰值输入信号通常在满标度至满标度以下6分贝至10分贝之间。3位或4位输出为该功能提供足够的范围和分辨率。

通过SPI端口,用户可以提供一个阈值,超过该阈值,超范围输出将被激活。只要信号低于这个阈值,输出就应该保持低。快速检测输出管脚也可以通过SPI端口编程,以便其中一个管脚可以作为当前使用此功能的客户的传统超量程管脚。在这种模式下,转换器的所有12位都以传统方式进行检查,在通常定义为溢出的情况下,输出很高。在任一模式下,计算条件时都会考虑数据的大小(但不考虑数据的符号)。阈值检测对期望幅度范围之外的正、负信号的响应相同。

快速检测概述

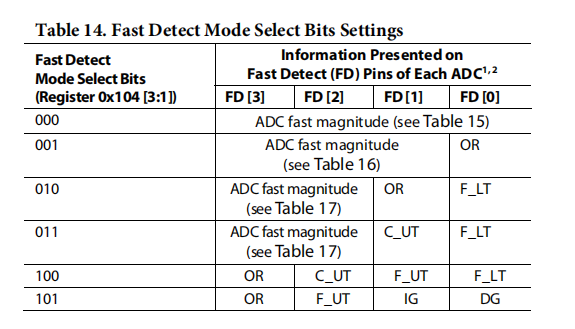

AD9600包含促进快速超量程检测的电路,允许非常灵活的外部增益控制实现。每个ADC有四个快速检测输出管脚,用于输出关于ADC输入电平的当前状态的信息。这些管脚的功能可通过寄存器0x104中的快速检测模式选择位和快速检测启用位进行编程,允许从内部数据路径中的多个点输出范围信息。根据可编程阈值水平,还可以设置这些管脚以指示是否存在超量程或超量程条件。表14显示了可用于快速检测管脚的六种配置。

1、CMOS模式配置的快速检测引脚为FD0A/FD0B至FD9A/FD9B,LVDS模式配置的快速检测引脚为FD0+/FD0-至FD9+/FD9-。

2、请参阅ADC超量程(或)和增益开关部分,以了解有关或、C_UT、F_UT、F_LT、IG和DG的更多信息。

ADC快速幅度

当快速检测输出管脚被配置为输出ADC快速幅度时(即,当快速检测模式选择位被设置为0b000时),所呈现的信息是来自仅具有两个时钟周期延迟(在CMOS输出模式时)的早期转换器级的ADC电平。在此配置中使用快速检测输出管脚可提供最早的液位指示信息。由于此信息是在数据路径的早期提供的,因此指示的级别存在明显的不确定性。表15显示了标称电平以及ADC快速幅度所示的不确定度。

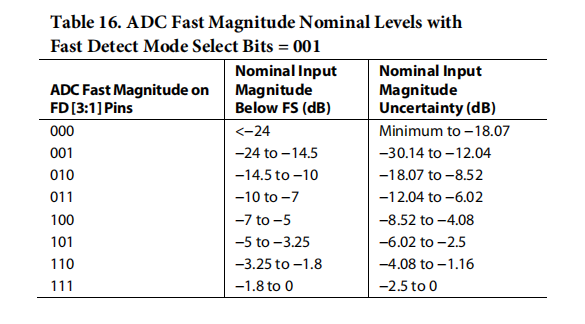

当快速检测模式选择位设置为0b001、0b010或0b011时,快速检测输出引脚的子集可用。在这些模式下,快速检测输出管脚具有6个时钟周期的延迟。表16显示了当快速检测模式选择位设置为0b001时(即,当FD[3:1]引脚上显示ADC快速幅度时)对应的ADC输入电平。

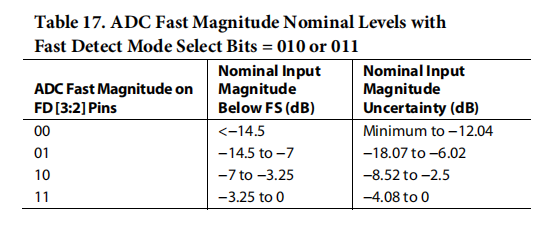

当快速检测模式选择位被设置为0b010或0b011(即,当FD[3:2]管脚上出现ADC快速幅度时),则不提供LSB。该模式的输入范围如表17所示。

ADC超量程(或)

当在ADC输入端检测到超量程时,ADC超量程指示器被断言。过量程条件在ADC管道的输出处确定,因此受12时钟周期延迟的影响。输入的超量程将由该位在发生后12个时钟周期来指示。

增益开关

AD9600包括在存在大动态范围或使用增益测距转换器的应用中有用的电路。该电路允许设置数字阈值,以便可以编程设置较高阈值和较低阈值。快速检测模式选择位=010到快速检测模式选择位=101支持增益切换选项的各种组合。

其中一个用途是检测ADC何时将在特定输入条件下达到满标度。其结果是提供一个指示器,可用于快速插入衰减器,防止ADC过驱动。

粗阈值(C_UT)

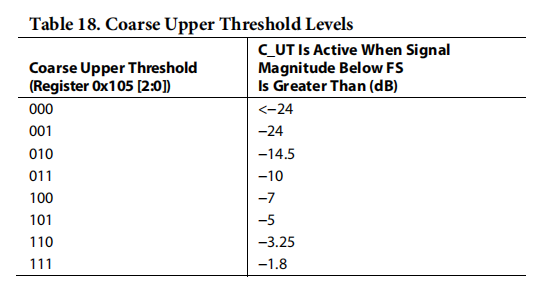

如果ADC快速幅度输入电平大于地址0x105处的粗略上限阈值寄存器中编程的电平[2:0],则断言粗略上限阈值指示器。粗上阈值输出在输入超过电平后两个时钟周期输出,因此提供输入信号电平的快速指示。粗略的阈值上限如表18所示。此指示灯在至少两个ADC时钟周期内保持断言状态,或直到信号降至阈值水平以下。

精细上阈值(F_UT)

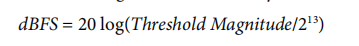

如果输入量超过位于地址0x106和地址0x107的精细上限阈值寄存器中编程的值,则断言精细上限阈值指示器。将13位阈值寄存器与ADC输出处的信号幅度进行比较。此比较受ADC时钟延迟的影响,但在转换器分辨率方面是准确的。精细阈值大小由以下等式定义:

细下限(F_LT)

如果输入幅度小于地址0x108和地址0x109处的精细下限阈值寄存器中编程的值,则断言精细下限阈值指示器。精细低阈值寄存器是一个13位寄存器,与ADC输出的信号幅度相比较。此比较受ADC时钟延迟的影响,但提供了与转换器分辨率精确的比较。细阈值大小在等式1中定义。

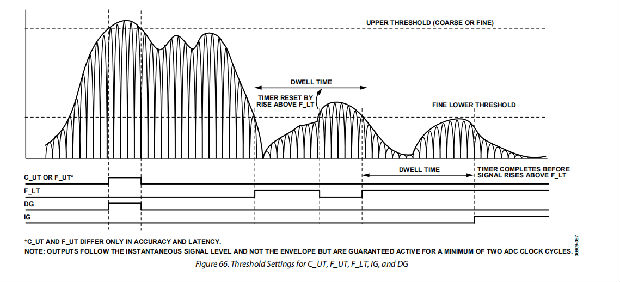

F_UT和F_LT指示器的操作如图66所示。

增量增益(IG)和减量增益(DG)

增量增益和减量增益指示器旨在一起使用,以提供信息,实现外部增益控制。减量增益指示器与粗略上限阈值位一起工作,当输入幅度大于粗略上限阈值寄存器(地址0x105)中的3位值时断言。类似地,增量增益指示符对应于精细下限阈值位,但仅当在停留时间过去之后,输入量小于精细下限阈值寄存器中编程的值时,才断言增量增益指示符。该暂停时间由16位增益增加暂停时间寄存器(地址0x10A和地址0x10B)设置,并且以ADC输入时钟周期为单位,范围从1到65535。精细低阈值寄存器是一个13位寄存器,与ADC输出的幅度相比较。此比较受ADC时钟延迟的影响,但允许更精细、更精确的比较。精细阈值大小在等式1中定义(参见精细上限阈值(F_UT)部分)。

衰减增益输出受快速检测输出管脚的影响,该管脚提供了潜在超量程条件的快速指示。增量增益指示器的断言基于ADC输出处的比较,要求输入幅度在向外部电路发送信号以增加增益之前,在预定义的时间段内保持在精确的可编程水平以下。

IG和DG指示器的操作如图66所示。