AD8031/AD8032是2.7V,800μA,80MHz轨对轨I/O放大器

日期:2020-4-17特征

低功率;电源电流800μA/放大器;完全规定在+2.7 V、+5 V和±5 V电源下;5V高速快速沉降;80兆赫,-3分贝带宽(G=+1);30v/μs转换率;125ns沉降时间至0.1%;轨对轨输入和输出;输入电压超过0.5V时无相位反转;输入CMVR超出轨道200 mV;输出摆幅至任一轨道的20 mV范围内;低失真-62分贝@1兆赫,VO=2伏p-p-86分贝@100千赫,VO=4.6伏p-p;输出电流:15毫安;高级选项:VOS(最大值)=1.5 mV。

应用

高速电池供电系统;高组分密度系统;便携式测试仪器;A/D缓冲器;有源滤波器;高速、设置和需求放大器。

一般说明

AD8031(单)和AD8032(双)单电源电压反馈放大器具有80mhz小信号带宽、30v/μs转换速率和125ns稳定时间的高速性能。这种性能是可能的,同时消耗不到4.0兆瓦的功率从一个单一的5伏电源。这些特性在不影响动态性能的前提下,增加了高速电池供电系统的运行时间。

产品具有真正的单电源供电能力,具有轨对轨输入和输出特性,并规定用于+2.7 V、+5 V和±5 V电源。输入电压范围可扩展到每轨500毫伏以上。输出电压在每条轨道的20毫伏范围内波动,提供最大的输出动态范围。

AD8031/AD8032还提供卓越的信号质量每个放大器的电源电流为800μA;THD为-62 dBc,带有2伏p-p,1兆赫输出信号,100千赫时为-86分贝,4.6伏p-p信号打开+5伏电源。低失真和快速的稳定时间使它们成为单电源adc的理想缓冲器。

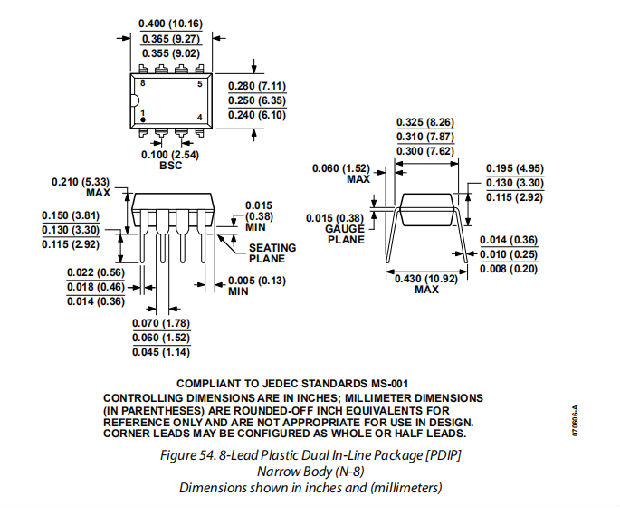

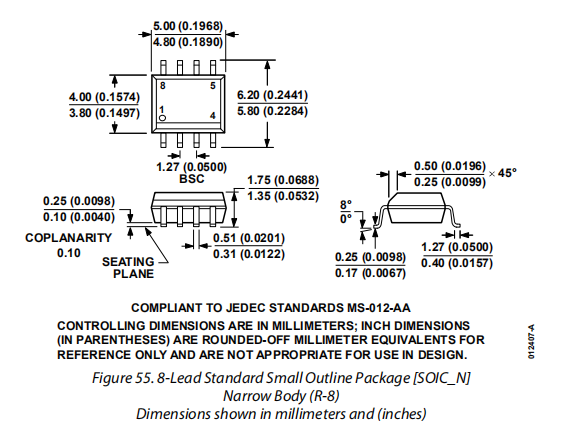

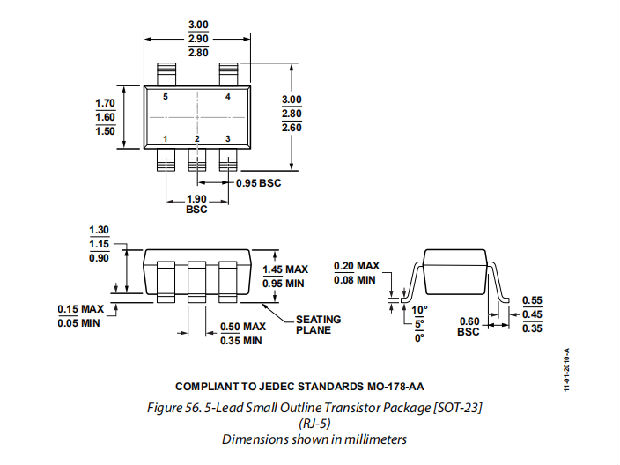

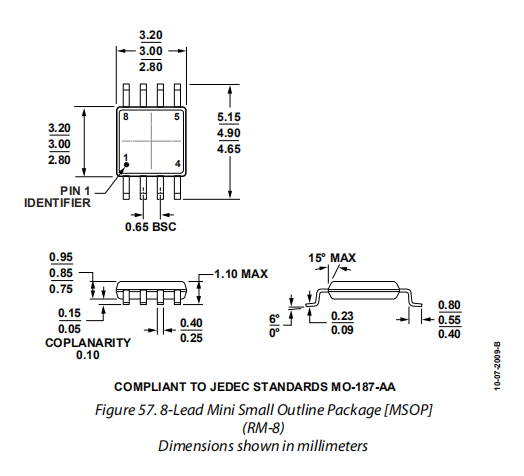

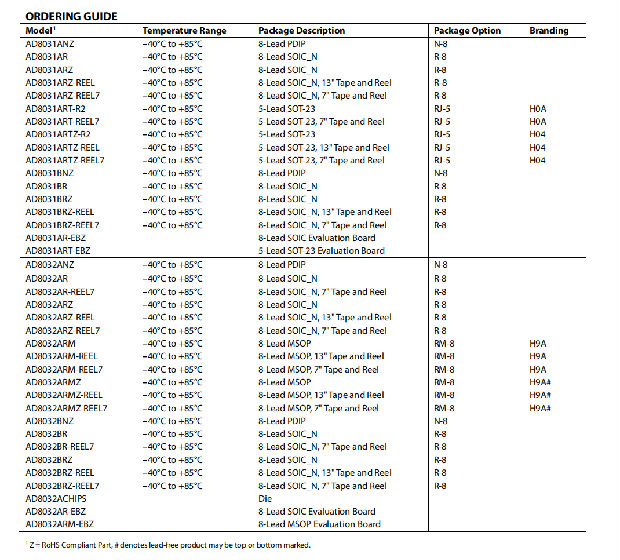

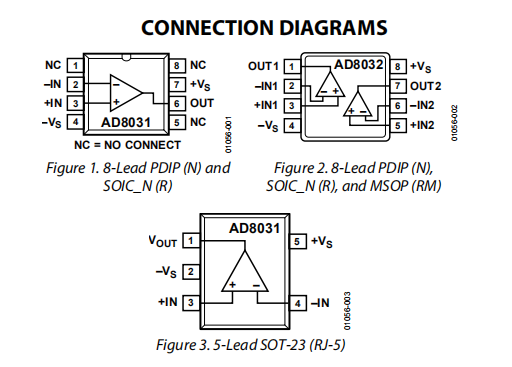

AD8031/AD8032工作在+2.7V至+12V的电源和高达±6V的双电源上,非常适合广泛的应用,从具有大带宽要求的电池供电系统到组件密度要求更低功耗的高速系统。AD8031/AD8032有8芯PDIP和8芯SOIC单元,可在−40°C到+85°C的工业温度范围内工作。AD8031A也有节省空间的5芯SOT-23单元,AD8032A有8芯MSOP单元。

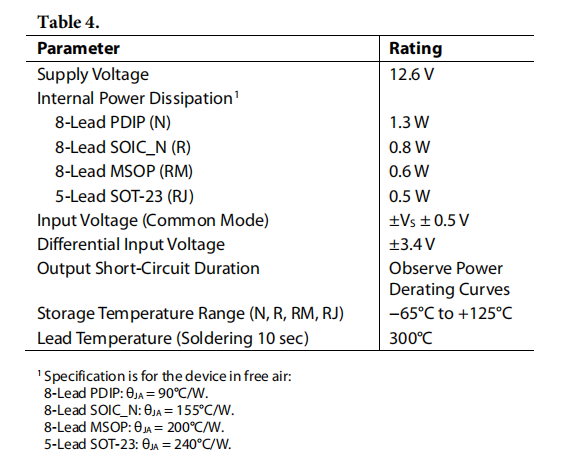

绝对最大额定值

高于绝对最大额定值的应力可能会对设备造成永久性损坏。这仅是一个应力额定值;设备在本规范操作章节所述条件或以上任何其他条件下的功能操作并不意味着。长期暴露在绝对最大额定条件下可能会影响设备的可靠性。

最大功耗

AD8031/AD8032可以安全地耗散的最大功率受到结温升高的限制。塑料封装器件的最高安全连接温度由塑料的玻璃化转变温度(约150°C)决定。暂时超过此限值可能会由于封装对模具施加的应力的变化而导致参数性能的变化。长时间超过175°C的结温会导致设备故障。

虽然AD8031/AD8032具有内部短路保护,但这可能不足以保证在所有条件下都不会超过最高结温(150°C)。为确保正常运行,有必要观察图7所示的最大功率降额曲线。

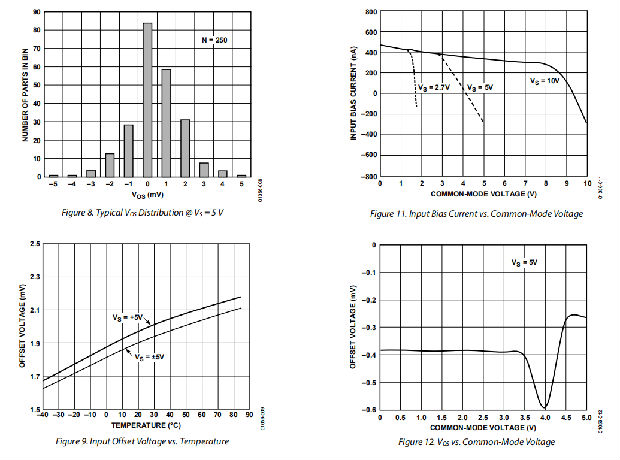

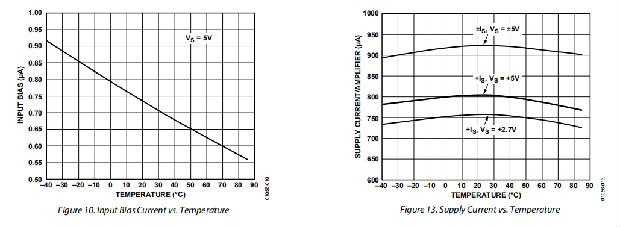

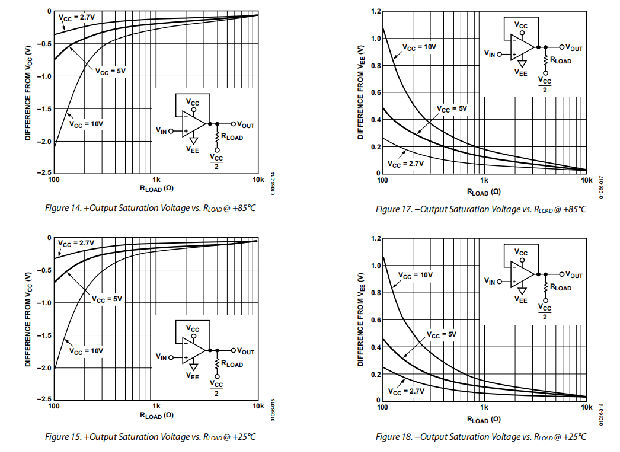

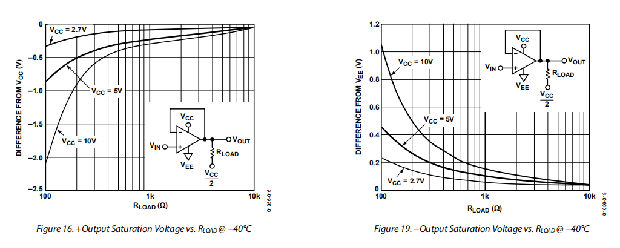

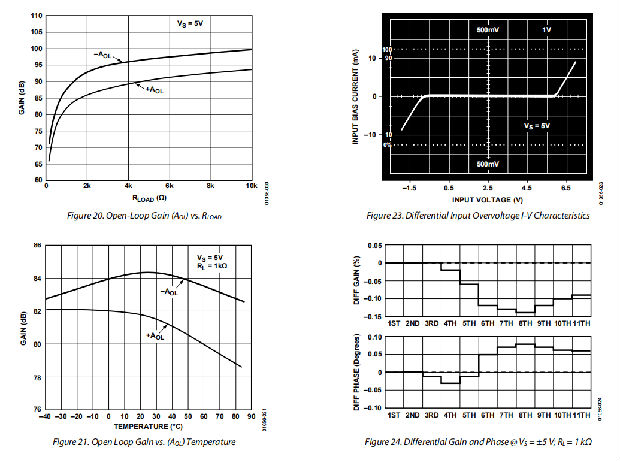

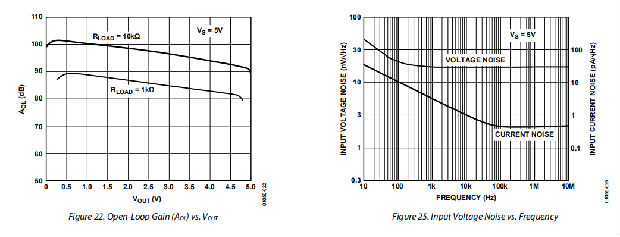

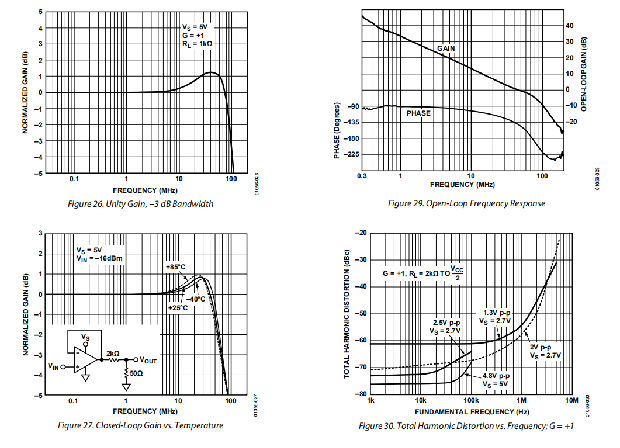

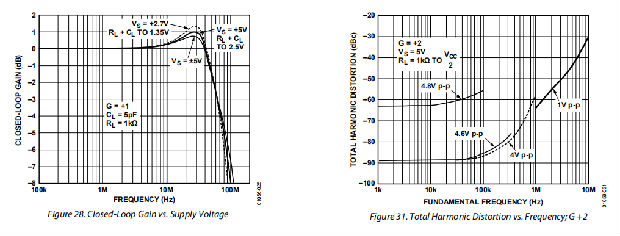

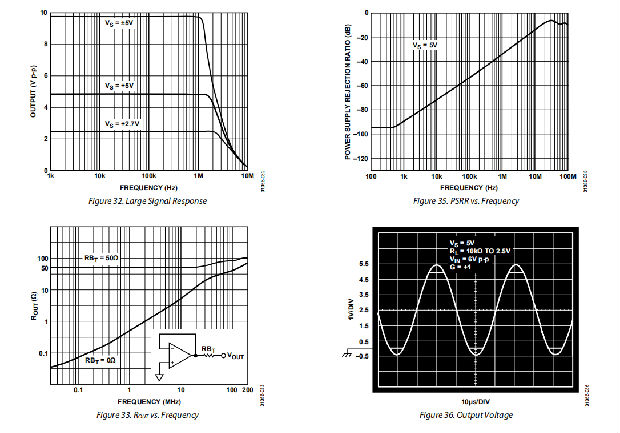

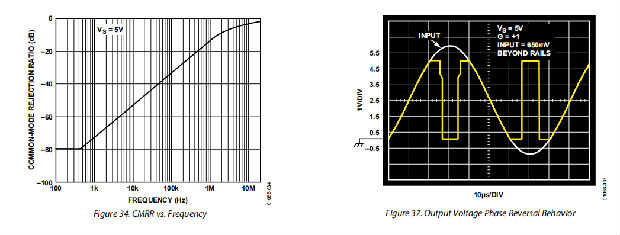

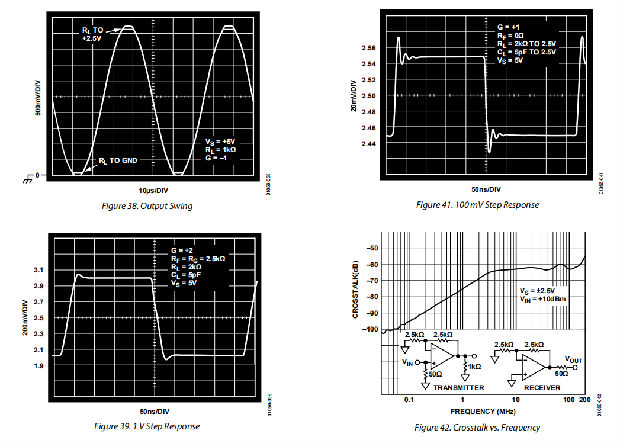

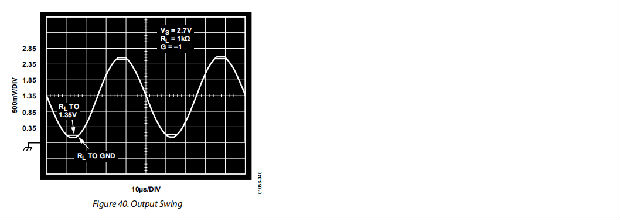

典型性能特征

操作理论

AD8031/AD8032是高速、低功耗、电压反馈放大器的单和双版本,具有创新的结构,最大限度地提高输入和输出的动态范围能力。线性输入共模范围超过任一电源电压200毫伏,且放大器在超过电源500毫伏时不显示相位反转。当驱动轻负载时,输出在任一电源的20毫伏范围内;当驱动高达5毫安时,输出在300毫伏范围内。

在模拟设备上制造,Inc.超快速互补双极(XFCB)过程中,放大器作为跟随器提供令人印象深刻的80mhz带宽,在仅800微安的电源电流下提供30v/微秒的转换速率。精心的设计使放大器在低至2.7伏的电源电压下工作。

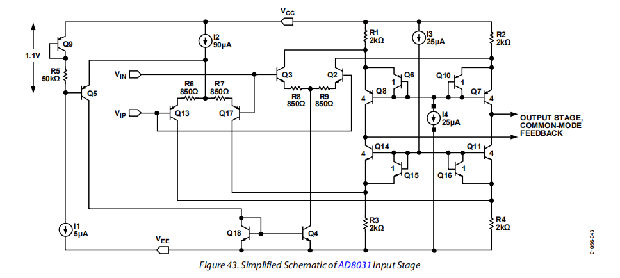

输入级操作

图43显示了输入级的简化示意图。对于正极电源内高达1.1V的共模电压(单个5V电源为0V至3.9V),尾流I2流过PNP差分对Q13和Q17。Q5被切断;没有偏置电流被传送到并联NPN差分对Q2和Q3。当共模电压在正电源的1.1V范围内驱动时,Q5打开并将尾流从PNP对路由到NPN对。在这个过渡区,放大器的输入电流改变幅度和方向。重复使用相同的尾流可以确保输入级在两个工作区域具有相同的跨导,这决定了放大器的增益和带宽。

当共模电压在正电源内被驱动超过1V时,切换到NPN对允许放大器在电源电压范围的任一端为信号提供有用的操作,并且消除在任一电源外高达500mV的输入信号的相位反转的可能性。偏移电压也会变化,以反映控制中输入对的偏移。过渡区很小,大约180毫伏。输入级的dc参数的这些突然变化可以产生对失真产生不利影响的小故障。

过度驱动输入级

应避免持续的输入差动电压大于3.4 V,因为输入晶体管可能会损坏。如果存在这种情况,建议使用输入钳位二极管。

输入对的收集器处的电压从电源轨设置为200 mV。这允许放大器在输入电压超过电源电压500毫伏时保持线性工作。驱动输入共模电压超过该点将正向偏置输入晶体管的集电极结,导致相位反转。应避免在任何时间内维持这种状态,因为当放大器处于反相时,很容易超过最大允许输入差动电压。

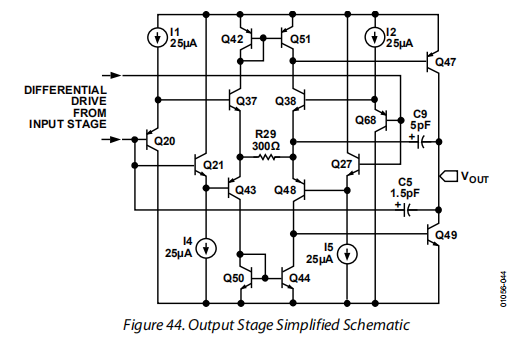

输出级、开环增益和

畸变与电源间隙

AD8031具有轨对轨输出级。输出晶体管作为公共发射极放大器工作,提供输出驱动电流以及放大器开环增益的很大一部分。

输出电压限制取决于输出晶体管需要源极或汇极多少电流。对于具有低驱动要求的应用(例如,单位增益跟随器驱动另一个放大器输入),AD8031通常在任一电压源的20毫伏范围内摆动。随着所需电流负载的增加,饱和输出电压随着:

式中:ILOAD为所需负载电流。RC是输出晶体管集电极电阻。

对于AD8031,两个输出晶体管的集电极电阻通常为25Ω。当电流负载超过15毫安的额定输出电流时,驱动输出晶体管饱和所需的基极驱动电流达到极限,放大器的输出摆幅迅速减小。

AD8031的开环增益随负载电阻近似线性下降,且取决于输出电压。开环增益保持恒定在正电源250毫伏、负电源150毫伏的范围内,然后随着输出晶体管进一步驱动至饱和而减小。

AD8031/AD8032放大器的失真性能不同于传统的放大器。通常,放大器的失真性能随着输出电压幅度的增加而降低。

作为单位增益跟随器,AD8031/AD8032的输出在峰值输出电压区域在V~-0.7v附近表现出更大的失真。这种不寻常的失真特性是由输入级结构引起的,在输入级操作部分中进行了详细讨论。

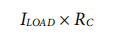

输出超速恢复

当放大器试图将输出电压驱动到超出其正常范围的水平时,就会发生放大器的输出过驱动。在消除过驱动条件后,放大器必须在合理的时间内恢复正常工作。如图45所示,AD8031/AD8032在负超速的100 ns内恢复,在正超速的80 ns内恢复。

驱动电容性负载

电容性负载与运放的输出阻抗相互作用,在反馈路径中产生额外的延迟。这会降低电路的稳定性,并可能导致不必要的振铃和振荡。当放大器使用较高的噪声增益时,给定的电容值会导致更少的振铃。

AD8031/AD8032的容性负载驱动可以通过在容性负载上串联一个低值电阻来实现。引入串联电阻有利于将电容性负载与反馈回路隔离,从而减小其影响。图46显示了串联电阻对可变电压增益的电容驱动。作为闭环增益增加,较大的相位裕度允许更大的电容负载和较少的过冲。在较低的闭环增益下加入串联电阻也能达到同样的效果。大的图46。电容负载驱动与闭环增益电容性负载时,放大器的频率响应主要由串联电阻和电容性负载的滚转决定。

应用

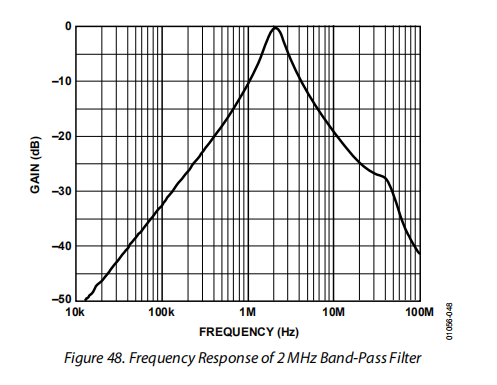

一个2mhz单电源双四路带通滤波器

图47显示了中心频率为2 MHz的单电源双四路带通滤波器电路。通过将所有三个运算放大器的非垂直输入连接到电阻分压器(由连接在5V和接地之间的两个1KΩ电阻组成),很容易产生2.5V的偏置电平。该偏置点还通过0.1μF电容器与接地分离。滤波器的频率响应如图48所示。

为了保持准确的中心频率,运算放大器必须在2兆赫有足够的环路增益。这就需要选择一个运算放大器,具有明显更高的单位增益,交叉频率。AD8031/AD8032的单位增益、交叉频率为40MHz。将开环增益乘以各个运放电路的反馈因子,得到每个增益级的环路增益。从各个运放电路的反馈网络可以看出,每个运放的环路增益至少为21db。该电平足够高,以确保滤波器的中心频率不受运放带宽的影响。例如,如果在该应用中选择增益带宽积为10 MHz的运放,则产生的中心频率将移动20%至1.6 MHz。

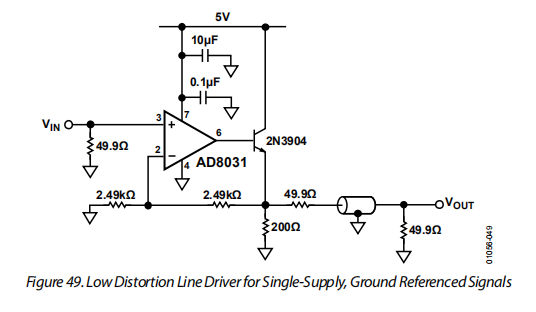

高性能单电源线驱动器

即使AD8031/AD8032在靠近两条轨道的位置摆动,但当信号在电源之间具有共模电平且每条轨道有大约500 mV的净空时,AD8031具有最佳的失真性能。如果在单电源应用中需要低失真以获得接近地面的信号,则可以在运放输出端使用发射极跟随电路。

图49显示了配置为单个电源的AD8031,gainof-2线路驱动器。当输出驱动一条后端接的50Ω线路时,从VIN到VOUT的总增益为1。除了尽量减少反射外,如果电缆短路,50Ω后端电阻还可保护晶体管免受损坏。发射器跟随器位于反馈回路内,确保来自AD8031的输出电压保持在离地约700毫伏。使用此电路,即使当输出信号摆动到离地50毫伏以内时,也可以实现低失真。电路在500khz和2mhz下进行了测试。

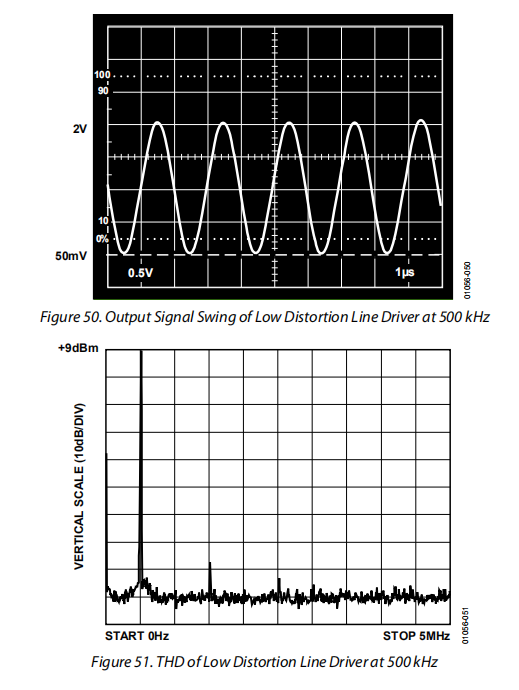

图50和图51显示了500 kHz时的输出信号摆动和频谱。在该频率下,输出信号(在VOUT处)的峰间摆动为1.95 V(50 mV至2 V),THD为-68 dB(SFDR=-77 dB)。

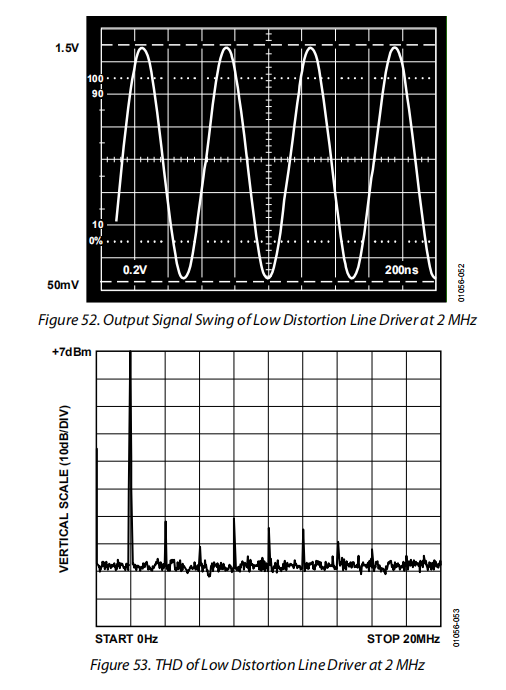

图52和图53显示了2兆赫时的输出信号摆动和频谱。正如预期的那样,在较高的频率下,信号质量会有所下降。当输出信号具有1.45 V的峰间摆动(从50 mV摆动到1.5 V)时,THD为-55 dB(SFDR=-60 dB)。

该电路还可用于驱动单电源高速ADC的模拟输入,其输入电压范围参考接地(例如,0 V至2 V或0 V至4 V)。在这种情况下,不需要后端接电阻器(假设晶体管到ADC的物理距离较短);因此,外部晶体管的发射极将直接连接到ADC输入端。因此,电路的可用输出电压摆幅将加倍。

外形尺寸