EL4585是一个PLL(锁相环)子系统

日期:2020-5-30特征

•36MHz,通用PLL

•8FSC定时(使用EL4584进行4FSC)

•与EL4583同步分离器兼容

•VCXO、Xtal或LC槽振荡器

•<2ns抖动(VCXO)

•用户控制的PLL捕获和锁定

•兼容NTSC和PAL电视格式

•8个预先编程的流行电视扫描速率时钟因子

•单5V,低电流运行

•提供无铅(符合RoHS)

应用

•像素时钟再生

•视频压缩引擎(MPEG)时钟发生器

•视频采集或数字化

•PIP(画中画)定时发生器

•文本或图形覆盖计时

水平发电机锁,8FSC

EL4585是一个PLL(锁相环)子系统,专为视频应用而设计,也适用于高达36MHz的通用用途。在视频应用中,该器件产生一个TTL/CMOS兼容像素时钟(CLK-OUT),它是电视水平扫描速率的倍数,并与之锁相。

参考信号是水平同步信号,TTL/CMOS格式,可以很容易地从带有EL4583同步分离器的模拟复合视频信号中导出。向“coast”提供输入信号,用于参考视频定时中存在周期性干扰的应用,例如VTR头切换。锁定检测器输出指示正确锁定。

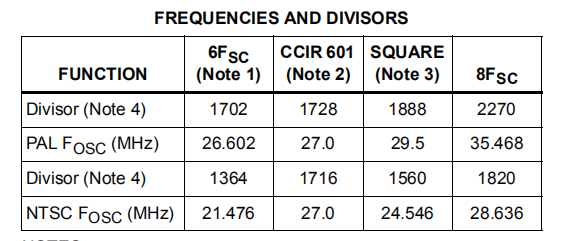

通过外部选择三个控制管脚,NTSC的分割比为四个比率,PAL视频定时标准的分割比为四个相似比率。这四个比率被选择用于常见的视频应用,包括8FSC、6FSC、27MHz(CCIR 601格式)和一些工作站图形中使用的方形图片元素。要生成4FSC、3FSC、13.5MHz(CCIR 601格式)等,请使用EL4584,它不具有EL4585的两级除法。

对于这些频率不合适的应用,或对于通用PLL应用,可以绕过内部分频器,使用外部分频链。

笔记:

1、 6FSC频率不产生整数除数。

2、 CCIR 601除数在NTSC和PAL的每行的活动部分产生1440像素。

3、 正方形像素格式为NTSC提供640像素,为PAL提供768像素。

4、 除数不包括÷2块。

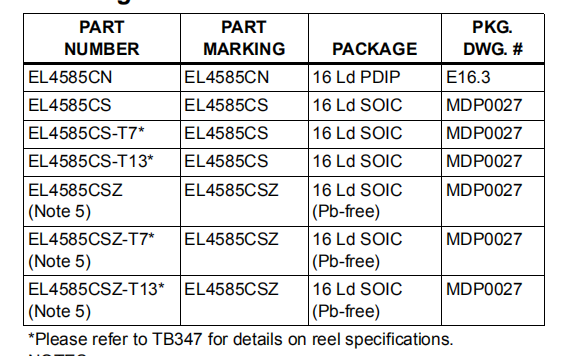

订购信息

笔记:

5、这些Intersil无铅塑料包装产品采用特殊的无铅材料组、模塑料/模具连接材料和100%哑光镀锡板加退火(e3端接处理,符合RoHS标准,并与SnPb和无铅焊接操作兼容)。Intersil无铅产品在无铅峰值回流焊温度下分类为MSL,满足或超过IPC/JEDEC J STD-020的无铅要求。

6、有关3FSC和4FSC时钟频率操作,请参阅EL4584数据表。

Pinout

时序图

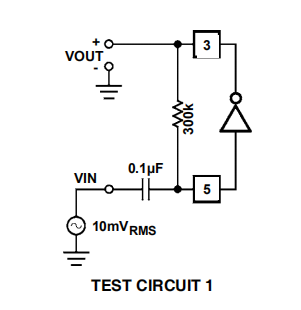

测试电路

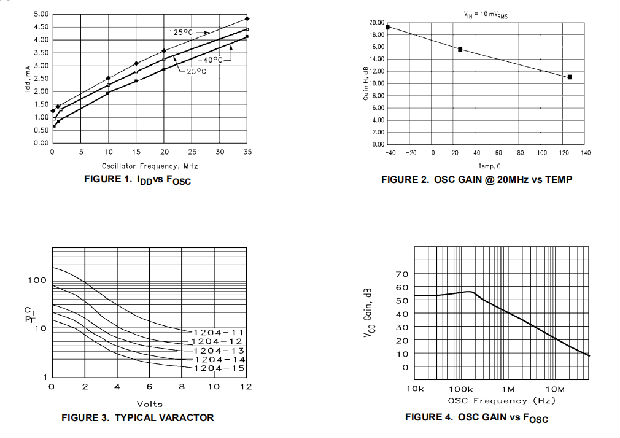

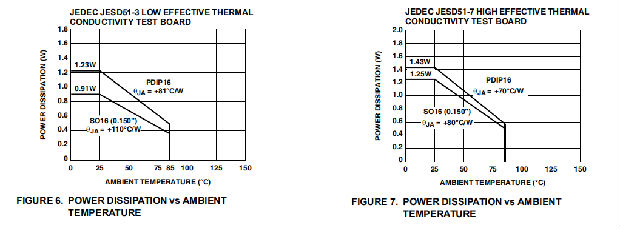

典型性能曲线

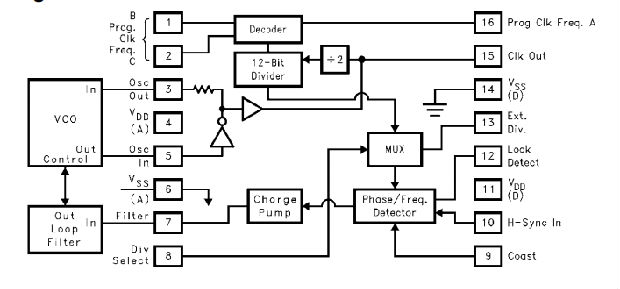

EL4585框图

操作说明

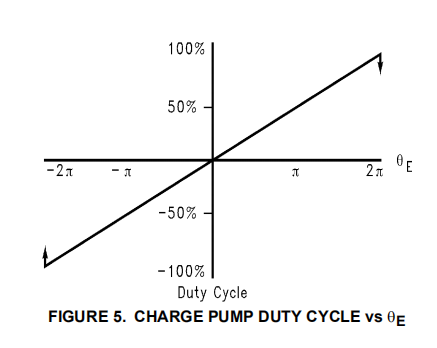

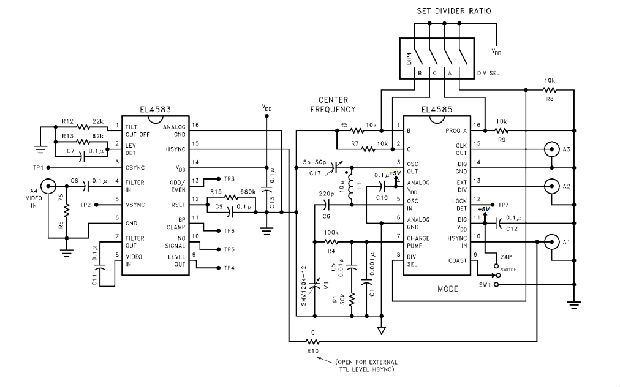

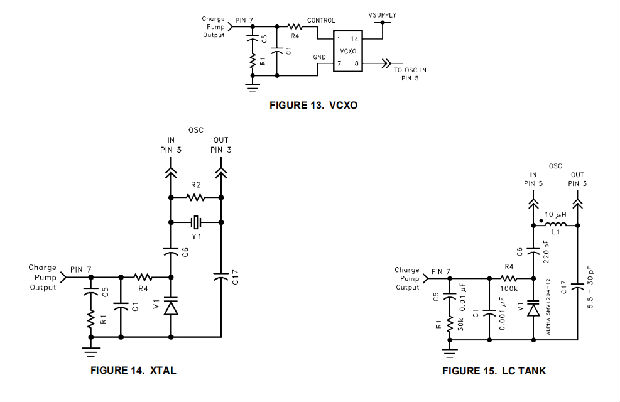

水平同步信号(CMOS电平,下降前缘)被输入到HSYNC输入(引脚10)。该信号延迟约200ns,其下降沿成为时钟输出锁定的参考(见第5页的“时序图”)。时钟由引脚5上的信号产生,OSC输入。有两种类型的VCO可用于EL4585、LC和晶体控制。此外,每种类型都可以使用离散组件(包括变容二极管作为频率控制元件)构建,或者可以购买完整的、自包含的模块以及金属罐内的所有东西。这些模块非常宽容的印刷电路板布局,但成本高于离散解决方案。VCO或VCXO用于调节时钟。LC谐振腔比晶体控制电路具有更大的“拉力”,但也更容易随时间漂移,从而产生更多的抖动。电路的“可拔性”是指通过调节VCO模块或变容管控制引脚上的电压,将振荡频率从其中心频率拉离的能力,是所用变容管或VCO模块电容电压曲线的斜率和范围的函数。VCO信号被发送到CLK out引脚,除以2,然后发送到除以N计数器。除数N由管脚1、2和16的状态确定,如表1所示。将分割后的信号连同延迟的HSYNC输入一起发送到相位/频率检测器,后者比较两个信号的相位和频率差。任何相位差在电荷泵输出端(引脚7)转换为电流。必须使用频率与控制电压正偏差的VCO。在图10和图11中,变容二极管的电容斜率与电压成负关系,随着振荡器控制电压的增加,产生正频率偏差。

VCO

当变容管上的电压为2.5V时,应调整VCO,使其振荡频率非常接近所需的时钟输出频率。VCXO和VCO模块已调整到所需频率,因此如果使用其中一个单元,则不必执行此步骤。电荷泵输出(引脚7)的输出范围为0V至5V,最大可产生或吸收约300微安的电流,因此所有频率控制都必须使用来自变容管在这个范围内。晶体振荡器比LC振荡器更稳定,后者转化为较低的抖动,但LC振荡器可以从其中点值进一步拉,从而产生更大的捕获和锁定范围。如果已知输入的水平同步信号非常稳定,则可以使用晶体振荡器电路。如果HSYNC信号的频率变化大于约300ppm,则应考虑LC振荡器,如晶体振荡器很难做到这一点。当HSYNC输入频率大于CLK频率÷2N时,电荷泵输出(pin 7)将电流输入滤波电容器,增加变容二极管上的电压,从而倾向于增加VCO频率。相反,当HSYNC频率小于CLK÷2N时,电荷泵输出从滤波电容器中拉出电流,迫使VCO频率降低。

环路滤波器

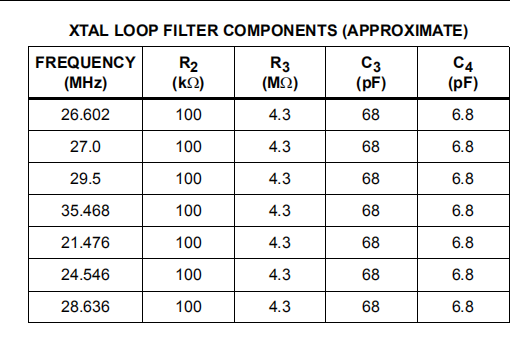

环路滤波器控制VCO对相位比较器输出刺激变化的响应速度。其元件的选择应确保能够实现快速锁定,但VCO“振荡”最小,最好是在电荷泵输出的一到两次振荡中,假设VCO频率在捕获范围内开始。如果滤波器阻尼不足,VCO将在稳定锁定发生之前,多次重复拍摄所需的工作点。有可能使滤波器阻尼过大,以致环路本身振荡,VCO锁永远无法实现。如果滤波器阻尼过大,VCO响应时间将过长,锁定条件需要多次循环。过阻尼的另一个特点是系统容易解锁,因为滤波器对VCO频率的扰动响应不够快。一个严重过阻尼的系统似乎会无休止地振荡,就像长摆末端的一个非常大的质量。由于PCB迹线和元件变量的寄生效应,要确定在任何给定情况下使用的最佳值,需要进行一些反复试验。使用组件表作为起点,但要注意,与这些值的偏差并非异常。

外部分水岭

DIV SEL(引脚8)控制内部分隔器的使用。高电平时,内部分频器启用,外部分频器(引脚13)输出CLK out除以2N。这是水平同步输入将锁定的信号。当除法选择低时,内部除法器输出被禁用,外部除法器成为外部除法器的输入,因此可以使用除8个预先编程的内部除法器之一之外的除法器。

正常模式

通过将COAST(针脚9)拉低启用正常模式(低于1/3*VCC)。如果HSYNC和CLK÷2N具有任何相位或频率差,则产生错误信号并发送到电荷泵。电荷泵将迫使电流进入或流出滤波电容器,以尝试调制VCO频率。调制将继续,直到CLK÷2N的相位和频率与HSYNC输入完全匹配。当相位和频率匹配时(相位偏移是VCO特性的函数),误差信号归零,锁定检测不再脉冲高,电荷泵进入高阻抗状态。时钟现在锁定到HSYNC输入。只要相位和频率差保持较小,锁相环就可以调节VCO保持锁定,锁定检测保持较低。

快速锁定模式

快速锁定模式可通过允许滑行浮动或将其拉至中间供电(在1/3和2/3*VCC之间)来启用。在这种模式下,锁的实现要比正常模式快得多,但时钟除数会被动态修改以实现这一点。如果相位检测器检测到足够大的误差,时钟将被抑制或重置以尝试信号的“快速锁定”。强制时钟以这种方式同步到HSYNC输入允许锁定大约2小时周期,但在此期间时钟间隔将不规则。一旦达到接近锁定状态,充电泵输出应非常接近其锁定值,将设备置于正常模式应非常快导致正常锁定。在HSYNC变得不规则的地方使用快速锁定模式,直到再次获得稳定信号。

滑行模式

通过将Coast(针脚9)拉高(高于2/3*VCC)来启用Coast(滑行)模式。在滑行模式下,内部相位检测器被禁用,滤波器输出保持在高阻抗模式,以尽可能保持滤波器输出电压和VCO频率恒定。VCO频率会随着滤波器电容的电荷泄漏而漂移,电压会改变VCO的工作点。当噪声或信号降级导致许多周期的水平同步丢失时,可使用滑行模式。鉴相器不会尝试调整信号的丢失,以便在水平同步返回时,可以快速重新建立同步锁。但是,如果VCO发生了很大的漂移,重新锁定可能需要与重新启动时一样长的时间。

锁定检测

锁定检测(引脚12)将在锁定建立时变低。从电荷泵输出的任何直流电流路径都将相对于HSYNC输入倾斜EXT DIV,倾向于偏移或增加200ns的内部延迟,这取决于额外电流的流动方式。这种偏移称为静态相位误差,在任何锁相环系统中都存在。如果部件在锁定模式下稳定,则锁定检测不低,则从环路滤波器串联电阻R2中加上或减去将改变该静态相位误差,以允许LDET在锁定时变低。目标是使EXT DIV的上升沿与HSYNC+200ns的下降沿同步(见第5页的“时序图”)。增大R2减小相位误差,减小R2增大相位误差。(当EXT DIV滞后于HSYNC时,相位误差为正。)所需电阻取决于VCO设计或VCXO模块选择。

应用程序信息

选择外部组件

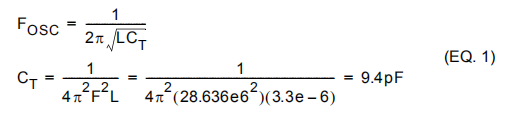

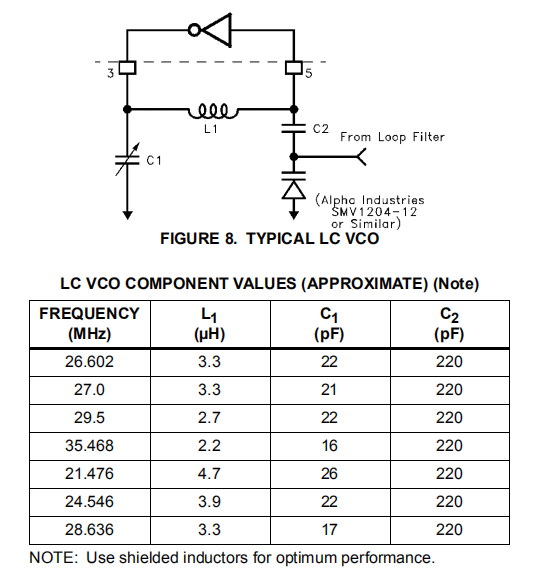

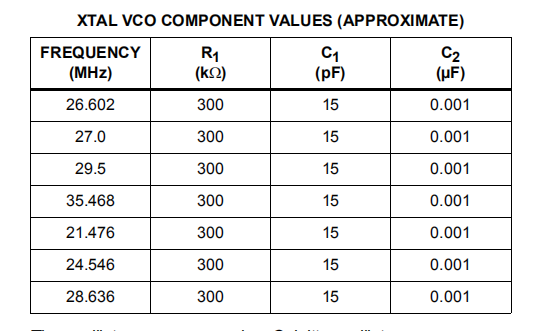

1、要选择LC VCO组件,首先选择所需的工作频率。在我们的例子中,我们将使用28.636MHz,HSYNC频率为15.734kHz。

2、选择一个合理的电感值(1至5μH工作良好)。我们选择3.3μH。

3、计算生产FOSC所需的CT。

4、从变容二极管数据表中,找到2.5V时所需的锁定电压CV。例如,我们的SMV1204-12的CV=23pF。

5、C2应该是10CV左右,所以我们选择C2=220pF作为例子。

6、计算C1。自:

然后:

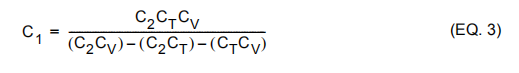

在我们的例子中,C1=17pF。(微调电容器可用于微调。)使用内部分频器的每个频率的示例如图8所示。

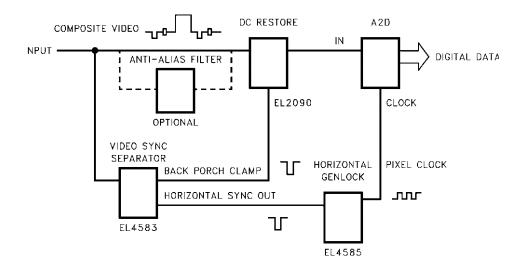

典型应用

水平genlock为模数转换器提供时钟,将模拟视频数字化。

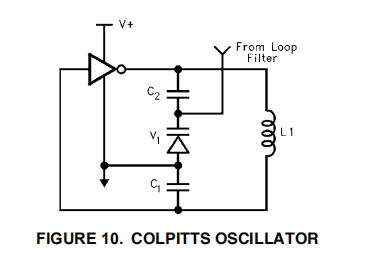

振荡器布置为Colpitts振荡器(见图8),此处重新绘制结构,以强调Colpitts振荡器中使用的分裂电容。应该注意的是,这种振荡器配置只是字面上数百种可能之一,这里显示的配置不一定代表所有应用程序的最佳解决方案。晶体制造商是在各种应用中设计和使用振荡器的信息来源,鼓励读者熟悉它们。

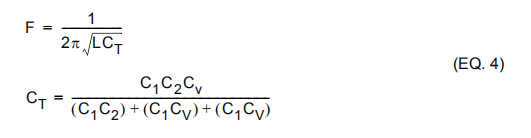

C1是用来调节中心频率的,C2 DC将控制与振荡器隔离开来,V1是主要的控制设备。C2应该比CV大得多,这样V1具有最大的调制能力。振荡频率由方程式4给出:

选择回路滤波器组件

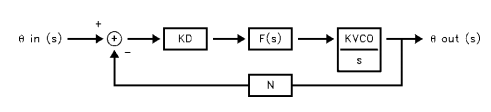

PLL、VCO和环路滤波器可以描述为:

式中:Kd=相位探测器增益(A/rad)

F(s)=环路滤波器阻抗(V/A)

KVCO=VCO增益(rad/s/V)

N=总内因子或外因子(见下文3)

可以看出,对于等式5所示的环路滤波器:

式中,ωn=环路滤波器带宽,ζ=环路滤波器阻尼因子。

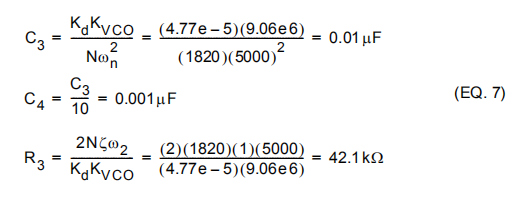

1、 对于EL4585,Kd=300μA/2πrad=4.77e-5A/rad。

2、 环路带宽应为HSYNC频率/20,阻尼比应为1,以获得最佳性能。以我们为例,ωn=15.734kHz/20=787Hz≈5000 rad/S。

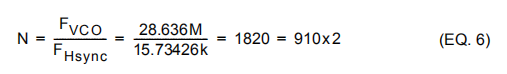

3、 表1中的N=910x2=1820。

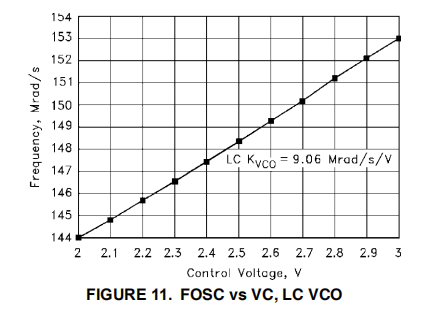

4、KVCO表示施加在控制管脚上的每伏电压的VCO频率变化量。假设(但可能不是)与锁定点(2.5V)呈线性关系。其值取决于VCO配置和变容管传递函数CV=F(VC),其中VC是反向偏压控制电压,CV是变容管电容。由于F(VC)是非线性的,所以最好建立一个VCO,测量KVCO约2.5V,测量结果如下。曲线的斜率由线性回归技术确定,等于KVCO。在我们的例子中,KVCO=9.06mrad/s/V。

5、现在我们可以解方程7中的C3、C4和R3:

为了方便起见,我们选择R3=43kΩ。

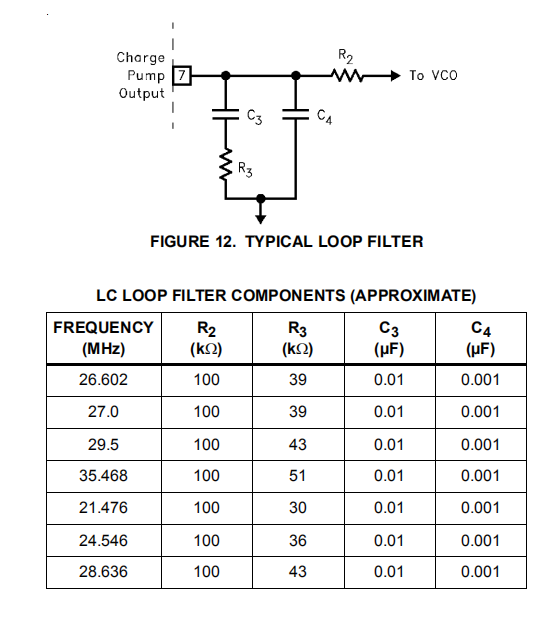

6、注意R2对环路滤波器的设计几乎没有影响。R2应该很大,在100k左右,并且可以调整以补偿锁定时的任何静态相位误差Tθ,但是如果调得太大,将减慢环路响应。如果R2变小,Tθ(见第5页的“时序图”)增大,如果R2增大,Tθ减小。锁处LDET低,| Tθ|<50ns。C4主要用于衰减电荷泵的高频噪声。这些组件对锁定的影响如图12所示。

锁定时间

设T=R3C3。随着T的增加,阻尼增加,但锁定时间也增加。减小T可以减小阻尼,加快回路响应,但会增加过冲,从而增加锁定前的振荡次数。

临界阻尼(ζ=1)发生在最小锁定时间。由于阻尼降低也会降低环路稳定性,因此有时需要设计稍微过阻尼(ζ>1),用锁定时间来增加稳定性。

PCB布局注意事项

强烈建议在布局中使用电源和接地平面。振荡器和滤波器部分构成反馈回路,因此必须注意避免任何反馈信号影响振荡器,控制输入除外。整个振荡器/滤波器部分应被铜接地包围,以防止来自附近信号的不必要影响。为模拟和数字电源使用单独的路径,使模拟(振荡器部分)尽可能短且无杂散信号。必须注意正确的旁路。保持导线长度较短,并将旁路盖尽可能靠近电源引脚。如果要为VCO部分使用分立元件布置PCB,必须注意避免OSC引脚3和5处的寄生电容,并将其滤除(引脚7)。移除这些轨迹上方和下方的接地和电源平面铜,以避免与它们进行电容连接。还建议将振荡器部分封装在屏蔽笼内,以减少对VCO的外部影响,因为它们往往对“手摇”影响非常敏感,LC品种比晶体控制振荡器更敏感。一般来说,工作频率越高,这些考虑就越重要。独立的VCXO或VCO模块已经安装在屏蔽笼中,因此在布局上不需要太多考虑。许多晶体制造商出版了关于振荡器的使用和布局的资料性文献,这应该是有帮助的。

EL4585/4演示板

EL4583/4/5演示板的VCO和环路滤波器部分可以通过以下配置实现:

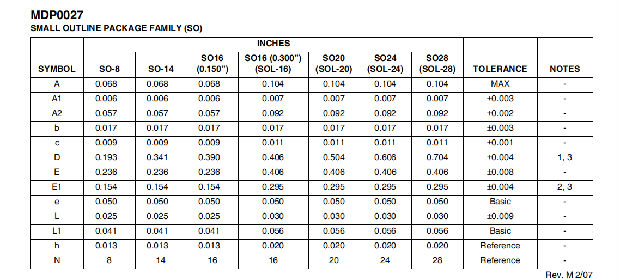

小外形包装系列(SO)

注:

1、不包括每侧最大0.006“的塑料或金属突出物。

2、不包括每侧最大0.010“的塑料内螺纹突出部分。

3、尺寸“D”和“E1”在基准面“H”处测量。

4、尺寸和公差符合ASME Y14.5M-1994。

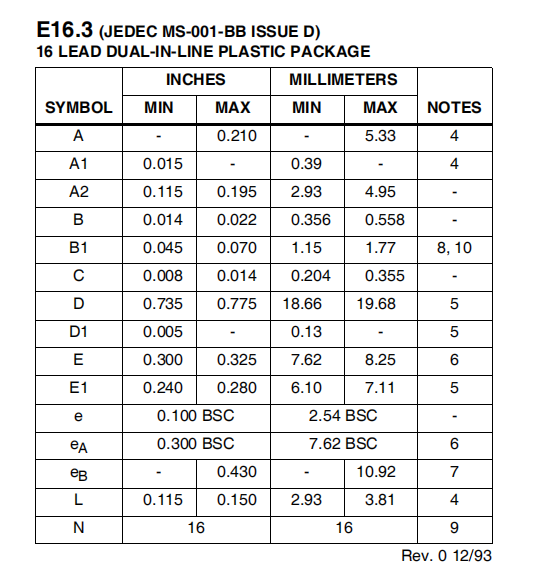

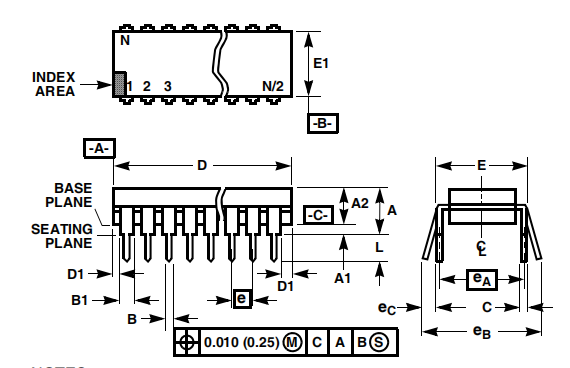

双列直插式塑料包装(PDIP)

笔记:

1、控制尺寸:英寸。如果英制尺寸和公制尺寸之间存在冲突,则以英制尺寸为准。

2、尺寸和公差符合ANSI Y14.5M-1982。

3、符号定义见第95号出版物第2.2节“MO系列符号列表”。

4、尺寸A、A1和L是在机组位于JEDEC座面规GS-3中时测量的。

5、D、 D1和E1尺寸不包括模具飞边或突出物。模子飞边或突出物不得超过0.010英寸(0.25毫米)。

6、E和eA的测量引线必须与基准面C-垂直。

7、eB和eC在引线末端测量,引线不受约束。eC必须为零或更大。

8、B1最大尺寸不包括坝筋突出。坝条突出物不得超过0.010英寸(0.25毫米)。

9、N是终端位置的最大数目。

10、E8.3、E16.3、E18.3、E28.3、E42.6的拐角导线(1、N、N/2和N/2+1)的B1尺寸为0.030-0.045英寸(0.76-1.14毫米)。