LMX2335/LMX2336/LMX2337 血小板™ 射频双频合成器

日期:2020-9-12LMX2335 1.1千兆赫/1.1千兆赫

LMX2336 2.0千兆赫/1.1千兆赫

LMX2337 550兆赫/550兆赫

一般说明

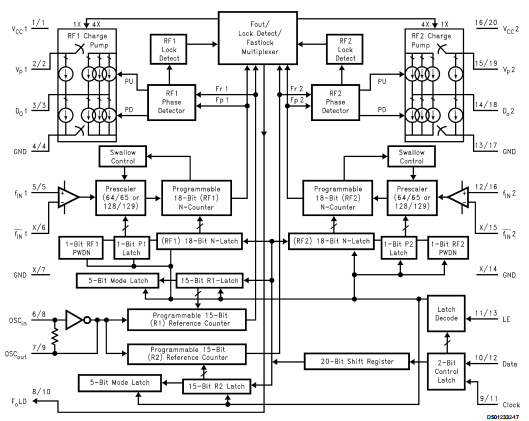

LMX2335、LMX2336和LMX2337是单片集成双频合成器,包括两个高频预分频器,设计用于需要两个射频锁相环的应用。它们是用国家的ABiC IV硅BiCMOS工艺。LMX2335/36/37包含两个双模预分频器。可以为每个RF选择64/65或128/129预分频器合成器。第二个参考分隔链包括在改善系统噪音的集成电路。LMX2335/36/37,其中采用数字锁相环技术,结合一个高质量的参考振荡器和环路滤波器,提供电压控制振荡器产生的调谐电压非常稳定的低噪声射频本振信号。串行数据通过3传输到LMX2335/36/37有线接口(数据、启用、时钟)。电源电压can范围从2.7V到5.5V。LMX2335/36/37的特点是低电流消耗;3V时LMX2335/37−10 mA,LMX2336−13 mA,3V电压。LMX2335/37可在JEDEC SO和TSSOP 16针表面贴装塑料包裹。LMX2336采用TSSOP 20针表面贴装塑料包装。

特征

2.7V至5.5V操作

低电流消耗

可选断电模式:ICC=1μA(典型值)

双模预分频器:64/65或128/129

可选电荷泵TRI-STATE®模式

可选电荷泵电流电平

可选快速锁™ 模式

应用

蜂窝电话系统(AMPS、ETAC、RCR-27)

无绳电话系统(DECT、ISM、PHS、CT-1+)

个人通信系统(DCS-1800,PCN-1900)

双模PC电话

有线电视

其他无线通信系统

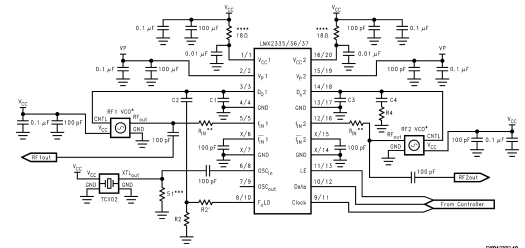

注:VCC1向RF1预分频器、N计数器、R计数器和相位检测器供电。VCC2向RF2预分频器、N计数器、相位供电检测器、R-计数器和OSCin缓冲液、MICROWIR

绝对最大额定值(注1、2)

如果需要军用/航空航天专用设备,

请联系国家半导体销售办公室/

经销商的可用性和规格。

电源电压

VCC−0.3V至+6.5V

VP−0.3V至+6.5V

任何引脚上的电压

接地=0V(VI

)-0.3V至VCC+0.3V

储存温度范围(TS)−65°C至+150°C

铅温度(焊料4秒)(TL)+260˚C

建议操作

条件

电源电压

VCC 2.7V至5.5V

VP VCC至+5.5V

工作温度(TA)−40°C至+85°C

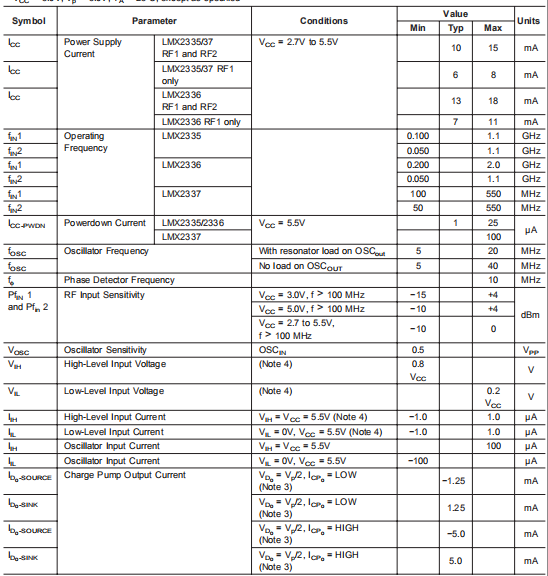

电气特性

VCC=5.0伏,Vp=5.0伏;TA=25摄氏度,除非另有规定

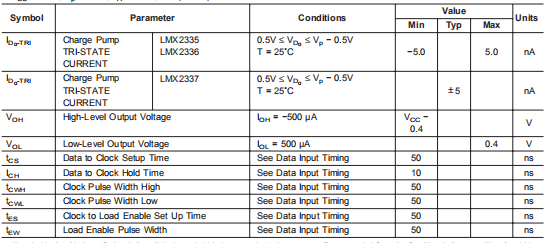

电气特性(续)

VCC=5.0伏,Vp=5.0伏;TA=25摄氏度,除非另有规定

注1:绝对最大额定值表示设备可能发生损坏的极限值。建议的操作条件表明该设备旨在发挥功能,但不保证特定的性能限制。有关保证的规格和测试条件,请参阅电气特性。保证规格仅适用于列出的试验条件。

注2:本装置为高性能射频集成电路,ESD额定值<2 keV,对ESD敏感。本设备的搬运和组装在防静电工作站进行。

注3:ICPo说明见可编程模式。

注4:时钟、数据和LE不包括fIN1、fIN2和OSCin。

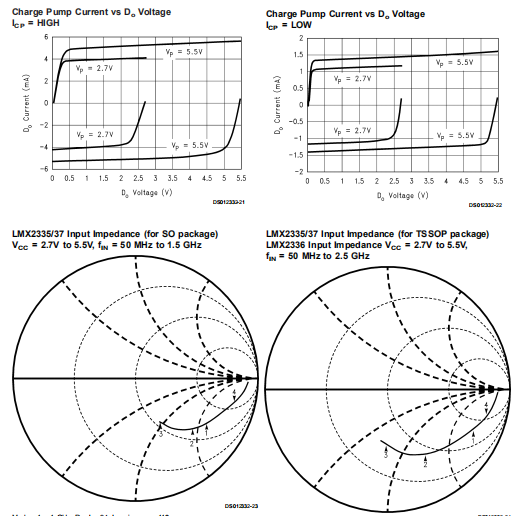

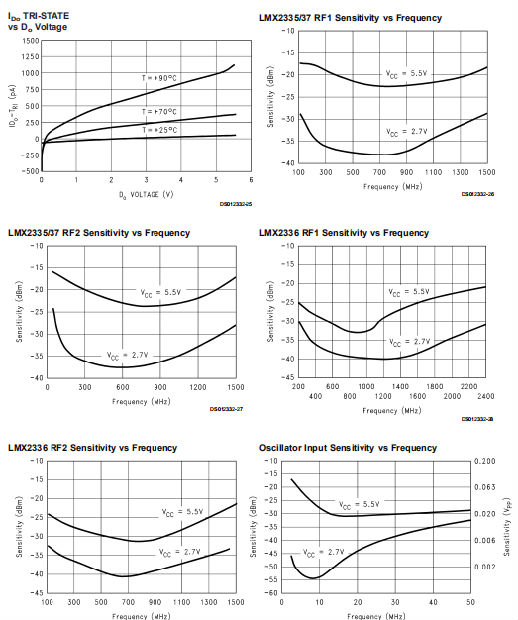

典型性能特征(续)

标记1=1 GHz,实数=94,虚值=−118

标记2=1.2 GHz,实数=72,虚值=−88

标记3=1.5 GHz,实数=53,虚值=−45

标记4=500 MHz,实数=201,虚值=−224

标记1=1 GHz,实=97,虚=146

标记2=1.89 GHz,实数=43,虚值=−67

标记3=2.5 GHz,实数=30,虚值=−33

标记4=500 MHz,实数=189,虚值=−233

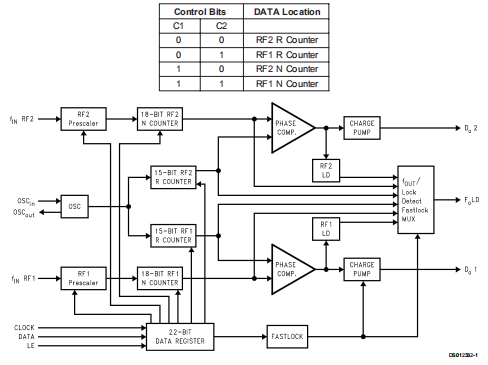

功能描述

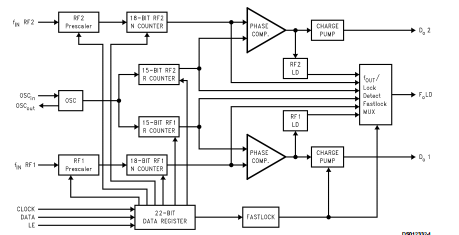

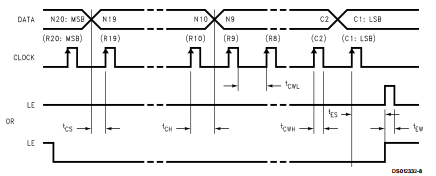

下面的简化框图显示了22位数据寄存器、两个15位R计数器和两个18位N计数器(中间闩锁未显示)。数据流被时钟(在时钟上升沿)进入数据寄存器,MSB优先。存储的数据在移位寄存器中,被加载到LE上升沿上的4个适当的锁存器中的一个。最后两位是控制位。数据按如下方式传输到计数器:

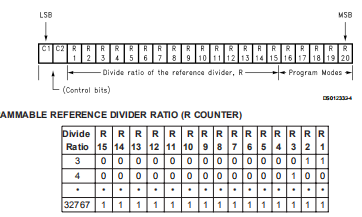

可编程参考分压器(RF1和RF2 R计数器)

如果控制位为00或01(RF2为00,RF1为01),则数据从22位移位寄存器传输到一个15位R计数器。串行数据格式如下所示。

注:禁止分割比小于3。

分流比:3:32767

R1到R15:这些位选择可编程参考分频器的分频比。

数据首先在MSB中移位。

功能描述(续)

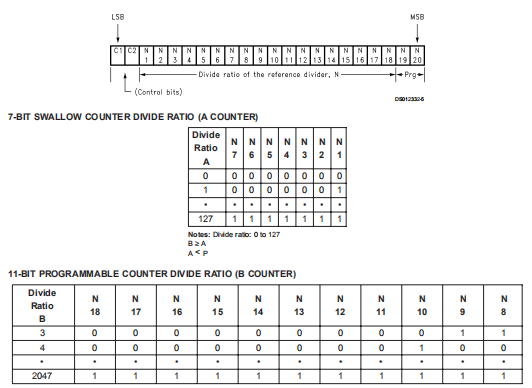

可编程分频器(N计数器)

每个N计数器由7位燕子计数器(A计数器)和11位可编程计数器(B计数器)组成。如果控件位为10或11(10用于RF2计数器,11用于RF1计数器)数据从20位移位寄存器传输到7位锁存器(设置吞咽(A)计数器)和11位锁存器(设置11位可编程(B)计数器),MSB优先。串行数据格式如下所示。

注:分流比:3~2047(禁止小于3的分流比)

脉冲吞咽功能

fVCO=[(P x B)+A]x fOSC/R

fVCO:外部压控振荡器(VCO)的输出频率

B: 二进制11位可编程计数器(3至2047)的预置分频比

A: 二进制7位燕子计数器预置分频比(0≤A≤P;A≤B)

fOSC:外部参考频率振荡器的输出频率

R: 二进制15位可编程参考计数器(3至32767)的预置分频比

P: 双模预分频器预置模(P=64或128)

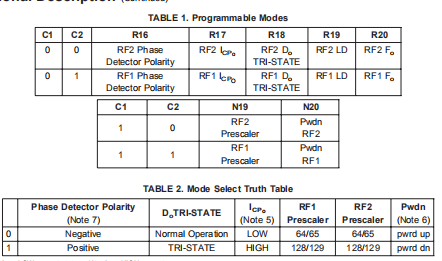

可编程模式

可以用位R16–R20编程多种操作模式,包括相位检测器极性、电荷泵三态以及折叠针的输出。使用位N19和N20选择预分频器和断电模式。可编程模式如表1所示。可编程模式和折叠输出的真值表如表2、3所示。

注5:ICPo低电流状态=1/4 x ICPo大电流。

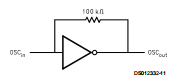

注6:激活RF2 PLL或RF1 PLL断电模式会导致禁用相应的N计数器除法器并使其各自的fIN输入减记(高阻抗状态)。断电功能由电荷泵选通以防止不必要的频率跳变。一旦断电程序模式加载后,当电荷泵达到三态状态时,部件将进入断电模式。R计数器和振荡器功能不变成在RF2和RF1断电位激活之前禁用。OSCin通过100 kΩ电阻器连接到VCC,当该条件存在时,OSCin变高。MICROWIRE控制寄存器保持激活状态,能够在所有断电模式下加载和锁定数据。

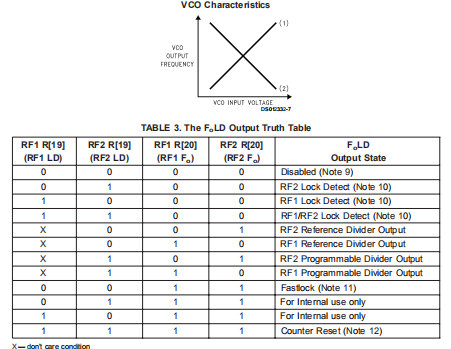

注7:相位检测器极性相应地,应根据VCO的特性设置位:当压控振荡器特性为正(1)时,R16应设为高当VCO特性如(2)为负时,应将R16设为低。

功能描述(续)

注9:当折叠输出被禁用时,它被主动拉至低逻辑状态。

注10:锁定检测输出用于指示VCO频率何时处于“锁定”状态。当环路被锁定并且选择了锁定检测模式时,管脚输出高,窄脉冲低。在RF1/RF2锁定检测模式下,当RF2和RF1都锁定时,将指示锁定状态。

注11:Fastlock模式在Fastlock操作期间利用折叠输出引脚将第二个环路滤波器阻尼电阻器切换至接地。激活Fastlock每当RF环路的Icpo幅值位#17选择为高(而#19和#20模式位被设置为Fastlock)时发生。

注12:计数器复位模式位R19和R20时,激活重置所有计数器。移除复位位后,N计数器以“关闭”状态继续计数与R计数器对齐。(最大误差为一个预分频器周期)。如果复位位被激活,R计数器也将被强制复位,从而允许通电时平滑的交流采集。

注:括号内的数据表示可编程参考分压器数据。

数据在时钟上升沿移入寄存器。数据首先在MSB中移位。

测试条件:使用VCC/2左右的对称波形测试串行数据输入时序。测试波形的边缘速率为0.6V/ns2.2V@VCC=2.7V和2.6V@VCC=5.5V的振幅。

操作说明:

1.压控振荡器假定为交流耦合。

2.RIN增加了阻抗,使得VCO输出功率被提供给负载而不是PLL。典型值为10Ω至200Ω,取决于VCO功率水平。鳍射频阻抗范围为40Ω至100Ω。如果阻抗较大,则为鳍。

3.50Ω终端通常用于测试板上,以允许使用外部参考振荡器。对于大多数典型产品a采用CMOS时钟,无需端接电阻。OSCin可以是交流或直流耦合的。建议使用交流耦合,因为输入电路提供自己的偏置。(见下图)。

4.建议在VCC线路上增加RC滤波器,以减少环路到环路的噪声耦合

应用提示:

正确使用接地和旁路电容器是实现高水平性能的关键。小心板可以减少引脚间的串扰布局。这是一种静电敏感装置。只能在无静电的工作站上处理。

申请信息

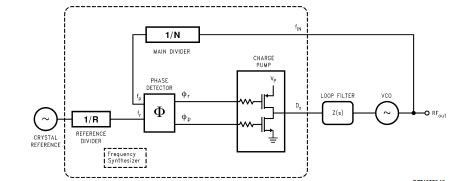

基本锁相环的框图如图1所示。

申请信息(续)

环路增益方程

相位反馈线性控制系统模型锁定状态下的PLL如图2所示。开环增益是相位比较器增益(Kφ)的乘积VCO增益(KVCO/s),环路滤波器增益Z(s)除以反馈计数器模的增益(N)。被动的使用的循环过滤器配置如图3所示,而滤波器的复阻抗如式(2)所示

从方程(3)可以看出,相位项与单极和零无关,因此相位裕度由方程式(5)确定。φ(ω)=tan−1(ωT2)−tan−1(ωT1)+180˚C

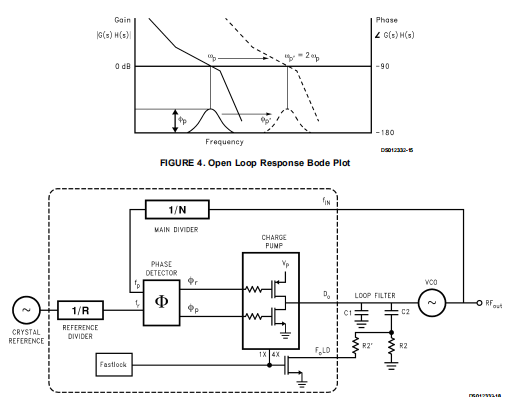

稳定性的G(s)H(s)的大小和相位图循环,如图4所示,带有一个实跟踪。参数φp表示该点存在的相位裕量增益下降到零以下(截止频率wp循环)。在临界阻尼系统中,相量边缘大约是45度。如果我们现在重新定义截止频率wp'双倍于我们原来的环路带宽wp的频率,环路响应时间大约为减半。由于比较频率下的滤波器衰减也会减小,杂散将增加大约6分贝。在提议的Fastlock方案中将存在更高的杂散电平和更宽的环路滤波器条件只有在初始锁定阶段-只要足够长的时间更快地获得锁定的好处。目标是打开环路带宽,但不引入任何额外的带宽与我们最初的设计有关的复杂或妥协标准。理想情况下,我们希望暂时改变曲线图4切换到不同的截止频率,由虚线,不影响相对开环增益和相位关系。在原截止频率的两倍处保持相同的增益/相位关系增益和相位方程(5)、(6)必须用相应的“1/w”或“1/w2”进行补偿“因素。考试式(3),(4),(5)表示阻尼电阻变量R2可选择用“w”项进行补偿相位裕度。这意味着另一个相等的电阻在初始锁定期。我们还必须确保开环增益H(s)G(s)在wp’处等于零=工作包2。KVCO、Kφ、N或这些术语的净积可以是改变因子4,以抵消w2项的存在在方程式(3)、(4)的分母中。Kφ项是选择完成转换是因为它可以易于在1X和4X值之间切换。这是通过增加电荷泵输出电流来实现的从标准模式下的1 mA到Fastlock中的4 mA。

快锁电路实现

图5示出了在钠族半导体LMX2335/36/37 PLL中实现的Fastlock方案的示意图。当一个新的频率被加载,并且RF1 ICPo位如果设置为高,则电荷泵电路接收到一个输入,使其每单位相位误差为正常电流的4倍第二个R2中的开漏NMOS片上设备开关电阻元件接地。用户计算循环过滤器正常稳态下的分量值应考虑。设备配置确保只要第二个相同的阻尼电阻器适当接线,在不考虑任何额外的稳定性因素的情况下,环路将更快地锁定。一旦锁定在正确的频率上,用户可以将锁相环恢复到标准低噪声通过发送带有RF1 ICPo位设置低。此转换不会影响在环路滤波器电容器上充电,并与电荷泵输出同步。这就产生了一个Fastlock和标准模式之间的无缝切换