ADF4110/ADF4111/ADF4112/ADF4113的应用程序详细解析

发布日期:2025-04-14

应用程序部分

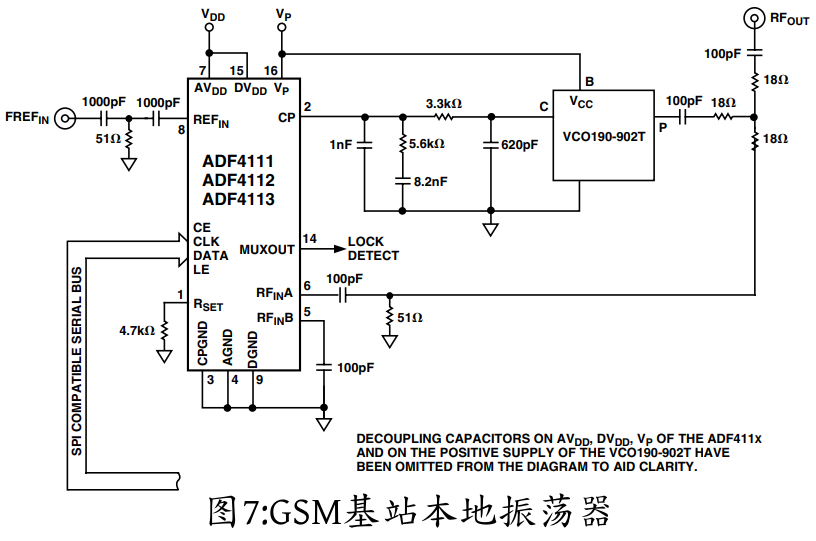

GSM基站发射机本地振荡器

下图显示了ADF4111/ADF4112/ADF4113与VCO一起使用,为GSM基站发射机产生LO。参考输入信号被施加到FREFIN处的电路,在这种情况下,其端接为50Ω。典型的GSM系统将有一个13 MHz的TCXO驱动参考输入,而没有任何50ℰ的端接。为了具有200 kHz的信道间隔(GSM标准),必须使用ADF4111/ADF4112/ADF4113的片上参考分频器将参考输入除以65。

ADF4111/ADF4112/ADF4113的电荷泵输出(引脚2)驱动环路滤波器。在计算循环滤波器组件值时,需要考虑许多项目。在这个例子中,环路滤波器的设计使得系统的整体相位裕度为45度。其他PLL系统规格包括:

KD=5毫安

KV=12MHz/V

环路带宽=20 kHz

频率频率=200 kHz

N=4500

额外参考杂散衰减=10 dB

所有这些规格都需要并用于得出图7所示的环路滤波器组件值。环路滤波器输出驱动VCO,VCO又反馈到PLL合成器的RF输入端,并驱动RF输出端。T电路配置在VCO输出、RF输出和合成器的RFIN端子之间提供50Ω匹配。

在PLL系统中,了解系统何时锁定非常重要。在图7中,这是通过使用来自合成器的MUXOUT信号来实现的。可以对MUXOUT引脚进行编程,以监测合成器中的各种内部信号。其中之一是LD或锁定检测信号。

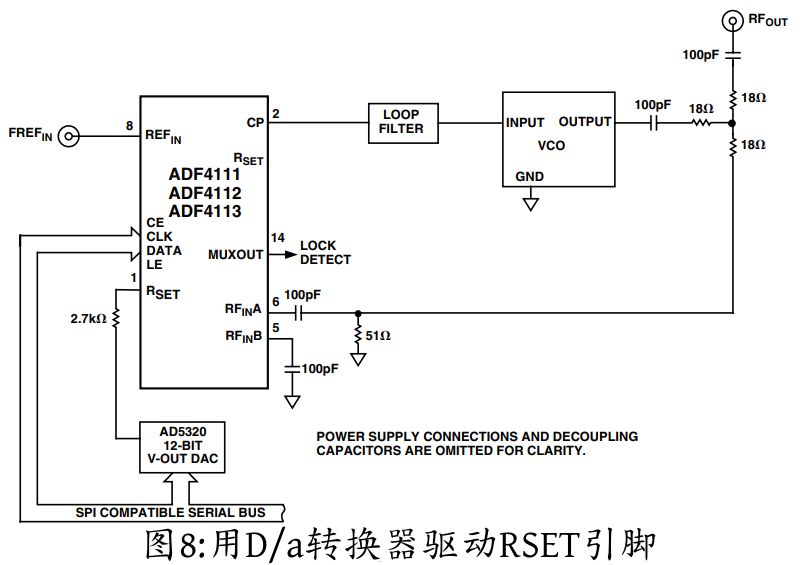

用D/A转换器驱动RSET引脚

您可以使用D/a转换器来驱动ADF4110系列的RSET引脚,从而提高对电荷泵电流ICP的控制水平。这在VCO的灵敏度在调谐范围内变化的宽带应用中是有利的。为了补偿这一点,可以改变ICP以保持良好的相位裕度并确保环路稳定性。见图8。

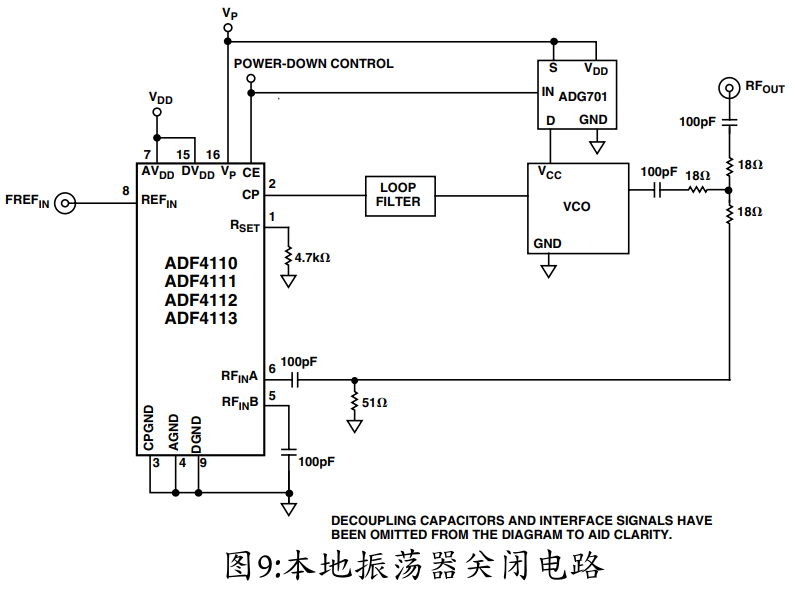

停机电路

图9中的附加电路显示了如何关闭ADF4110系列和随附的VCO。当逻辑1应用于IN输入时,ADG701开关闭合。低成本开关有SOT-23和micro-SO两种封装。

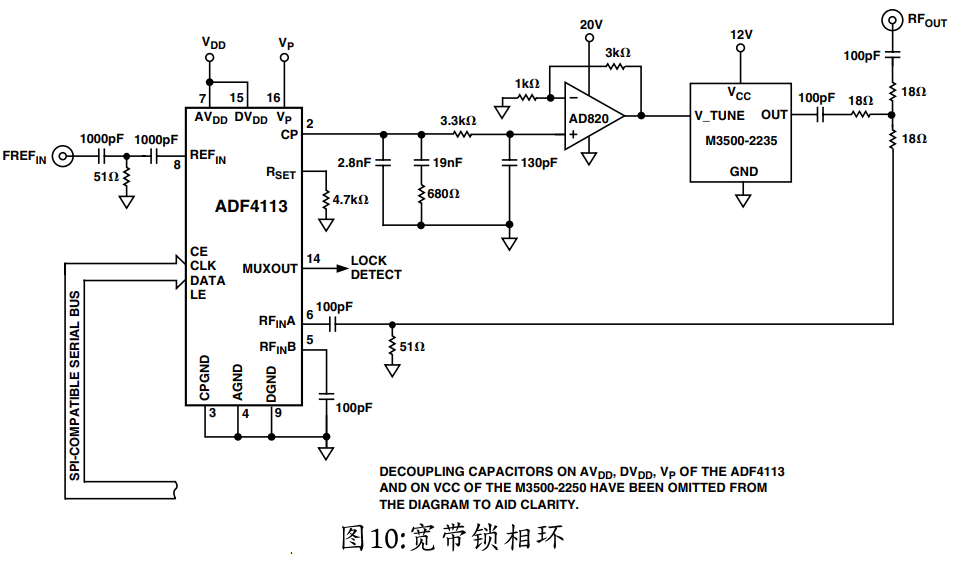

宽带锁相环

PLL中合成器和VCO的许多无线应用本质上都是窄带的。这些应用包括各种无线标准,如GSM、DSC1800、CDMA或WCDMA。在每种情况下,本地振荡器的总调谐范围都小于100 MHz。然而,也有低频带应用,其中本地振荡器可以具有高达倍频程的调谐范围。例如,有线电视调谐器的总范围约为400 MHz。图10显示了一个应用程序,其中ADF4113用于控制和编程Micronetics M3500-2235。环路滤波器设计用于2900 MHz的RF输出、40 kHz的环路带宽、1 MHz的PFD频率、10 mA的ICP(2.5 mA合成器ICP乘以4的增益因子)、90 MHz/V的VCO KD(M3500-2235在2900 MHz输出时的灵敏度)和45°C的单相裕度。

在窄带应用中,输出频率通常变化很小(通常小于10%),VCO灵敏度在该范围内也有很小的变化(通常为10%至15%)。然而,在宽带应用中,这两个参数的变化要大得多。例如,在图10中,标称2.9 GHz的射频输出变化为-25%和+17%。VCO的灵敏度可以从120 MHz/Vat 2750 MHz变化到3400 MHz时的75 MHz/V(+33%,-17%)。这些参数的变化将改变环路带宽。这反过来会影响稳定性和锁定时间。通过更改可编程ICP,可以对这些变化的回路条件进行补偿,并确保回路始终在接近最佳条件的情况下运行。

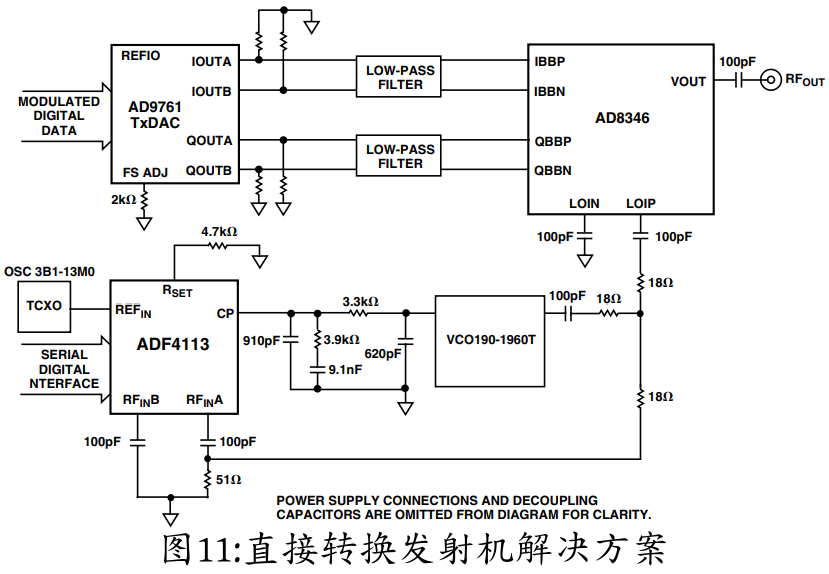

直接转换调制器

在某些应用中,直接转换架构可用于基站发射机。图11显示了ADI可用于实现此解决方案的组合。

电路图显示AD9761与AD8346一起使用。使用双集成DAC,如具有指定±0.02 dB和±0.004 dB增益和偏移匹配特性的AD9761,可确保信号链这部分的误差贡献(超温)最小。

本地振荡器(LO)使用ADF4113实现。在这种情况下,OSC 3B1-13M0提供稳定的13 MHz参考频率。该系统设计用于200 kHz的信道间隔和1960 MHz的输出中心频率。

目标应用是WCDMA基站发射机。该LO的典型相位噪声性能为-85 dBc/Hz,偏移1 kHz。

AD8346的LO端口以单端方式驱动。LOIN通过100 pF电容器交流耦合到地,LOIP通过交流耦合电容器从50Ω电源驱动。LO驱动电平需要在-6dBm和-12dBm之间。图11的电路给出了-8dBm的典型电平。射频输出设计用于驱动50Ω负载,但必须如图11所示进行耦合。如果I和Q输入由2 V p-p信号正交驱动,则产生的输出功率约为-10 dBm。

接合

ADF4110系列有一个简单的SPI兼容串行接口,用于写入设备。SCLK、SDATA和LE控制数据传输。当LE(锁存启用)变高时,已时钟记录在SCLK每个上升边缘的输入寄存器中的24位将被传输到相应的锁存器。时序图见图1,锁存真值表见表I。

最大允许串行时钟速率为20 MHz。这意味着设备可能的最大更新速率为833 kHz,或者每1.2微秒更新一次。对于典型锁定时间为数百微秒的系统来说,这当然绰绰有余。

ADuC812接口

图12显示了ADF4110系列和ADuC812微转换器之间的接口。由于ADuC812基于8051内核,因此该接口可以与任何基于8051的微控制器一起使用。微转换器设置为SPI MasterMode,CPHA=0。为了启动操作,将驱动LE的I/O端口设置为低电平。ADF4110系列的每个锁存器都需要一个24位字。这是通过将三个8位字节从微转换器写入设备来实现的。当写入第三字节时,LE输入应调高以完成传输。

首次向ADF4110系列供电时,需要三次写入(R计数器锁存器、N计数器锁存和初始化锁存器各一次)才能激活输出。ADuC812上的I/O端口线还用于控制断电(CE输入)和检测锁定(MUXOUT配置为锁定检测并由端口输入轮询)。

在所述模式下操作时,ADuC812的最大SCLOCKrate为4 MHz。这意味着输出频率可以改变的最大速率将是166kHz。

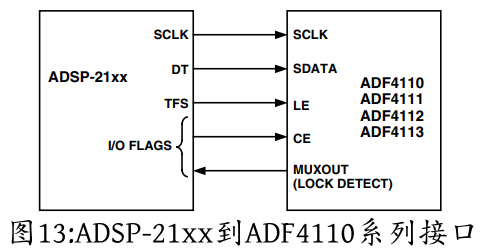

ADSP-2181接口

图13显示了ADF4110系列和ADSP-21xx数字信号处理器之间的接口。ADF4110系列每次锁存写入都需要一个24位串行字。使用ADSP-21xx系列实现这一点的最简单方法是使用AlternateFraming的自动缓冲传输操作模式。这提供了一种在产生中断之前传输整个串行数据块的方法。

将字长设置为8位,并为每个24位字使用三个存储位置。要对每个24位锁存器进行编程,请存储三个8位字节,启用自动缓冲模式,然后写入DSP的传输寄存器。最后一个操作启动自动缓冲区传输。

芯片级封装的PCB设计指南

芯片级封装(CP-20)上的焊盘是矩形的。这些的印刷电路板焊盘应比封装焊盘长度长0.1毫米,比封装焊区宽度宽0.05毫米。土地应该集中在垫子上。这将确保焊点尺寸最大化。

芯片级封装的底部有一个中央热垫。印刷电路板上的热垫应至少与暴露的垫一样大。在印刷电路板上,热敏焊盘和焊盘图案的内边缘之间应至少有0.25毫米的间隙。这将确保避免短路。

热通孔可用于印刷电路板热敏板上,以提高封装的热性能。如果使用过孔,则应将其以1.2mm的间距网格结合在热垫中。过孔直径应在0.3mm至0.33mm之间,过孔筒应镀上1盎司的铜以插入过孔。用户应将印刷电路板热焊盘连接到AGND。