EP9312

Universal Platform SOC Processor

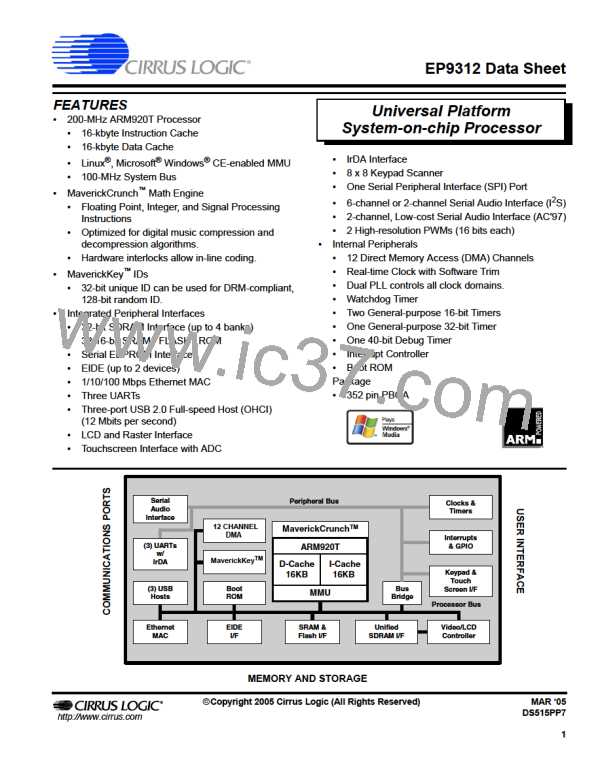

Static Memory Burst Write Cycle

Parameter

Symbol

tADs

Min

Typ

Max

Unit

tHCLK − 3

tHCLK × 2

AD setup to WRn assert time

AD hold from WRn deassert time

WRN/DQMn deassert to AD transition time

CSn hold from WRn deassert time

CSn to WRn assert delay time

CSn to DQMn assert delay time

DQMn assert time

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

tADh

tADd

tHCLK + 6

tCSh

7

tWRd

2

1

tDQMd

tDQpwL

tDQpwH

tWRpwL

tWRpwH

tDAh

tHCLK × (WST1 + 1)

tHCLK × (WST1 + 11)

(tHCLK × 2) + 14

(tHCLK × 2) + 7

8

DQMn deassert time

WRn assert time

WRn deassert time

tHCLK

WRn/DQMn deassert to DA transition time

WRn/DQMn assert to DA valid time

tDAv

Note: These characteristics are valid when the Page Mode Enable (Burst Mode) bit is set. See the User's Guide for details.

tADs

tADd

tADh

AD

CSn

tWRpwL

tCSh

WRn

RD

tWRpwH

tWRd

tDQpwL

tDQMd

DQMn

DA

tDQpwH

tDAh

tDAv

WAIT

Figure 13. Static Memory Burst Write Cycle Timing Measurement

26

©Copyright 2005 Cirrus Logic (All Rights Reserved)

DS515PP7

CIRRUS [ CIRRUS LOGIC ]

CIRRUS [ CIRRUS LOGIC ]