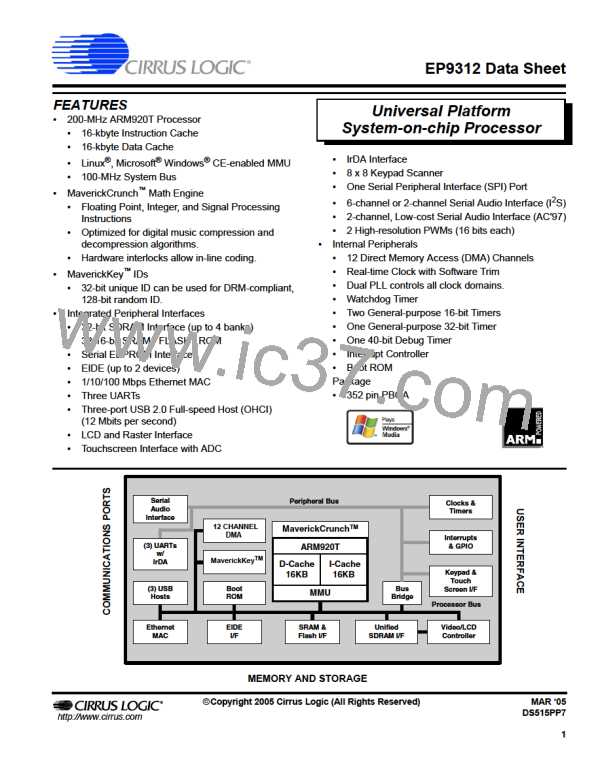

EP9312

Universal Platform SOC Processor

PIO Data Transfers

Mode 0 Mode 1 Mode 2 Mode 3 Mode 4

Parameter

Symbol

(in ns)

(in ns)

(in ns)

(in ns)

(in ns)

t0

t1

Cycle time

(min)

(min)

(min)

(min)

(min)

(min)

(min)

(min)

(max)

(min)

(min)

(Note 1, 4)

(Note 4)

600

70

165

-

383

50

125

-

240

30

100

-

180

30

80

70

30

0

120

25

70

25

20

0

Address valid to DIORn / DIOWn setup

DIORn / DIOWn 16-bit

DIORn / DIOWn recovery time

DIOWn data setup

t2

(Note 1, 4)

(Note 1, 4)

(Note 4)

t2i

t3

60

0

45

0

30

0

t4

DIOWn data hold

t5

DIORn data setup

20

0

20

0

20

0

20

0

20

0

t6

DIORn data hold

t6z

t9

DIORn data high impedance state

DIORn / DIOWn to address valid hold

(Note 2, 4)

(Note 4)

30

20

30

15

30

10

30

10

30

10

Read Data Valid to IORDY

active (if IORDY initially low after tA)

tRD

0

0

0

0

0

(Note 4)

(Note 3, 4)

(Note 4)

tA

tB

IORDY Setup time

35

1250

5

35

1250

5

35

1250

5

35

1250

5

35

1250

5

IORDY Pulse Width

(max)

(max)

(max)

tC

IORDY assertion to release

DIOWn assert to data valid

tDDV

10

10

10

10

10

Note: 1. t0 is the minimum total cycle time, t2 is the minimum DIORn / DIOWn assertion time, and t2i is the minimum DIORn / DIOWn

negation time. A host implementation shall lengthen t2 and/or t2i to ensure that t0 is equal to or greater than the value

reported in the devices IDENTIFY DEVICE data. A device implementation shall support any legal host implementation.

2. This parameter specifies the time from the negation edge of DIORn to the time that the data bus is released by the device.

3. The delay from the activation of DIORn or DIOWn until the state of IORDY is first sampled. If IORDY is inactive then the host

shall wait until IORDY is active before the register transfer cycle is completed. If the device is not driving IORDY negated at

the tA after the activation of DIORn or DIOWn, then t5 shall be met and tRD is not applicable. If the device is driving IORDY

negated at the time tA after the activation of DIORn or DIOWn, then tRD shall be met and t5 is not applicable.

4. Timings based upon software control. See User’s Guide.

5. All IDE timing is based upon HCLK = 100 MHz.

32

©Copyright 2005 Cirrus Logic (All Rights Reserved)

DS515PP7

CIRRUS [ CIRRUS LOGIC ]

CIRRUS [ CIRRUS LOGIC ]