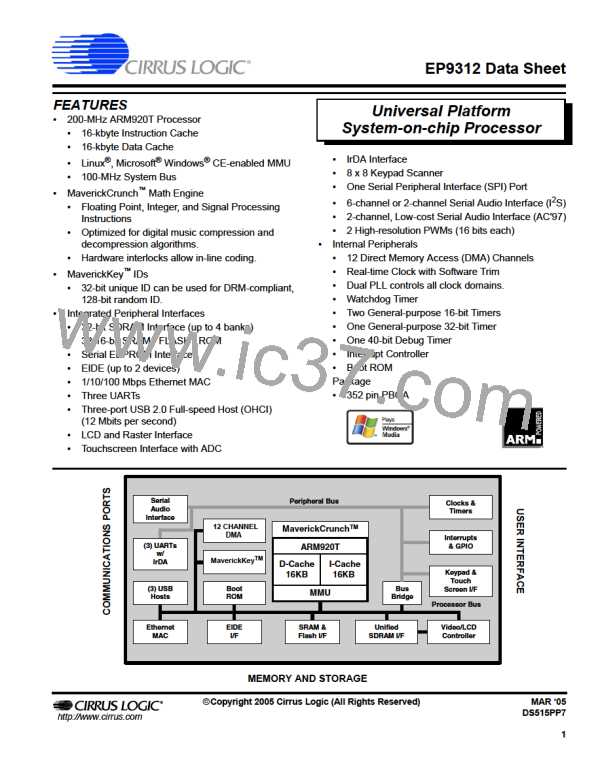

EP9312

Universal Platform SOC Processor

Inter-IC Sound - I2S

Parameter

Symbol

tclk_per

tclk_high

tclk_low

tclkrf

Min

Typ

Max

Unit

ti2s_clk

SCLK cycle time

-

-

-

-

ns

ns

ns

ns

ns

(ti2s_clk) / 2

SCLK high time

(ti2s_clk) / 2

SCLK low time

-

-

SCLK rise/fall time

SCLK to LRCLK assert delay time

1

-

4

-

8

3

tLRd

Hold between SCLK assert then LRCLK deassert

tLRh

or

0

-

-

ns

Hold between LRCLK deassert then SCLK assert

tSDIs

tSDIh

tSDOd

tSDOh

SDI to SCLK deassert setup time

SDI from SCLK deassert hold time

SCLK assert to SDO delay time

SDO from SCLK assert hold time

12

0

-

-

-

-

-

-

ns

ns

ns

ns

-

9

-

1

Note:

ti2s_clk is programmable by the user.

tclk_per

tclk_low

tclkrf

tclk_high

SCLK

tLRd

tLRh

LRCLK

tSDIs

tSDIh

SDI

tSDOh

tSDOd

SDO

Figure 33. Inter-IC Sound (I2S) Timing Measurement

48

©Copyright 2005 Cirrus Logic (All Rights Reserved)

DS515PP7

CIRRUS [ CIRRUS LOGIC ]

CIRRUS [ CIRRUS LOGIC ]