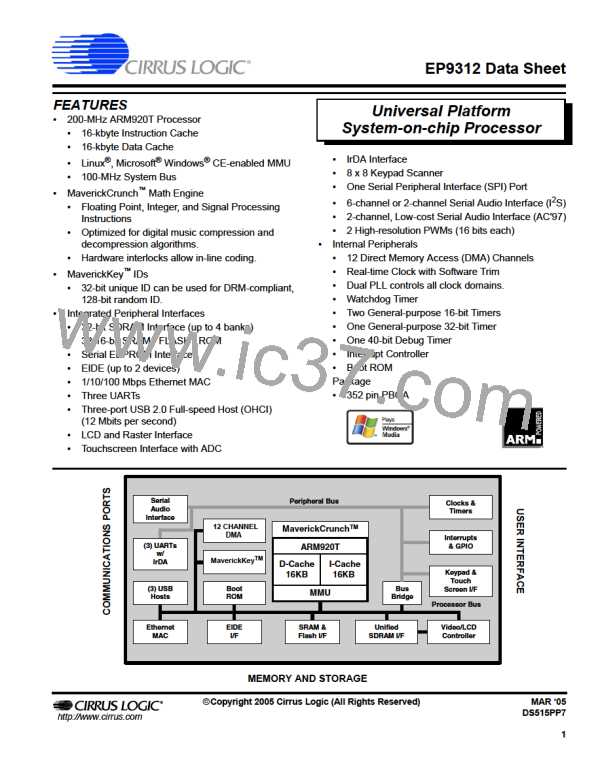

EP9312

Universal Platform SOC Processor

Pin List

The following Plastic Ball Grid Array (PBGA) ball assignment table is sorted in order of ball.

Ball

Signal

Ball

Signal

Ball

Signal

Ball

Signal

A1

A2

CSN[7]

DA[28]

AD[18]

DD[8]

E9

E10

E11

E12

E13

E14

E15

E16

E17

E18

E19

E20

F1

RVDD

GND

L3

L4

DA[16]

DA[15]

GND

T13

T14

T15

T16

T17

T18

T19

T20

U1

CVDD

GND

A3

GND

L5

INT[0]

USBM[1]

RXD[0]

TXD[2]

ROW[2]

ROW[4]

AD[0]

A4

RVDD

L8

GND

A5

DD[4]

CVDD

L9

GND

A6

AD[17]

RDN

CVDD

L10

L11

L12

L13

L16

L17

L18

L19

L20

M1

GND

A7

GND

GND

A8

RXCLK

MIIRXD[0]

RXDVAL

MIITXD[2]

TXERR

CLD

ASDI

GND

A9

DIOWN

EGPIO[0]

EGPIO[3]

EGPIO[5]

SDCSN[3]

DA[22]

GND

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

B1

CVDD

COL[5]

COL[7]

RSTON

PRSTN

AD[7]

DA[14]

AD[6]

AD[5]

CVDD

GND

U2

P[15]

U3

P[10]

U4

P[7]

U5

P[6]

NC

F2

U6

P[4]

NC

F3

DA[24]

U7

P[0]

NC

F4

AD[25]

M2

U8

AD[13]

DA[3]

EGPIO[12]

EGPIO[15]

NC

F5

RVDD

M3

U9

F6

GND

M4

U10

U11

U12

U13

U14

U15

U16

U17

U18

U19

U20

V1

DA[0]

F7

CVDD

M5

DSRN

BOOT[1]

NC

NC

F14

F15

F16

F17

F18

F19

F20

G1

CVDD

M8

CSN[2]

DA[31]

DA[30]

DA[27]

DD[7]

GND

M9

GND

B2

GND

M10

M11

M12

M13

M16

M17

M18

M19

M20

N1

GND

SSPRX1

INT[1]

PWMOUT

USBM[0]

RXD[1]

TXD[1]

ROW[1]

P[16]

B3

EGPIO[2]

EGPIO[4]

EGPIO[6]

EGPIO[8]

SDCSN[0]

SDCSN[1]

SDWEN

SDCLK

RVDD

GND

B4

GND

B5

GND

B6

DD[3]

GND

B7

WRN

COL[4]

COL[3]

COL[6]

CSN[0]

DA[13]

DA[12]

DA[11]

AD[3]

CVDD

CVDD

GND

B8

MDIO

G2

B9

MIIRXD[1]

RXERR

MIITXD[1]

CRS

G3

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

C1

G4

V2

P[11]

G5

V3

P[8]

G6

RVDD

N2

V4

DD[15]

DD[13]

P[1]

NC

G15

G16

G17

G18

G19

G20

H1

RVDD

N3

V5

NC

RVDD

N4

V6

NC

EGPIO[7]

EGPIO[9]

EGPIO[10]

EGPIO[11]

DQMN[3]

CASN

N5

V7

AD[14]

AD[12]

DA[2]

NC

N6

V8

EGPIO[13]

NC

N8

V9

N9

GND

V10

V11

V12

V13

V14

IDECS0N

IDEDA[2]

TDI

WAITN

TRSTN

CSN[1]

CSN[3]

N10

N11

N12

N13

GND

H2

GND

H3

RASN

GND

GND

C2

H4

SDCSN[2]

GND

ASYNC

56

©Copyright 2005 Cirrus Logic (All Rights Reserved)

DS515PP7

CIRRUS [ CIRRUS LOGIC ]

CIRRUS [ CIRRUS LOGIC ]