CMOS SCC串行 通信控制器

日期:2019-10-9概述

Zilog Z80C30--ic/" title="Z80C30-">Z80C30-ic/" title="Z80C30">Z80C30和Z85C30--ic/" title="Z85C30-">Z85C30-ic/" title="Z85C30">Z85C30设备的特点包括:

Z85C30--ic/" title="Z85C30-">Z85C30-ic/" title="Z85C30">Z85C30-针对非多路复用总线微处理器进行优化。

Z80C30--ic/" title="Z80C30-">Z80C30-ic/" title="Z80C30">Z80C30-为多路总线微处理器优化。

与NMOS版本兼容的管脚。

两个独立的0至4.1 Mbit/秒全双工信道。每个通道带有单独的晶体振荡器、波特率发生器(BRG)和用于时钟恢复的数字锁相环(DPLL)。

程序控制下的多协议操作;可编程用于NRZ、NRZI或FM数据编码。

异步模式,每个字符有5至8位和1、1.5或2个停止位、可编程时钟因子、中断检测和生成;奇偶校验、溢出和帧错误检测。

同步模式,在一个或两个同步字符上进行内部或外部字符同步,CRC生成和检查,CRC-16或CRC-CCITT预设为1或0。

SDLC/HDLC模式,具有全面的帧级控制、自动零插入和零删除、I字段剩余处理、中止生成和检测、CRC生成和检查以及SDLC循环。

软件中断确认功能(不适用于NMOS)。

本地回送和自动回送模式。

支持T1数字中继。

增强的DMA支持(不适用于NMOS)10 x 19位状态FIFO 14位字节计数器。

速度:

–Z85C3O-8.5、10、16.384兆赫

–Z80C3O-8,10兆赫

仅限Z85C30--ic/" title="Z85C30-">Z85C30-ic/" title="Z85C30">Z85C30的其他功能

默认情况下,下面列出的某些功能可用。其中一些(带有*的功能)在默认情况下被禁用,以保持与现有串行通信控制器(SCC)设计和“通过WR7启用的程序”的兼容性:

新的可编程WR7(写入寄存器7 prime)以启用新功能。支持同步通信的sdlc模式的改进:

–改进功能,以便于背靠背发送帧。

–自动SDLC打开标志传输。

–在SDLC模式下自动发送欠载/EOM锁存复位。

–自动关闭RTS。

–关闭标志后,在SDLC NRZI模式下TXD引脚被强制调高。

–完成CRC接收。

–改进了对状态FIFO中中止序列的响应。

–自动发送CRC发生器预设/重置。

–扩展读写寄存器。*–写入数据设置计时改进。改进的交流定时:·

–3到3.6 pclk访问恢复时间。

–可编程DTR/REQ定时。

–将数据写入wr设置时间要求的下降沿现在已消除。

–缩短内部计时。其他功能包括:·

–扩展读取功能,将写入的值读回写入寄存器。*–读取期间锁定错误。

–RRO,位D7和RR10,位D6现在具有重置默认值。

一般说明

Z80C30--ic/" title="Z80C30-">Z80C30-ic/" title="Z80C30">Z80C30/Z85C30--ic/" title="Z85C30-">Z85C30-ic/" title="Z85C30">Z85C30串行通信控制器(SCC)是Zilog®于1981年推出的SCC系列中与引脚和软件兼容的CMOS成员。它是一个双通道、多协议数据通信外围设备,可通过多路或非多路地址/数据总线轻松与CPU接口。

先进的cmos工艺具有更低的功耗、更高的性能和更高的抗噪声能力。内部寄存器的编程灵活性允许将scc配置为各种串行通信应用程序。

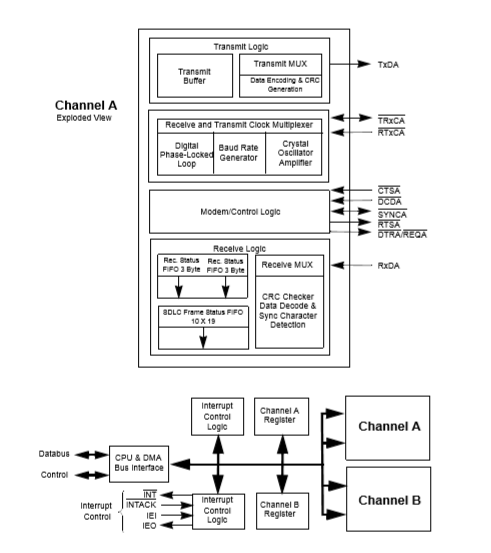

SCC的框图。

许多片上功能,如波特率发生器(brg)、数字锁相环(dpll)和晶体振荡器,减少了对外部逻辑的需求。

附加功能包括一个10 x 19位状态fifo和14位字节计数器,以支持使用dma控制器的高速sdlc传输。

scc处理异步格式、同步字节定向协议(如ibm bisync)和同步比特定向协议(如hdlc和ibm sdlc)。这个设备实际上支持任何串行数据传输应用程序(例如,盒式磁带、软盘、磁带机等)。

该装置可在任何同步模式下生成和检查CRC码,并可编程以在各种模式下检查数据完整性。SCC还包含在两个信道中进行调制解调器控制的设备。在不需要这些控件的应用程序中,调制解调器控件可用于通用I/O。也支持菊花链中断层次结构。

管脚说明

Z85C30--ic/" title="Z85C30-">Z85C30-ic/" title="Z85C30">Z85C30/Z80C30--ic/" title="Z80C30-">Z80C30-ic/" title="Z80C30">Z80C30公共管脚功能

以下各节介绍了Z85C30--ic/" title="Z85C30-">Z85C30-ic/" title="Z85C30">Z85C30和Z80C30--ic/" title="Z80C30-">Z80C30-ic/" title="Z80C30">Z80C30设备的公共管脚功能:

清除发送(输入,有效低)-如果这些引脚被编程为自动启用,则输入上的低电平将启用相应的发射器。如果没有编程为自动启用,这些引脚可以用作通用输入。两个输入都是施密特触发器缓冲,以适应缓慢上升时间输入。scc检测这些输入上的脉冲,并且可以在两个逻辑级转换上中断cpu。

数据载波检测(输入,低电平)-如果编程设置为自动启用,则这些引脚作为接收器启用。否则,这些管脚用作通用输入管脚。两个引脚都是施密特触发器缓冲,以适应缓慢上升时间信号。SCC检测这些管脚上的脉冲,并且可以在两个逻辑级转换上中断CPU。

DTR/需求,DTR/需求

数据终端就绪/请求(输出,低电平)-这些输出遵循编程到DTR位的状态。它们也可以用作通用输出或dma控制器的请求线。

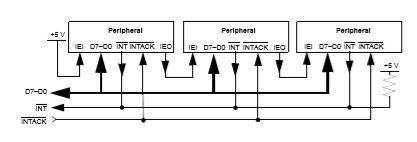

中断启用(输入,高电平)-当有多个中断驱动设备时,iei与ieo一起构成中断菊花链。高iei表示没有其他高优先级设备正在服务中断或正在请求中断。

中断使能输出(输出,高电平)-只有当iei高并且

CPU没有为SCC中断提供服务,或者SCC没有请求中断(仅限中断确认周期)。ieo连接到下一个低优先级设备的iei输入,因此禁止来自低优先级设备的中断。

国际的

中断请求(输出,开漏,低电平)-当SCC请求中断时,此信号激活。

内塔克

中断确认(输入,低电平)-此信号表示激活的中断确认周期。在这个周期中,SCC中断菊花链结束。当rd激活时,scc在数据总线上放置一个中断向量(如果iei高)。凹口被PCLK的上升沿锁住。

时钟(输入)-这是用于同步内部信号的主scc时钟。PCLK是TTL电平信号。PCLK不需要与主系统时钟有任何相位关系。最大传输速率为1/4 pclk。

接收数据(输入,高电平)-这些信号以标准ttl电平接收串行数据。

接收/发送时钟(输入,低电平)-这些引脚可以编程

几种不同的操作模式。在每个信道中,rtxc可以提供接收时钟、发送时钟、波特率发生器时钟或数字相位时钟。-

锁定回路。这些管脚也可以编程,与相应的同步管脚一起用作晶体振荡器。在异步模式下,接收时钟可以是数据速率的1、16、32或64倍。

发送请求(输出,有效低)-当请求发送(rts)位时

设置写入寄存器5(见第19页图9),RTS信号变低。当RTS位在异步模式下复位并且自动启用时,信号在发送器为空后变高。在同步模式下,它严格遵循rts位的状态。

当auto enable关闭时,rts管脚可以用作通用输出。

同步加速器

同步(输入或输出,低电平)-这些管脚用作晶体振荡器电路的输入、输出或部分。在异步接收模式下(Crystal振荡器选项未选中),这些引脚是类似于CTS和DCD的输入。在此模式下,这些行上的转换会影响读取寄存器0中同步/寻道状态位的状态,但没有其他功能。

在未选择晶体振荡器的外部同步模式下,这些线路也

作为输入。在这种模式下,同步字符中的最后一位被接收后,必须在两个接收时钟周期内低驱动同步。角色集合开始于

同步激活前接收时钟的上升沿。

在未选择晶体振荡器的内部同步模式(单同步和双同步)中,这些管脚用作输出,并且仅在接收时钟周期中识别同步字符的部分期间激活。此同步条件未锁定。每次识别同步模式时(不考虑字符边界),这些输出都是活动的。在sdlc模式下,这些管脚作为输出,在收到标志时有效。

传输数据(输出,高电平)-这些输出信号以标准ttl电平传输串行数据。

发送/接收时钟(输入或输出,低电平)-这些针可以是

在几种不同的操作模式下编程。trxc可以在输入模式下提供接收时钟或发送时钟,或者在输出模式下提供数字锁相环、晶体振荡器、波特率发生器或发送时钟的输出。

W/需求,W/需求

等待/请求(输出,为等待功能编程时为开漏,为请求功能编程时为高或低驱动)-这些双用途输出可以编程为dma控制器的请求线,或者编程为使cpu与scc数据速率同步的等待线。重置状态为等待。

通道A/通道B(输入)-此信号选择发生读或写操作的通道。

总工程师

芯片启用(输入,低电平)-该信号为读或写操作选择scc。

数据总线(双向,三态)-这些线路携带数据和命令往返于SCC。

付款交单

数据/控制选择(输入)-该信号定义了传送到或从scc传送的信息的类型。高表示数据传输;低表示命令。

研发

读取(输入,低电平)-此信号表示读取操作,当选择SCC时,启用SCC的总线驱动器。在中断确认周期内,如果SCC是请求中断的最高优先级设备,则该信号将中断向量传送到总线上。

写入(输入,低电平)-当选择SCC时,此信号表示写入

操作。rd和wr的重合被解释为复位。

小精灵

地址/数据总线(双向、高电平、三态)-这些多路复用线路将寄存器地址以及数据或控制信息传送到scc。

地址选通(输入,低电平)-AD7–AD0上的地址被该信号的上升沿锁定。

小精灵

芯片选择0(输入,低电平)-此信号与AD7–AD0上的地址同时锁定,并且必须处于活动状态才能发生预期的总线事务。

芯片选择1(输入,高电平)-第二个选择信号也必须在预期的总线事务发生之前处于活动状态。CS1必须在整个事务中保持活动状态。

数据选通(输入,低电平)-这个信号为数据传输提供定时

进出SCC。如果as和ds重合,则此汇流被解释为重置。

读/写(输入)-此信号指定要执行的操作是读还是写。

功能描述

SCC的架构描述如下:

作为以各种协议传输和接收数据的数据通信设备。

作为微处理器外围设备,SCC提供有价值的功能,如矢量中断和DMA支持。

scc的外围设备和数据通信在以下各节中描述。

轮询时,所有中断都被禁用。当执行任何功能时,SCC中的三个状态寄存器会自动更新。例如,sdlc模式下的帧尾在其中一个状态寄存器中设置一个位。轮询的目的是让cpu周期性地读取状态寄存器,直到寄存器内容指示需要传输数据为止。只有一个寄存器被读取,根据其内容,CPU要么写入数据,要么读取数据,要么继续。寄存器中的两位表示需要数据传输。另一种方法是对中断挂起寄存器进行轮询,以确定中断源。两个通道的状态都位于一个寄存器中。

中断

SCC的中断结构支持向量化和嵌套中断。SCC的中断确认功能(intack pin)支持嵌套中断。

这允许CPU识别中断的发生,并重新启用更高的优先级-

奥利蒂打断了。由于一个intack周期将int管脚从激活状态释放出来,高优先级scc中断或另一个高优先级设备可以中断cpu。

当scc响应来自cpu的中断确认信号(intack)时,可以在数据总线上放置中断向量。这个矢量是用wr2写的,可以用rr2a或rr2b读。为了加快中断响应时间,scc可以修改这个矢量中的三个位来指示状态。如果在通道A中读取矢量,则永远不包括状态。如果在通道B中读取矢量,则始终包括状态。

SCC中的六个中断源(两个通道中的传输、接收和外部/状态中断)中的每一个都有三位与中断源相关。

中断挂起(IP)、服务中断(IUS)和中断启用(IE)。IE钻头的操作是直接的。如果为给定的中断源设置了ie位,则该源可以请求中断。例外情况是WR9中的MIE(主中断启用)位被重置,并且不能请求中断。ie位是只写的。

另外两位与中断优先级链有关。作为微处理器外围设备,scc只能在没有更高优先级设备请求中断时(即iei高时)请求中断。如果有问题的设备请求中断,它拉低int。cpu以intack响应,中断设备将矢量放在数据总线上。

SCC还可以通过软件执行中断确认周期。在一些CPU中

在环境中,很难用必要的定时来创建内插信号

确认中断并允许中断嵌套。在这些情况下,可以使用对scc的软件命令来创建intack信号。

在scc中,中断挂起(ip)位表示需要中断服务。当一个

IP位为1,IEI输入高,INT输出低,请求中断。在scc中,如果ie位不是通过启用中断来设置的,则永远不会设置该源的ip。IP位在RR3A中是可读的。

IUS位表示正在服务中断请求。如果设置了一个ius,则scc中和scc外部优先级较低的所有中断源都将被阻止请求中断。

内部中断源受到内部菊花链状态的抑制,而较低优先级设备则受到SCC的IEO输出被拉低并传播到后续外设的抑制。如果没有更高优先级的设备请求中断,则在中断确认周期中设置一个IUS位。

有三种类型的中断:

传输

接收

外部/状态

每种中断类型在程序控制下启用,通道A的优先级高于通道B,接收器、传输和外部/状态中断在每个通道内按该顺序排列优先级。

启用时,接收器通过以下三种方式之一中断CPU:

在第一个接收字符或特殊接收条件下中断

中断所有接收字符或特殊接收条件

仅在特殊接收条件下中断

第一个字符或特殊条件下的中断和特殊条件下的中断通常与块传输模式一起使用。特殊接收条件是以下条件之一。接收器溢出、异步模式下的帧错误、sdlc模式下的帧结束以及可选的奇偶校验错误。特殊接收条件中断不同于普通接收字符,只有在中断确认周期内,通过矢量中的状态才可使用中断。在第一接收字符中断中,在第一接收字符中断后的任何时候,都会发生特殊接收条件的中断。

外部/状态中断的主要功能是监视

然而,cts、dcd和sync管脚的外部/状态中断也由以下原因引起:传输欠载条件;波特率发生器中的零计数;通过检测数据流中的中断(异步模式)、中止(sdlc模式)或eop(sdlc循环模式)序列。由中止或EOP引起的中断具有一个特殊特性,允许SCC在检测到或终止中止或EOP序列时中断。此功能有助于在SDLC模式下正确终止当前消息、正确初始化下一条消息以及在外部逻辑中精确定时中止条件。在sdlc循环模式下,此功能允许辅助站识别主站,在轮询序列期间恢复对循环的控制。

软件中断确认

在cmos版本的scc上,scc中断确认周期可以通过软件启动。如果设置了写入寄存器9(WR9)位D5,则读取寄存器2(RR2)将导致

内部执行的中断确认周期。就像一个硬件安装周期,

软件确认导致int pin返回高,ieo pin返回低,并为最高优先级中断挂起设置ius锁存。

与使用硬件输入信号类似,软件确认周期要求在中断服务程序中发出重置最高IUS命令。每当使用中断确认周期(硬件或软件)时,需要重置最高IUS命令。如果从通道A读取rr2,则返回未修改的向量。如果从信道b读取rr2,则修改向量以指示中断源。当位05设置为1时,wr9中的向量包括状态(vis)和无向量(nv)位被忽略。

当不使用内插和IEI引脚时,应通过电阻器(典型值为10 kΩ)将其拉至VCC。

CPU/DMA块传输

scc提供块传输模式以适应cpu块传输功能和dma控制器。块传输模式将wait/reouest输出与wr1中的wait/request位结合使用。在软件控制下,wait/reouest输出可以定义为cpu块传输模式下的等待线或dma块传输模式下的请求线。

对于dma控制器,scc请求输出指示scc已准备好传输-

将数据传送到或从存储器传送到cpu,等待线指示escc不是

准备传输数据,从而请求cpu延长i/o周期。DTR/

请求线路允许在DMA控制下进行全双工操作。

SCC数据通信能力

SCC提供两个独立的全双工可编程通道,用于任何常见的异步或同步数据通信协议。每个数据通信信道具有相同的特性和能力。

异步模式

发送和接收在每个通道上独立完成,每个字符有5到8位,外加可选的奇偶校验。发射机可以为每个字符提供一个、一个和半个或两个停止位,并且可以随时提供中断输出。接收器中断检测逻辑在接收到中断的开始和结束时中断cpu。

在接收数据输入端(rxda或rxdb管脚)检测到低电平后,通过瞬时尖峰抑制机制检查信号半位时间,以防止接收尖峰。如果低位没有持续(暂时),字符装配过程就不会启动。

检测帧错误和溢出错误并将其与发生错误的部分字符一起缓冲。矢量化中断允许使用专用例程快速服务或错误条件。内置的检查过程避免了将帧错误解释为新的起始位。帧错误导致在开始搜索下一个起始位的点上增加半位时间。

SCC不需要对称的发送和接收时钟信号——这一特性允许使用多种时钟源。发射器和接收器以提供给接收和发送时钟输入的速率处理数据。在异步模式下,同步管脚可以编程为一个输入,用于监视环形指示器等功能。

同步模式

scc支持面向字节和位的同步通信。面向字节的同步协议有几种处理方式。它们允许使用6位或8位同步字符(monosync)、12位或16位同步模式(bisync)或外部同步信号进行字符同步。在不中断CPU的情况下删除前导同步字符。

5位或7位同步字符在SCC中用8位或16位模式检测,方法是将较大的模式重叠到多个传入的同步字符上

同步字节定向模式的crc检查延迟一个字符的时间,以便cpu可以禁用对特定字符的crc检查。此功能允许实现ibm bisync等协议。

支持CRC-16(x16+x15+x12+1)和CCITT(x16+x12+x5+1)错误检查多项式。在所有同步模式下都可以选择任一多项式。您可以将CRC生成器和检查器设置为“全部1”或“全部0”。SCC还提供一个功能,当没有其他数据可供传输时,自动传输CRC数据。此功能允许在dma控制下进行高速传输,而无需在消息末尾进行cpu干预。

当没有数据或CRC以同步模式发送时,无论编程字符长度如何,发射机都会插入6、8或16位同步字符。

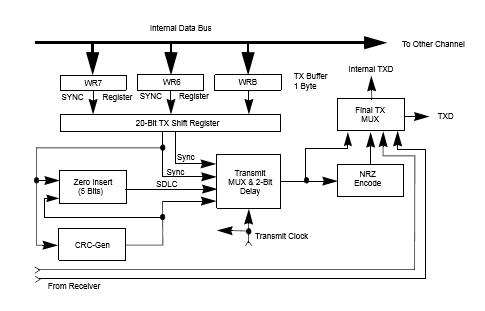

SDLC模式

scc通过执行自动标志发送、零插入和crc生成来支持同步的面向位协议,例如sdlc和hdlc。一个特殊的命令用于中止传输中的帧。在消息的末尾,当发送器运行不足时,scc自动发送crc和尾随标志。发射机也可以编程发送由连续标记字符或稳定标记条件组成的空闲线。

如果在消息中间发生传输不足,则外部/状态中断会警告CPU此状态更改,并发出中止。scc也可以被编程为在欠运行的情况下发送中止本身,从而释放此任务的cpu。每个字符可以发送一到八位,允许接收帧的信息字段中没有关于字符结构的先验信息的消息。

接收机在帧的前标志上自动获取同步

SDLC或HDLC,并在同步引脚上提供同步信号(也可以编程中断)。接收机可以被编程为搜索由用户选择的地址的单字节(或一个字节内的四位)或全局广播地址寻址的帧。在此模式下,将忽略与用户选定地址或广播地址不匹配的帧。

地址字节数在软件控制下扩展。对于接收数据,可以选择第一个接收字符上的中断,或每个字符上的中断,或仅在特殊情况下(帧结束)。接收机自动删除在字符组合期间由发射机插入的所有0,crc也被计算出来,并被自动检查以验证帧传输。在传输结束时,接收帧的状态在状态寄存器中可用。在sdlc模式下,scc必须编程为使用sdlc crc多项式,但生成器和检查器可以预设为所有1或所有0。crc在传输前反转,接收器根据位模式0001110100001111进行检查。

nrz、nrzi或fm编码可用于任何1x模式。异步模式下可用的奇偶校验选项在同步模式下可用。

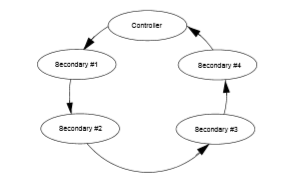

SDLC环路模式

除了正常的sdlc外,scc还支持sdlc环路模式。在sdlc环路中,主控制器站管理环路上的消息通信流和任意数量的辅助站。在sdlc循环模式下,scc执行辅助站的功能,而在常规sdlc模式下运行的scc充当控制器。可通过设置WR10位D1来选择SDLC环路模式。

sdlc环路中的一个辅助站总是监听围绕环路发送的消息,并通过以一位时间延迟重新发送这些消息来将这些消息传递给环路的其余部分。辅助站仅在特定时间将其自身的消息放置在循环上。

控制器通过在环路周围发送一个称为轮询结束(EOP)的特殊字符来指示辅助站可以发送消息。EOP字符是位模式11111110。由于消息期间零插入,此位模式是唯一的,并且易于识别。

当辅助站包含要传输的消息并识别线路上的EOP时,它会在传输前将EOP的最后二进制1更改为0。此更改的效果是将EOP转换为标志序列。辅助站现在将其消息放在循环上,并用EOP终止该消息。任何在回路中进一步下行的二级站,其发送的消息通过相同的过程将其消息附加到第一二级站的消息中。没有消息发送的任何二级站回显传入的消息,并且禁止将消息放置在循环上(识别EOP时除外)。在sdlc循环模式下,可以使用nrz、nrzi和fm编码。

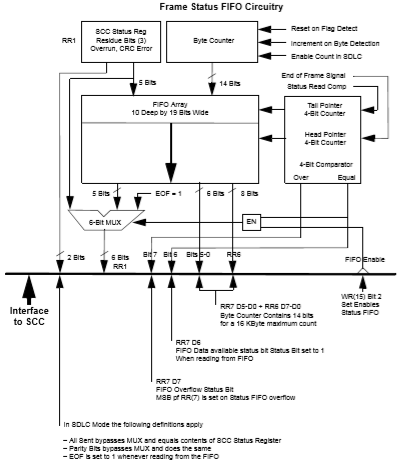

SCC接收高速背对背SDLC帧的能力通过10深19宽的状态FIFO最大化。启用时(通过WR15,位D2),它提供

dma继续将数据传输到内存中以便cpu以后可以检查消息的能力。对于每个sdlc帧,存储14位字节计数和5个状态/错误位。字节计数和状态位通过读取寄存器6和7访问。只有在启用SDLC FIFO时,才能访问读取寄存器6和7。10 x 19状态fifo与3字节接收数据fifo分开。

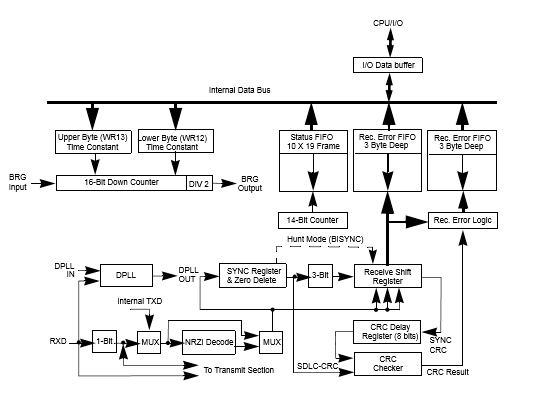

波特率发生器

SCC中的每个通道都包含一个可编程波特率发生器(BRG)。每个发生器由两个8位时间常数寄存器组成,它们构成16位时间常数、16位下行计数器和输出端的触发器,产生方波。启动时,输出触发器设置为高状态,时间常数寄存器中的值加载到计数器中,计数器开始倒计时。BRG的输出在达到0时切换,时间常数寄存器中的值加载到计数器中,然后重复该过程。时间常数可以随时更改,但新值在下次加载计数器之前不会生效。

brg的输出可以用作发送时钟和/或接收时钟。它还可以驱动数字锁相环(见数字锁相环)。

如果接收时钟或发送时钟未被编程为来自trxc引脚,则brg的输出可通过trxc引脚发出回声。以下公式将时间常数与波特率联系起来,其中pclk或rtxc是以赫兹为单位的brg输入频率。时钟模式为1、16、32或64,如在写入寄存器4的位d6和d7中选择的。

同步操作模式选择1,异步模式选择16、32或64。

自动回显和本地环回

SCC能够自动回显它接收到的所有信息。此功能主要在异步模式下有用,但也适用于同步和sdlc模式。自动回音模式(tx0是rx0)与nrzi或fm编码一起使用,没有额外的延迟,因为数据流在重新传输之前未被解码。在自动回声模式下,

当变送器启用时,CTS输入将被忽略(尽管此输入上的转换仍然会导致中断,如果编程的话)。在这种模式下,发射器实际上被旁路

程序员负责关闭发射机中断并等待/

发送请求。

scc还可以进行本地环回。在此模式下,txd或rxd类似于auto

回声模式。但是,在本地环回模式下,内部传输数据绑定到内部接收数据,而rxd被忽略(除了通过txd进行回显)。CTS

当发射和接收启用时,DCD输入也被忽略。但是,这些输入上的转换仍然会导致中断。本地环回在异步、同步和sdlc模式下工作,数据流采用nrz、nrzi或fm编码。

sdlc fifo帧状态fifo增强

scc接收高速背靠背sdlc帧的能力通过10深19宽的状态fifo最大化。启用时(通过wr15,位d2),它使dma能够继续将数据传输到内存中,以便cpu可以稍后检查消息。对于每个sdlc帧,存储14位字节计数和5个状态/错误位。字节计数和状态位通过读取寄存器6和7访问。只有在启用SDLC FIFO时,才能访问读取寄存器6和7。10x19状态fifo与3字节接收数据fifo分开。

当增强功能启用时,读取寄存器1(rr1)中的状态和sdlc帧的字节计数存储在10 x 19位状态fifo中。这种安排允许dma控制器在cpu验证消息是否正确接收时将下一帧传输到内存中。

总结操作;数据在被dma控制器传输到存储器之前被接收、组装并加载到8字节fifo中。当在sdlc帧的末尾接收到标志时,来自14位计数器和5个状态位的帧字节计数被加载到状态fifo中以供cpu验证。crc检查器自动重置,以准备下一帧可以立即开始。由于为每个帧保存字节计数和状态,因此稍后将验证消息的完整性。在发生状态fifo溢出之前,最多存储10帧的状态信息。

如果一个帧因中止而终止,字节计数将加载到状态fifo,计数器将为下一个帧重置。

先进先出细节

启用/禁用

当设置了WR15位D2且SCC处于SDLC/HDLC模式时,启用该FIFO。否则,状态寄存器内容绕过fifo并直接进入总线接口(fifo指针逻辑在禁用或通过通道或上电复位时复位)。当fifo模式被禁用时,scc向下兼容nmos z8530。通电时禁用FIFO模式(复位时WR15 D2设置为0)。后向兼容性对寄存器集的影响是,rr4是rr0的图像,rr5是rr1的图像,rr6是rr2的图像,rr7是rr3的图像。有关添加的寄存器的更多详细信息,请参见第30页的图16。fifo使能信号的状态是通过读取rr15位d2获得的。如果启用fifo,则该位设置为1;否则,它将重置。

读取操作

当WR15位D2设置且FIFO不为空时,下一个读取状态寄存器RR1或寄存器RR7和RR6的数据来自FIFO。读取状态寄存器rr1导致fifo的一个位置变为空。读取字节计数后读取状态,否则计数不正确。在fifo下溢之前,它被禁用。在这种情况下,多路复用器被切换,允许从状态寄存器直接读取状态。从rr7和rr6读取的数据包含未定义的位。rr7的位d6(fifo数据可用)确定状态数据是来自fifo还是直接来自状态寄存器,当fifo不为空时,状态寄存器设置为1。不是所有的状态位都存储在fifo中。所有发送、奇偶校验和eof位都绕过fifo。通过fifo发送的状态位是剩余位(3)、溢出和crc错误。

字节计数和fifo逻辑的操作顺序是按以下顺序读取寄存器。RR7、RR6和RR1(读RR6是可选的)。附加逻辑可防止从rr1中多次读取时清空fifo。从rr7读取锁定fifo空/满状态位(d6),并引导状态多路复用器从scc megacell读取,而不是从状态fifo读取(因为状态fifo为空)。从rr1读取允许从fifo读取条目(如果fifo为空,则添加逻辑以防止fifo下溢情况)。

写操作

当接收到sdlc帧(eof)的结束并且fifo被启用时,状态和字节计数寄存器的内容被加载到fifo中。eof信号用于增加fifo。如果fifo溢出,则rr7,位d7(fifo溢出)设置为指示溢出。该位和fifo控制逻辑通过禁用和重新启用fifo控制位(wr15,位02)复位。

程序设计

scc在每个信道中包含写入寄存器,这些寄存器由系统单独编程以配置信道的功能特性。

Z85 C30

在scc中,通过选择d/c引脚上的高电平直接寻址数据寄存器。对于所有其他寄存器(wr0和rr0除外),编写写寄存器需要两个写操作,读取读寄存器需要一个写操作和一个读操作。第一次写入是wr0,包含三个指向所选寄存器的位。第二次写入是所选寄存器的实际控制字,如果读取第二次操作,则访问所选读取寄存器。所有的scc寄存器,包括数据寄存器,都可以这样访问。指针位在读或写操作后自动清除,以便再次寻址wr0(或rr0)。

小精灵

所有SCC寄存器都可以直接寻址。在wr0b中发出的命令控制

scc解码在读或写周期开始时放在地址/数据总线上的地址。在右移模式下,信道选择A/B取自AD0,而忽略AD5的状态。在左移模式下,信道选择A/B取自AD5,而忽略AD0的状态。AD7和AD6总是作为地址位忽略,寄存器地址占用AD4-AD1。

Z85C30--ic/" title="Z85C30-">Z85C30-ic/" title="Z85C30">Z85C30/Z80C30--ic/" title="Z80C30-">Z80C30-ic/" title="Z80C30">Z80C30设置

初始化

系统程序首先发出一系列命令来初始化基本操作模式。接下来是其他命令,用于限定选定模式中的条件。例如,在异步模式下,必须首先设置字符长度、时钟速率、停止位数以及奇偶校验。设置中断模式,最后启用接收器和发射器。

写入寄存器

scc包含用于80c30的15个写入寄存器,而用于85c30的16个写入寄存器(如果计算发送缓冲器,则另加一个写入寄存器)。这些写入寄存器单独编程,以配置通道的功能“个性”。两个通道共享两个寄存器(WR2和WR9),通过其中一个通道访问。WR2包含两个通道的中断矢量,而WR9包含中断控制位和复位命令。

写入寄存器0(非多路复用总线模式)写入寄存器1

中断确认周期计时。时间间隔

向下移动,rd的下降沿,内部和外部iei/ieo菊花链固定。

如果SCC中有一个挂起的中断,并且当RD下降时IEI为高,则确认周期用于SCC。在这种情况下,SCC可编程为响应

通过将其中断向量放在d7-d0上降低rd。然后在服务锁存器内部设置适当的中断。

如果不使用外部菊花链,则需要AC参数38来解决SCC内部的中断优先级菊花链。如果使用外部菊花链,则必须遵循第47页“交流特性,读/写定时表6,注释5”中的公式,以计算所需菊花链的稳定时间。

写入寄存器位函数

读取寄存器

scc包含10个读取寄存器(11个,计算每个信道中的接收缓冲器(rr8))。其中四个可以读取以获取状态信息(rr0、rr1、rr10和rr15)。读取两个寄存器(RR12和RR13)来学习波特率发生器时间常数。rr2包含未修改的中断向量(通道a)或由状态信息修改的向量(通道b)。RR3包含中断挂起(IP)位(仅通道A–图19)。rr6和rr7包含sdlc帧状态fifo中的信息,但仅在设置wr15 d2时读取

读取寄存器0读取寄存器3

读取寄存器位函数

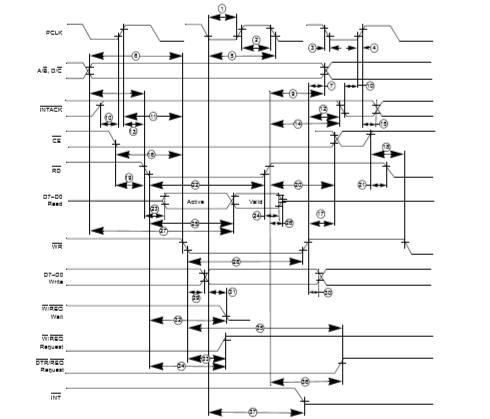

Z85C30--ic/" title="Z85C30-">Z85C30-ic/" title="Z85C30">Z85C30定时

scc从wr和rd生成与pclk相关的内部控制信号。pclk与wr和rd没有相位关系,产生内部控制信号的电路为亚稳态条件消失提供了时间。这会产生与pclk相关的恢复时间。恢复时间仅适用于涉及scc的总线事务之间。

正确操作所需的恢复时间是从wr的下降沿开始规定的

或涉及scc的第一事务中的rd到涉及scc的第二事务中的wr或rd的下降沿。无论访问哪个寄存器或通道,此时间必须至少为3个PCLK。

Z85C30--ic/" title="Z85C30-">Z85C30-ic/" title="Z85C30">Z85C30计时如下所述:

读取周期计时

写入周期计时

中断确认周期计时

读取周期计时。A/B和D/C上的地址和状态

在整个周期内,Intack必须保持稳定。如果ce在rd下降之后下降,或者ce上升

在rd上升之前,有效rd缩短。

读取周期计时

写入周期计时。A/B和D/C上的地址和状态

在整个周期内,Intack必须保持稳定。如果ce在wr下降之后下降,或者ce上升

在wr上升之前,有效wr缩短。数据必须在wr上升沿之前有效。

写入周期计时

中断确认周期计时。时间间隔

向下移动,rd的下降沿,内部和外部iei/ieo菊花链固定。

如果SCC中有一个挂起的中断,并且当RD下降时IEI为高,则确认周期用于SCC。在这种情况下,SCC可编程为响应

通过将其中断向量放在d7-d0上降低rd。然后在服务锁存器内部设置适当的中断。

如果不使用外部菊花链,则需要AC参数38来解决SCC内部的中断优先级菊花链。如果使用外部菊花链,则必须遵循第47页“交流特性,读/写定时表6,注释5”中的公式,以计算所需菊花链的稳定时间。

中断确认周期计时

Z80C30--ic/" title="Z80C30-">Z80C30-ic/" title="Z80C30">Z80C30定时

SCC从与PCLK相关的AS和DS生成内部控制信号。由于pclk与as和ds没有相位关系,产生这些内部控制信号的电路必须为亚稳态条件消失提供时间。这会产生与pclk相关的恢复时间。恢复时间仅适用于涉及scc的总线事务之间。正确操作所需的恢复时间是规定的-

从涉及scc的第一交易中的ds的下降沿到涉及scc的第二交易中的ds的下降沿。Z80C30--ic/" title="Z80C30-">Z80C30-ic/" title="Z80C30">Z80C30设备的计时如下所述:

读取周期计时

写入周期计时

中断确认周期计时

读取周期计时

读取寄存器位函数

Z85C30--ic/" title="Z85C30-">Z85C30-ic/" title="Z85C30">Z85C30定时

scc从wr和rd生成与pclk相关的内部控制信号。pclk与wr和rd没有相位关系,产生内部控制信号的电路为亚稳态条件消失提供了时间。这会产生与pclk相关的恢复时间。恢复时间仅适用于涉及scc的总线事务之间。

正确操作所需的恢复时间是从wr的下降沿开始规定的

或涉及scc的第一事务中的rd到涉及scc的第二事务中的wr或rd的下降沿。无论访问哪个寄存器或通道,此时间必须至少为3个PCLK。

Z85C30--ic/" title="Z85C30-">Z85C30-ic/" title="Z85C30">Z85C30计时如下所述:

读取周期计时

写入周期计时

中断确认周期计时

读取周期计时。A/B和D/C上的地址和状态

在整个周期内,Intack必须保持稳定。如果ce在rd下降之后下降,或者ce上升

在rd上升之前,有效rd缩短。

读取周期计时

写入周期计时

A/B和D/C上的地址和状态

在整个周期内,Intack必须保持稳定。如果ce在wr下降之后下降,或者ce上升

在wr上升之前,有效wr缩短。数据必须在wr上升沿之前有效。

写入周期计时

中断确认周期计时。时间间隔

向下移动,rd的下降沿,内部和外部iei/ieo菊花链固定。

如果SCC中有一个挂起的中断,并且当RD下降时IEI为高,则确认周期用于SCC。在这种情况下,SCC可编程为响应

通过将其中断向量放在d7-d0上降低rd。然后在服务锁存器内部设置适当的中断。

如果不使用外部菊花链,则需要AC参数38来解决SCC内部的中断优先级菊花链。如果使用外部菊花链,则必须遵循第47页“交流特性,读/写定时表6,注释5”中的公式,以计算所需菊花链的稳定时间。

中断确认周期计时

Z80C30--ic/" title="Z80C30-">Z80C30-ic/" title="Z80C30">Z80C30定时

SCC从与PCLK相关的AS和DS生成内部控制信号。由于pclk与as和ds没有相位关系,产生这些内部控制信号的电路必须为亚稳态条件消失提供时间。这会产生与pclk相关的恢复时间。恢复时间仅适用于涉及scc的总线事务之间。正确操作所需的恢复时间是规定的-

从涉及scc的第一交易中的ds的下降沿到涉及scc的第二交易中的ds的下降沿。Z80C30--ic/" title="Z80C30-">Z80C30-ic/" title="Z80C30">Z80C30设备的计时如下所述:

写入周期计时

中断确认周期计时

读取周期计时。AD7-AD0上的地址和CS0的状态

而内装则被AS的上升沿锁住。R/W必须高才能指示读取周期。CS1也必须高,才能进行读取循环。scc中的数据总线驱动程序然后在DS低时启用。

读取周期计

写入周期计时。AD7-AD0上的地址和CS0的状态

而内装则被AS的上升沿锁住。R/W必须低才能指示写入周期。cs1必须为高,写入周期才会发生ds low将数据选通到

写入周期计时

中断确认周期计时

AD7–AD0上的地址以及CS0和Intack的状态由AS的上升沿锁定。如果intack很低,则忽略地址和cs0。在中断确认周期期间,R/W和CS1的状态也被忽略。在as的上升沿和ds的下降沿之间,内部和外部iei/ieo菊花链固定。如果有

SCC中的中断挂起,当DS下降时IEI高,确认周期是为SCC准备的。在这种情况下,通过将SCC的中断向量设置在D7-d0上并在服务锁存器下内部设置适当的中断,SCC被编程为响应RD低。

中断确认周期计时

电气特性

Z80C30--ic/" title="Z80C30-">Z80C30-ic/" title="Z80C30">Z80C30和Z85C30--ic/" title="Z85C30-">Z85C30-ic/" title="Z85C30">Z85C30设备的电气特性在以下章节中描述。

绝对最大额定值

大于表3所列的应力可能会对设备造成永久性损坏。这只是应力额定值。在本规范操作章节所述条件之上的任何条件下,设备的操作都不是隐含的。长期暴露在绝对最大额定条件下可能会影响设备的可靠性。

Z85C30--ic/" title="Z85C30-">Z85C30-ic/" title="Z85C30">Z85C30读/写时序图

Z85C30--ic/" title="Z85C30-">Z85C30-ic/" title="Z85C30">Z85C30读/写定时参数