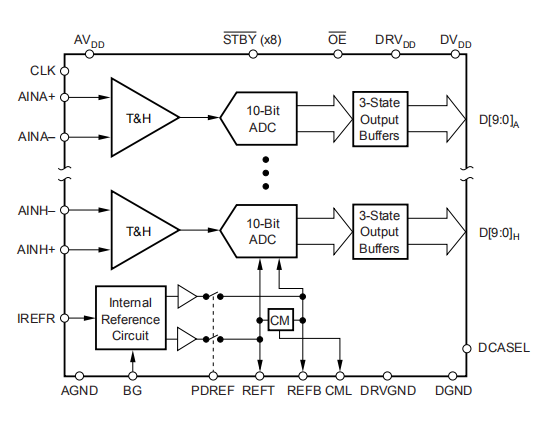

ADS5120是8通道,10位,40MSPS,1.8V CMOS模拟双数字转换器(ADC)

日期:2019-12-24特征

8个差分模拟输入;1VPP差分输入范围;内部/外部电压参考;模拟/数字电源1.8V;数字I/O电源1.8V/3.3V;积分非线性:±0.8LSB;信噪比:58dB,fIN=20MHz;无杂散动态范围:72dB at;fIN=20MHz;794mW功耗;单独通道断电;257-铅,0.8球距,塑料MicroSTAR BGA™(16•16毫米)。

应用

便携式超声波;便携式仪器。

说明

ADS5120是一种低功耗、8通道、10位、40MSPS CMOS模数转换器(ADC),它由单个1.8V电源供电,同时提供1.8V和3.3V数字I/O灵活性。单端输入时钟用于同时采样多达八个模拟差分输入通道。灵活的占空比调节电路(DCASEL)允许使用非50%的时钟占空比。单个备用管脚允许用户关闭任意数量的ADC。在ADC前加入采样保持级,并使用数字纠错电路产生最终的数字码。可以绕过内部参考,使用外部参考,以满足应用的精度和温度漂移要求。八个通道上的10位并行总线具有三态输出。

ADS5120的速度、分辨率和低功耗使其非常适合在低功耗环境中需要高密度信号处理的应用。

ADS5120的特点是在0°C到70°C的温度下工作。

应用程序信息

变频器运行

ADS5120是一个8通道同步采样ADC。它的低功耗(100mW/通道)和高采样率40MSPS是采用先进的低压CMOS工艺构建的最先进的开关电容流水线结构实现的。ADS5120主要由+1.8V单电源供电。为了增加接口的灵活性,数字I/O电源可以设置为+ 1.8V或3.3V。每个通道的ADC核心由10个流水线级组成。每10级产生一个数字位。利用上升和下降的时钟边缘每半个时钟通过管道传播样本,总共五个时钟周期。需要两个额外的时钟周期来通过数字纠错逻辑和输出锁存器来传递样本数据。因此,总的管道延迟或数据延迟为7个时钟周期。由于一个公共时钟控制所有八个信道的定时,所以模拟信号和并行端口上同时更新的数据被同时采样。

模拟输入

ADS5120的每个通道的模拟输入由使用开关电容技术实现的差分跟踪和保持放大器组成,如图1所示。这种差分输入拓扑和紧密匹配的电容器产生高水平的交流性能,高达高采样率。

当轨道和保持放大器处于轨道模式时,转换电流对输入采样电容器进行充放电。ADS5120的输入阻抗也是采样率的函数。随着采样频率的增加,输入阻抗以1/fs的速率线性下降。对于大多数应用来说,这并不代表一个限制,因为阻抗保持相对较高,例如,在最大采样速率为40MSPS的情况下,大约为83KΩ。对于使用运放驱动ADC的应用,建议在放大器输出和转换器输入之间添加一个串联电阻,通常为10Ω至50Ω。这将隔离转换器的电容输入与驱动器,并避免潜在的增益峰值,或不稳定。

输入偏置

ADS5120由一个+1.8V模拟电源工作,要求每个模拟输入(AIN+,AIN-)由适当的共模电压进行外部偏置。例如,共模电压为+1V时,1VPP满标度差分输入信号将围绕+1V对称摆动,或在0.75V和1.25V之间摆动。这由两个参考电压决定,即上参考电压(REFT)和下参考电压(REFB)。通常,输入共模电平与参考电压相关,定义为(REFT+REFB)/2。该参考中点位于CML引脚处,可直接用于输入偏置目的。CML处的电压将假定为内部或外部参考操作的中点。在任何情况下,建议使用陶瓷0.1μF电容器绕过CML引脚。

输入阻抗

由于采用了开关电容输入跟踪保持放大器,ADS5120的输入阻抗具有有效的电容性,驱动电源需要提供足够的。

驱动模拟输入与单端差分

ADS5120的模拟输入允许单端或差分驱动。ADS5120的差分操作需要一个输入信号,该信号由一个同相部分和一个同时应用于输入(AIN+,AIN–)的180°异相部分组成。ADS5120的满标度输入范围由根据FSR=2 x的参考电压定义(参考-参考B)。对于典型的1VPP范围,差分输入配置只要求每个输入看到0.5VPP的信号摆动。在单端配置中操作转换器需要对所选输入应用完整的1VPP摆动。差分操作具有许多优点,在大多数应用中,这将有助于实现ADS5120的最佳动态性能:

(1)、信号摆幅是单端操作所需摆幅的一半,因此在保持信号源良好线性性能的同时,对实现要求较低。

(2)、减小的信号摆幅允许接口电路有更大的净空,因此可以更广泛地选择最合适的驱动器运放。

(3)、偶次谐波最小化。

(4)、基于转换器的共模输入抑制,提高抗噪性。

对于单端模式,信号被施加到其中一个输入端,而另一个输入端被直流电压偏置到所需的共模电平。这两个输入在阻抗和性能方面是相同的。然而,将信号应用于互补输入(AIN-)而不是AIN+输入将反转输入信号相对于输出代码的方向。例如,如果输入驱动器使用输入AIN在反转模式下工作,这可能会有帮助,因为信号输入将使信号的相位恢复到其原始方向。

输入驱动程序配置

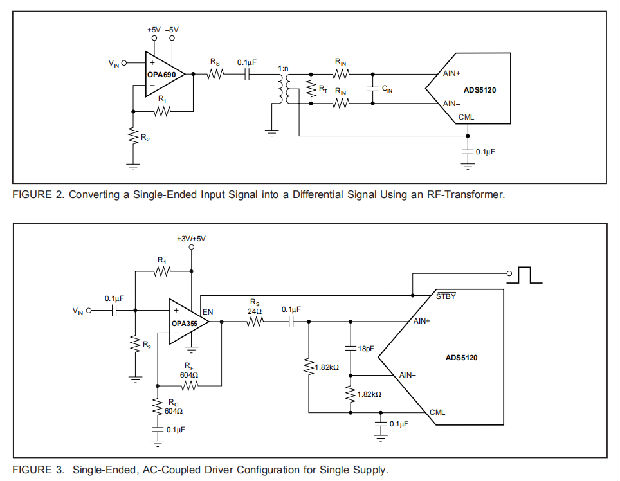

变压器耦合接口

如果应用程序需要从单端源进行信号转换以差分驱动ADS5120,则RFtransformer可能是一个很好的解决方案。所选变压器必须有一个中心抽头,以便施加偏置转换器输入所需的共模直流电压。中心抽头接地将在二次绕组上产生差动信号摆动。考虑一个升压变压器,在不引入其他噪声源的情况下利用信号放大。此外,来自源的减少的信号摆动可导致改善的失真性能。

差分输入配置可提供在宽输入频率范围内获得良好SFDR性能的显著优点。在这种模式下,ADS5120的两个输入(AIN+和AIN-)都会看到匹配的阻抗。图2显示了建议的变压器耦合接口电路的示意图。R-C低通的分量值可以根据期望的滚转频率进行优化。

单端交流耦合驱动器

图3的电路显示了在单端配置中驱动ADS5120的输入的示例。信号在驱动器放大器和转换器输入(AIN+)之间进行交流耦合。这允许为ADC和运算放大器分别设置所需的共模电压。单电源运放在中间电源由两个电阻在其非垂直输入端连接偏置。将每个输入连接到CML管脚为ADS5120的输入提供所需的共模电压。在这里,两个电阻值相等,确保输入看到密切匹配的源阻抗。如果运算放大器具有禁用功能,它可以很容易地与ADS5120信道(STBY)的掉电引脚。在图3所示的电路示例中,OPA355 EN引脚是直接连接到STBY引脚,允许整个电路的断电模式。其他适用于单电源驱动器应用的合适运算放大器包括OPA634、OPA635或OPA690,例如。

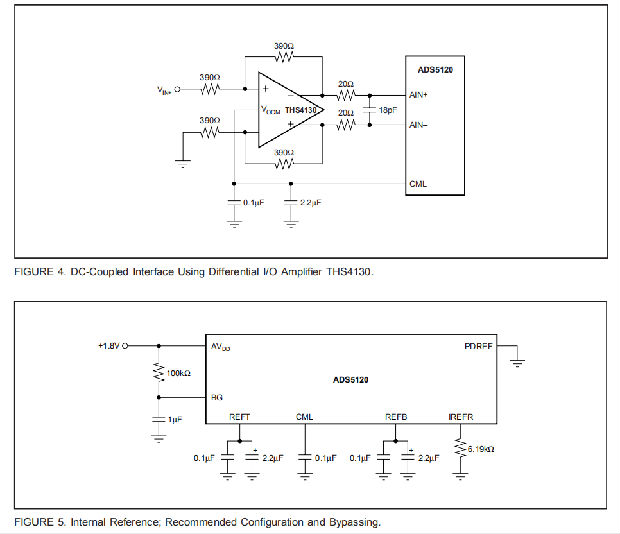

带差动放大器的直流耦合接口

差分输入输出放大器可以简化需要输入-直流耦合的驱动电路。灵活的配置,这样的放大器可以用于单端到差分转换,允许信号放大,并在ADC之前进行滤波。图4显示了使用THS4130放大器的一种可能的电路实现。在这里,放大器以+1的增益工作。CML引脚上的共模电压可以方便地连接到放大器VOCM引脚,以设置ADS5120所需的输入偏置。

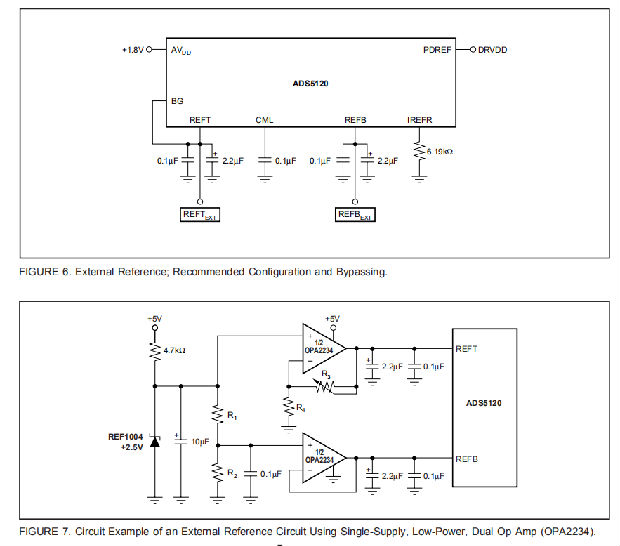

为了使ADS5120及其参考信号正常工作,必须将外部6.19kΩ电阻器从IREFR引脚连接到模拟接地(AGND)(如图5所示)。当1%的电阻公差足够时,偏离该电阻值将导致性能改变和降低。

为了确保在任何参考配置下正常工作,必须在所有参考引脚上提供可靠的旁路,以便将时钟馈通保持在最小值。图5显示了推荐的解耦方案。使用0.1μF的低电感陶瓷电容器可以获得良好的性能。根据应用情况,添加钽电容器(1μF至10μF)可导致性能改进。所有旁路电容器应尽可能靠近各自的引脚。

ADS5120的内部基准电路由带隙基准电压源、上下基准驱动器和电阻基准梯形图组成。相应的参考管脚是REFT、REFB、CML、IREFR、BG和PDREF。为了启用内部引用,pin PDREF必须处于逻辑低位=0。此外,带隙引脚BG必须具有到AVDD的100kΩ上拉电阻器,并且应与1μF电容器分离。参考电路为八个通道中的每一个提供参考电压。

参考缓冲器可用于向外部电路提供高达1毫安(接收器和源)。共模电平输出引脚CML表示内部电阻梯形图的中点,是无缓冲节点。应避免加载该引脚,因为这将导致转换器线性度降低。

使用外部引用

对于更大的设计灵活性,内部参考可以被禁用和外部参考电压使用。对于需要更高精度或改进温度性能的应用,可以考虑使用外部参考。特别是在多通道应用中,使用公共外部参考信号有助于更好地匹配转换器之间的满标度范围。

将ADS5120设置为外部参考模式需要将PDREF引脚设置为高电平。此外,引脚BG和REFT必须连接在一起(如图6所示)。在CML引脚的共模电压将维持在大约施加的参考电压的中点,根据CML(VRFT-VReFB)/ 2。当ADS5120在外部参考模式下工作时,用于REFT和REFB的内部缓冲放大器被禁用。外部参考电路必须设计为驱动位于REFT和REFB引脚之间的内部参考梯形图(80Ω)。例如,设置REFT=+1.25V和REFB=+0.75V将需要至少0.5V/80Ω=6.25mA的电流驱动能力。只要外部顶部参照(REFTEXT)的值保持在+1.15V到+1.35V的范围内,外部底部参照(REFBEXT)保持在+0.65V到+0.85V的范围内(如图7所示),外部参照就可以改变。

数字输入输出时钟输入

时钟输入设计为在+1.8V或+3.3V CMOS逻辑电平下工作。时钟电路内部连接到DRVDD电源。因此,输入高电平和低电平将根据应用的DRVDD电源而变化;请参阅直流特性表。由于该流水线ADC中使用了时钟的两个边缘,因此理想的时钟应该是占空比为50%的方波逻辑信号。

由于这种情况不容易满足,ADS5120具有一个内部时钟调节电路,可以通过占空比调节引脚(DCASEL)激活。

DCASEL引脚是一个逻辑输入,其逻辑电平与DVD电源相关(仅限+1.8V):

a)、DCASEL=低(GND);在此模式下,时钟条件电路被禁用。如果应用的时钟信号是占空比为50%的方波时钟,或者占空比保持在48%到52%的范围内,则使用此设置。

b)、DCASEL=高(DVD D);在此模式下,时钟调节电路启用。如果应用的外部时钟信号是不符合上述标准但占空比在30%到70%范围内的方波时钟,则使用此设置。

最小采样率

ADS5120的流水线结构在内部轨道和保持级使用开关电容技术。在每个时钟周期中,代表捕获信号电平的电荷在ADC流水线核心内移动。高采样率要求使用非常小的电容值。为了保持较低的下垂误差,电容器需要最小的刷新率。为了保持采集到的样品电荷的完全准确度,ADS5120的采样时钟不应低于规定的最小1MSPS。

数据输出格式

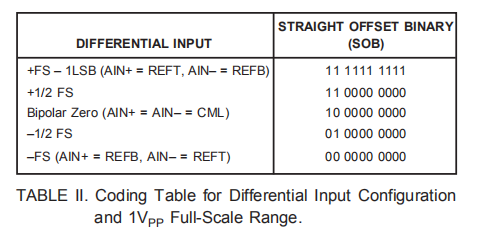

ADS5120的输出数据格式是正直偏移二进制(SOB)码。表一和表二显示了单端差分信号的输出编码。对于所有数据输出通道,msb位于D9x管脚。

数字输出加载

减小数字输出端的电容负载对于获得最佳性能非常重要。总负载电容通常由两个源组成:下一级输入电容和寄生/印刷电路板(PDB)电容。建议尽可能降低数据线上的总电容负载(≤15pF)。当数字输出改变状态时,较高的电容负载将导致较大的动态电流。大电流浪涌可能会导致反馈到ADS5120的模拟部分并影响性能。如有必要,可使用靠近转换器输出引脚的外部缓冲器或锁存器来最小化电容负载。建议使用的设备是SN74AVC16827(20位缓冲/驱动器),它是高级极低电压CMOS逻辑家族(AVC)的成员。使用这样的逻辑装置还可以提供附加的好处,将ADS5120与总线上的任何数字噪声活动隔离,从而耦合回高频噪声。在数据线中使用串联电阻(≤100Ω)也可能有助于某些应用。这将提供电流限制,并减少任何现有的过冲或下冲。

输出启用

ADS5120提供一个输出使能管脚(OE),用于同时控制所有通道的数字输出。一个OE引脚上的低(L=0)电平将激活所有通道变频器正常工作。将OE引脚设为高(H=1)将禁用或三态所有输出频道。注意,OE引脚没有内部上拉电阻器,因此需要定义一个应用。运行经验和输出总线启用/禁用时间之间的时序关系如时序图所示。

通电顺序

理想情况下,ADS5120的三个主电源应同时使用和提升。如果无法确保这一点,建议执行以下通电顺序:

1、平均折旧率(+1.8典型值)

2、DVD驱动器(+1.8类型)

3、DRVDD(+3.3类型)

在ADS5120通电期间,时钟信号也应采用适当的逻辑电平。偏离此通电顺序可能导致设备进入一种模式,使得数字输出不接近全部指定的输出电平。

断电(待机)

ADS5120具有断电功能八个频道中的每一个。标记为备用管脚,正常工作模式是当该管脚连接到逻辑高(H=1)时。如果相应的STBY引脚连接到逻辑低(L=0),则选定的ADC通道将处于断电模式。STBY管脚的逻辑电平取决于DRVDD电源。掉电功能控制内部偏置节点,因此,转换器管道中存在的任何数据都将无效。这与断电期间时钟是否保持应用无关。通电后,新的有效数据将在至少七个时钟周期后可用。值得注意的是STBE引脚不用于在ADS5120的八个通道之间动态复用。

数字输出驱动电源

ADS5120使用输出逻辑驱动器DRVDD的专用电源连接,以及标记为DRGND的数字驱动器接地连接。

将DRVDD处的电压设置为+3.3V或+1.8V时,输出逻辑电平将相应地设置,从而允许ADS5120直接连接到选定的逻辑系列。输出级被设计为提供足够的电流来驱动各种逻辑族。但是,建议使用ADS5120和+1.8V驱动电源。这将降低由于较低的输出摆幅而导致的输出级功耗,并减少电源线上的电流故障,否则可能影响转换器的交流性能。在某些应用中,使用附加电容器或pi滤波器来分离DRVDD电源可能是有利的。

接地和去耦

正确的接地和旁路、短引线长度和接地平面的使用对于高频设计特别重要。建议使用多层印刷电路板以获得最佳性能,因为它们具有显著的优点,如最小化接地阻抗、通过接地层分离信号层等。ADS5120应视为模拟组件。只要有可能,电源引脚就应该由模拟电源供电。这将确保最一致的结果,因为数字电源线往往携带高水平的噪声,否则将耦合到转换器和降低可实现的性能。接地引脚应直接连接到覆盖转换器下PCB区域的模拟接地平面。在设计布局时,重要的是保持模拟信号轨迹与任何数字线路分离,以防止噪声耦合到模拟信号路径上。由于其高采样率,ADS5120产生的高频电流瞬变和噪声(时钟馈通)反馈到电源线和参考线。这要求所有的电源和参考引脚都被充分旁路。在大多数情况下,每个引脚的0.1μF陶瓷芯片电容器足以在宽频率范围内保持低阻抗。它们的有效性在很大程度上取决于接近个别供应引脚。因此,它们应尽可能靠近电源引脚。此外,更大的双极性电容器(1μF至22μF)应在转换器电路附近放置在PCB上。

用MICROSTAR-BGA封装的PCB版图

ADS5120封装在基于聚酰亚胺薄膜的芯片级封装(CSP)中。与大多数csp一样,焊料合金球被用作封装基板和封装焊接在其上的PCB之间的互连。有关这些封装的详细信息,请参阅文献编号SSYZ015B,MicroStar BGA封装参考指南,其中说明了将MicroStar BGA封装集成到PCB设计中时需要考虑的具体问题。

术语

模拟带宽

模拟输入频率,在该频率下,基频的频谱功率(由FFT分析确定)降低3dB。

孔径延迟

时钟上升沿50%点与模拟输入采样时刻之间的延迟。

孔径不确定度(抖动)

孔径延迟的采样-采样变化。

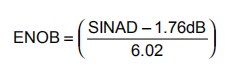

有效位数(ENOB)

ENOB根据测量的SINAD计算,公式如下:

增益误差

增益误差是第一个和最后一个代码转换之间的实际差和第一个和最后一个代码转换之间的理想差的偏差。

增益匹配

相邻信道间增益误差的变化。

谐波失真,秒

二次谐波分量的均方根信号振幅与均方根值的比值,用dBc表示。

谐波失真,第三

三次谐波分量的均方根信号振幅与均方根值之比,用dBc表示。

互调失真

双音IMD是输入音与最差三阶(或更高)互调产物的分贝比值。单个输入音电平为-6.5dB满标度,其包络为-0.5dB满标度。

偏移误差(零刻度误差)

当模拟值高于负满标度1/2 LSB时,应发生第一次转换。偏移误差定义为实际过渡点与该点的偏差。

偏移匹配

相邻通道间偏移误差的变化。

电源抑制比

输入偏移电压变化与电源电压变化的比率。

信噪比和失真(SINAD)

有效值信号振幅(设为满标度以下0.5dB)与所有其他谱分量之和的有效值之比,包括谐波,但不包括直流电。

信噪比(无谐波)

有效值信号振幅(设为满标度以下0.5dB)与所有其他谱分量之和的有效值之比,不包括前五次谐波和直流电。

无杂散动态范围(SFDR)

峰值杂散频谱分量的均方根信号振幅与均方根值之比。峰值杂散分量可以是谐波,也可以不是谐波。可以用dBc(即,随着信号电平降低而降低)或dBFS(始终与转换器满标度相关)报告。