YSS920B前夕用于各种音效的32位DSP引擎

日期:2019-4-25大纲

YSS920B是一款专为声场处理而设计的32位数字信号处理器。作为一个经过环绕声解码后的后处理DSP,YSS920B可以处理各种声场通过用户程序进行各种模拟环绕和虚拟环绕,可提供广泛的功能声场对音频设备的影响变化。

特征

YSS920B具有以下功能:

与用于DSP程序的YSS922 / 932的SubDSP部分基本兼容通过32位浮点运算实现高精度处理能够通过将外部程序下载到内置RAM来处理各种声音效果

16通道处理能力(输入:16ch,输出:16ch)

每个通道上的零数据检测功能

多个YSS920B之间的32位数据传输能力通过控制寄存器设置,可连接到大多数类型的ADC,DAC和DIR内置延迟存储器,32位×1024字(fs = 48 kHz时最大21.3 ms)

与外部DRAM连接时,能够执行最长2.73秒的延迟(fs = 48 kHz)

SRAM

支持32 kHz至192 kHz的采样频率

DSP部分规格

内部工作频率:30.72至50.00 MHz

数据总线宽度:32位

MAC:32位(浮点)×16位(定点)+ 49位→49位

程序RAM:50位×1024字

系数RAM:16位×1024字

最多可使用20个通用输入/输出终端

电源电压:2.5 V(内部和PLL电路),3.3 V(I / O)

硅栅CMOS工艺

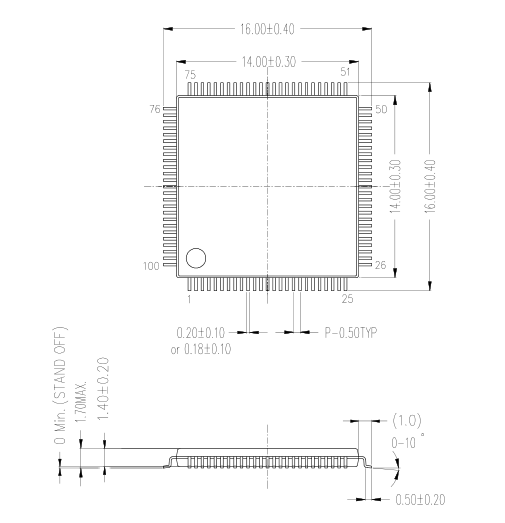

无铅100引脚SQFP封装:YSS920B-SZ

应用

AV放大器和音频混合器的声场处理,例如:

模拟环绕大厅,剧院,教堂,体育馆,迪斯科舞厅,爵士乐和现场

虚拟环绕

低音管理

LPF,HPF,均衡器等的过滤过程

推子和液位计

产生白噪声,粉红噪声,正弦波等。

YSS920B和YSS920之间的区别

主要差异如下。 请充分检查您的问题是否没有问题

当您用YSS920B替换YSS920时的产品。

项目YSS920B YSS920

1内部工作频率30.72至50.00MHz 30.72至40.96MHz

2功耗(V DD1)45mW(典型值)/ 65mW(最大值)30mW(典型值)/ 45mW(最大值)

3功耗(V DD2 / AV DD)120mW(典型值)/ 145mW(最大值)80mW(典型值)/ 115mW(最大值)

4电源启动顺序)定义(参见p18上电)未定义

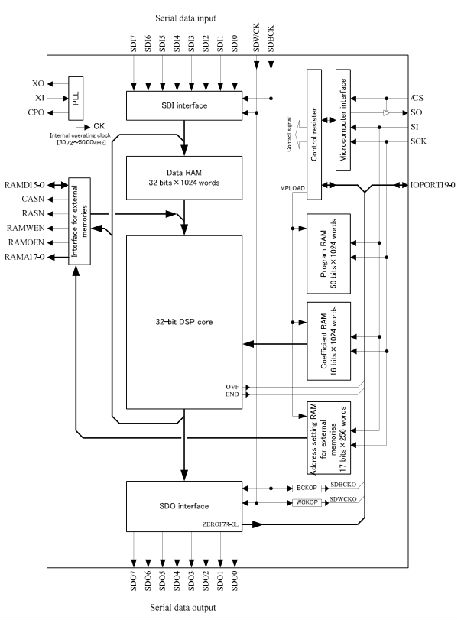

框图

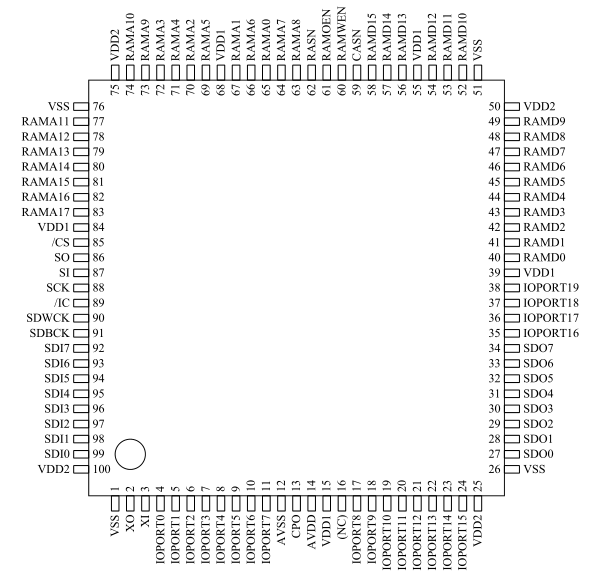

引脚配置

引脚说明

串行数据接口

SDI7-0

该LSI的PCM数据输入引脚。最多可输入16个PCM数据通道。

将未使用的引脚连接到VSS。

通过设置SDI寄存器选择输入格式。

SDO7-0

DSP处理的PCM信号的输出引脚。最多可输出16个PCM数据通道。

通过设置SDO寄存器选择输出格式。

SDBCK和SDWCK

用于SDI输入和SDO输出的时钟输入引脚。

输入64fs至SDBCK和fs至SDWCK的时钟信号。

外部存储器接口

RAMA17-0,RAMD15-0,RAMWEN,RAMOEN,CASN和RASN

用于连接外部存储器以进行数据延迟的引脚。

微处理器接口

/ CS,SCK,SI和SO

4线串行接口,用于读/写控制寄存器和程序下载。

有关格式,请参阅“■微处理器接口格式”。

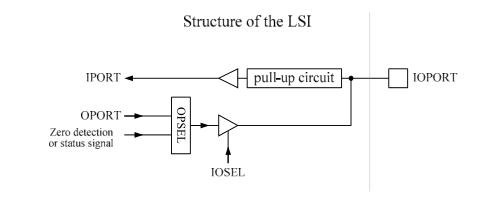

通用输入/输出引脚

IOPORT19-0

IOPORT0至IOPORT19可用作通用输入/输出端口。

通过设置IOSEL 19-0位选择是将引脚用作输入引脚(IPORT)还是输出引脚(OPORT)

IOSEL寄存器(IOSEL_H,IOSEL_M和IOSEL_L)。

如果设置为输出引脚(OPORT),则可以选择是否将设置的值输出到寄存器(OPORT_H,

OPORT_M和OPORT_L)或通过设置OPSEL 19-0位寄存器输出各种状态信号

(OPSEL_H,OPSEL_M和OPSEL_L)。

IOPORT引脚的功能可以设置如下:注1)芯片地址设定引脚(IOPORT 15-12)

这些引脚也用作芯片地址设置引脚:

IOPORT 12 -----芯片地址0(CA0)

IOPORT 13 -----芯片地址1(CA1)

IOPORT 14 -----芯片地址2(CA2)

IOPORT 15 -----芯片地址3(CA3)

注2)ZEROF输出引脚(IOPORT 15-0)

通过设置IOSEL和OPSEL,IOPORT 15-0作为SDO的数字零检测引脚运行输出信号。

如果SD0输出信号连续保持数字零,表示由指定的样本数ZEROB寄存器,相应通道的标志输出引脚设置为H.此标志输出引脚可以用于DAC之后的模拟静音。

通道对应的引脚如下:

注3)各种状态信号输出引脚通过设置IOSEL和OPSEL,将从每个引脚输出以下状态信号:

IOPORT16 ----- OVF

IOPORT17 -----结束

IOPORT18 ----- SDBCKO(64fs时钟)

IOPORT19 ----- SDWCKO(fs clock)

OVF如果DSP的运算结果发生溢出,则OVF设置为H.H间隔是从溢出的发生到下一个PCM的输出开始来自SDO接口的样本。当下一个PCM采样输出开始时,OVF重置为L.该引脚用于DSP编程和调试。

当DSP程序计数器激活时,END END设置为H.所有流程都设置为L.已完成,程序计数器停止。当程序运行正常时,每个样品的引脚始终设置为L。如果不是,则表示程序没有完成正确到最后。该引脚用于DSP编程和调试。

SDBCKO此引脚输出与SDO输出信号同步的64fs时钟。这个时钟可以用作后续阶段的设备为64fs时钟。 SDBCKO时钟的极性可以是通过设置SDO寄存器的BCKOP来选择。

SDWCKO该引脚输出与SDO输出信号同步的fs时钟。这个时钟可以用作fs为后续阶段的设备提供时钟。 SDWCKO时钟的极性可以是通过设置SDO寄存器的WCKOP来选择。

IOPORT 19-0每个引脚的LSI结构如下所示:

时钟 XI和XO用于连接晶体振荡器(12.288至15.000 MHz)的引脚。 使用带基波的晶体振荡器波。如果使用外部时钟,请将其连接到XI。内部操作时钟(ck)通过该晶体振荡器的振荡频率和设置来设置ERAM寄存器的CKUP位。

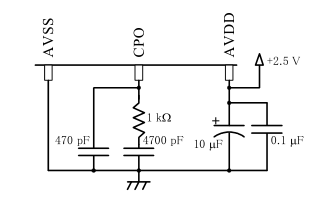

CPO,AVDD和AVSS用于连接PLL外部元件的引脚,用于在DSP部分产生时钟脉冲。在CPO附近连接电阻和电容,如下所示。在AVDD和AVSS之间的引脚附近连接去耦电容。

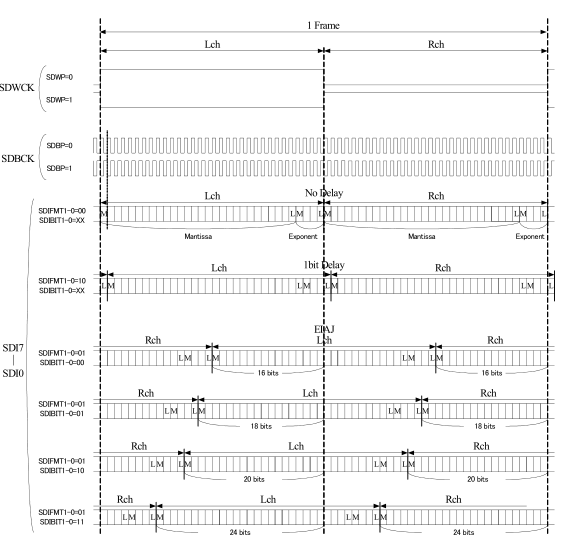

串行数据接口的格式PCM信号的输入/输出通过以下方式执行:·SDI接口,和·SDO接口。1)SDI接口:(串行数据输入)根据SDI寄存器的设置,串行数据的输入格式如下。无论设置如何,SDI7-0引脚的输入信号都被处理为由28位组成的32位数据尾数和4位指数

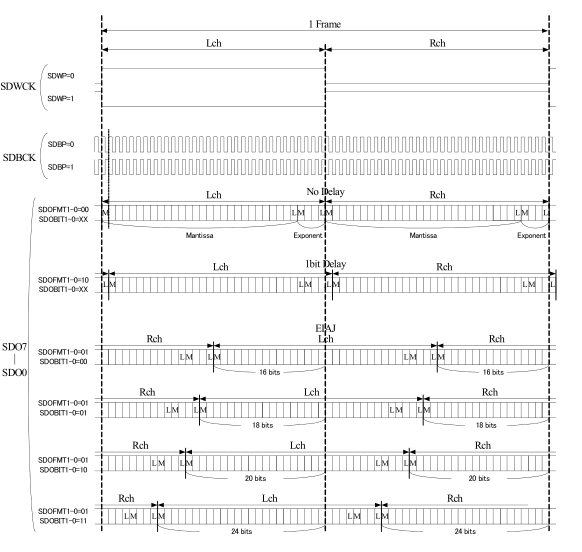

SDO接口:(串行数据输出)根据SDO寄存器的设置,串行数据的输出格式如下。无论设置如何,始终输出由28位尾数和4位指数组成的32位数据SDO7-0引脚。将SDO7-0输出传递给其他设备(如D / A)时,请指定定点数(线性)DSP程序中的输出。 当使用多个YSS920B时,32位数据由28位尾数和可以通过指定浮点(浮点)输出来传递4位指数。

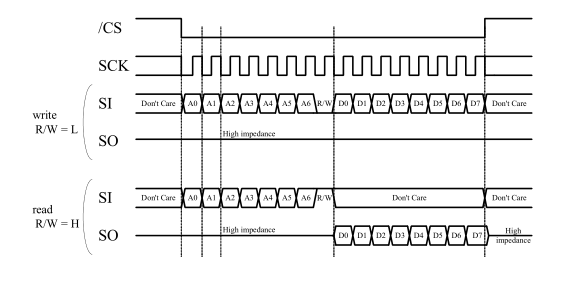

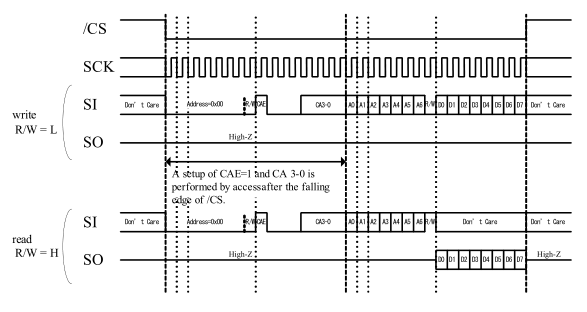

微处理器接口格式如图所示,通过4线串行接口读取/写入内部控制寄存器下面:1)当/ CS仅由一个设备使用时

仅当满足以下所有条件时,才将SO设置为输出模式:·当/ CS = L时·读取有效的地址设置时·在数据输出时序(8位)期间。在所有其他情况下,它被设置为High-Z,因此可以与具有相似的设备共享SO,SI和SCK接口。 当使用多个YSS920B时,也可以通过指定CHIP ADR寄存器来共享/ CSCA3-0。 请参见下一节“2)”。如果通用输入/输出引脚(IOPORT19-0)用作输入引脚(IPORT),那么IOPORT将通过SO读取上面所示的“R / W”期间的(IPORT)值。如果它用作输出引脚(OPORT),则IOPORT(OPORT)输出将在此时切换上面显示的“D7”上的SCK上升沿。[注意]初始清除期间将/ CS设置为H(/ IC = L)。

/ CS与多个设备共享时当使用多个YSS920B或/ CS与其他LSI共享时,请务必设置CAE = 1和CA 3-0紧接在/ CS的下降沿之后,如下图所示

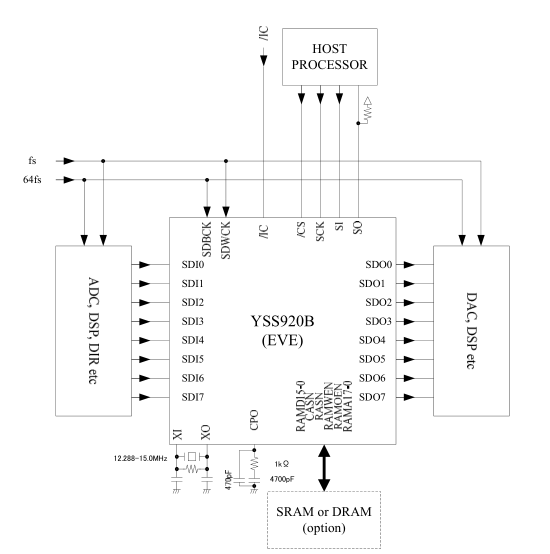

连接图示例1)使用一个YSS920B时使用一个YSS920B时的基本连接示例如下所示:

使用一个YSS920B时,无需设置芯片地址(CA3-0)。SO引脚可能变为高阻态。 因此,某些系统可能需要上拉电阻。在需要具有极性反转的位时钟的ADC和DAC等外围设备上,请使用通过设置IOSEL18 = 1,OPSEL18 = 1和BCKOP = 1,从IOPORT18引脚输出SDBCKO

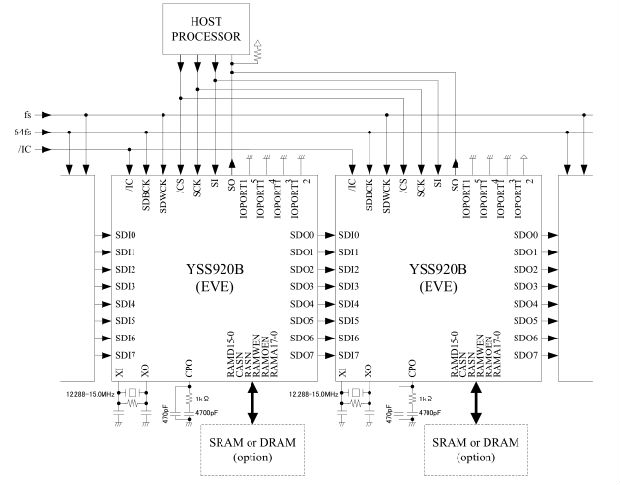

使用多个YSS920B时使用多个YSS920B时的基本连接示例如下所示:

通过将芯片地址(CA3-0)设置到IOPORT15-12引脚,可以共享/ CS。将器件切换为控制时,重写控制寄存器地址0x00(CA3-0)。例如,在上面的情况中:要控制左设备,请将寄存器设置为CAE = 1和CA3-0 = 0000,要控制正确的设备,请将寄存器设置为CAE = 1且CA3-0 = 0001。? 在需要具有极性反转的位时钟的ADC和DAC等外围设备上,请使用通过设置IOSEL18 = 1,OPSEL18 = 1和BCKOP = 1,从IOPORT18引脚输出SDBCKO。? SO引脚可能变为高阻态。 因此,某些系统可能需要上拉电阻。

包装尺寸