vecana01模拟数字转换器

日期:2019-9-9功能应用程序

10全差分输入交流电机速度控制

5路同步采样三相功率控制

加2同步采样*

渠道

振动分析

3个同步12位ADC

12.8s吞吐率

数字可选输入范围

±5V电源IUP/N

串行数字输入/输出A1P/NADOUT1

7个签名,3个数字签名A2P/N可编程窗口比较器体外受精/胚胎移植

描述B1P/NADOUT2

B2P/N

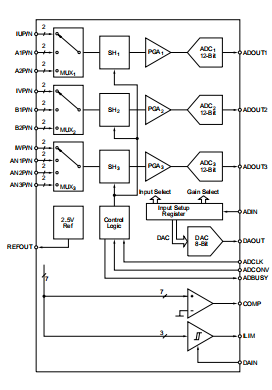

vecana01由三个12位模拟数字转换器组成,前面同时有五个IWP/N

用于10个差分输入的操作采样保持放大器和多路复用器。ADC具有模拟串行输出,用于高速数据传输和数据处理。AN1P/NAdOut3AN2P/NAN3P/N

Vecana01还提供可编程增益放大器,可编程增益为1.0V/V、1.25V/V,2.5V/V和5.0V/V。通道选择和增益选择可通过串行输入控制字选择重新输出。阿德克simula保持了较高的通过率。-阿德科夫在当前转换为忙的计时。COMP该部分还包含一个8位数字到模拟转换器-其数字输入作为输入控制字的一部分提供的转换器

功能图。

vecan01是一个三重12位sar a/d转换器,由双±5v电源供电。该部分包括三个12位逐次逼近adc、10个全差分输入的多路复用器、5个差分输入同步采样保持放大器以及两个异步采样保持放大器。它通过三个同步SPI/SSI串行输出和一个输入端口进行通信。vecana01在外部时钟上运行,外部时钟还决定输出数据速率。

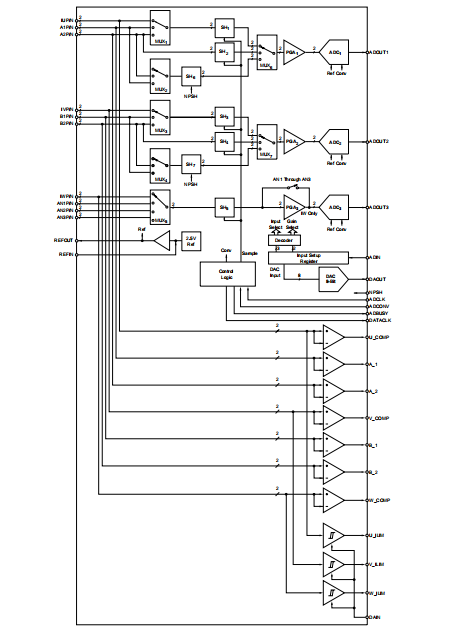

多路复用器

vecana01具有多个输入多路复用器,用于选择所需的模拟输入,并将适当的采样和保持输出连接到pgas和a/d转换器。解码器从输入设置寄存器接收其输入并驱动mux。输入多路复用器可以接收全差分或单端信号。模拟信号通过采样保持差分,PGA一直到A/D转换器的输入端。这提供了最好的噪声抑制。

样品保存

vecana01包含七个采样保持放大器。其中五个(SH1到SH5)同时采样,并在内部同步采样和保持定时。三个采样和保持(sh1、sh3和sh5)连接到输入多路复用器,以便它们可以为所有信道输入提供同步采样。此外,sh2和sh4同时采样其信道的第三个输入(分别为a2和b2)。这在电机控制应用中很有用,其中a1和b1是一个位置传感器的正交输入,a2和b2是第二个位置传感器的正交输入。在该应用中,希望同时采样给定位置传感器的正交输入(即使它们在连续的转换周期中被转换),以便在相同的轴位置捕获它们的值。vecana01还具有有限异步采样的能力。sh6和sh7的采样由控制信号npsh异步控制。这允许两个输入,分别在通道1和通道2上,从另一个采样保持的定时异步采样。这在电机控制应用中非常有用,因为每个通道的两个输入需要异步采样到一个参考点。

时序图。

Vecana01包含三个信号通道,每个通道都有12位A/D转换器输出。A/D转换器同步工作,其串行输出同时发生(表九给出了模拟输入/数字输出关系)。可编程增益放大器位于A/D转换器之前(表九给出了增益选择信息)。对于通道1和通道2,PGA对所有三个模拟输入都有效。对于第三信道,pga只改变iw输入的增益。无论增益选择值如何,输入an1、an2和an3以1.0v/v的固定增益连接到a/d转换器3。

电压基准

Vecana01包含一个内部2.5V电压参考。它可以通过输出缓冲放大器从外部获得。如果需要使用外部参考,可以在refin引脚处连接一个。该引脚对于外部参考电压的输出电阻通常为7kΩ。然后,这会覆盖内部2.5V参考电压,并连接到A/D转换器。它也可用作重新输出端的缓冲输出。

基准电压应通过外部电容器(约2.2μf)缓冲在Refin引脚和RefOut引脚上,尽可能靠近引脚。

数模转换器

8位DAC提供从0V到2.499V的256个输出电压电平(输入/输出关系见表I)。dac由输入设置字的dac输入部分控制。字的dac输入部分在转换周期结束时被选入dac

模数转换器

建筑学

a/d转换器是用开关电容电路实现的12位逐次逼近型。

时钟速率

A/D转换器转换的时钟由ADCLK引脚外部提供。规定精度的典型时钟频率为1.25MHz。这将导致10.4微秒的完整转换周期(S/H采集和A/D转换)。

输入输出

vecana01是为双极性输入电压设计的,使用二进制二补数字输出码。每个A/D转换器都有一个可编程增益功能。这会改变转换器的满标度模拟输入范围和模拟分辨率。

差动和共模输入电压

vecana01设计有从多路复用器输入到a/d转换器输入的全差分信号路径。这样做是为了提供优越的高频噪声抑制。与大多数差分输入半导体器件一样,差分输入电压和共模输入电压的组合存在复合限制。由于大多数模拟输入能够受到可编程增益功能的影响,这一问题变得稍微复杂一些