HIP6503 多重线性功率控制器 ACPI控制接口

日期:2020-3-3HIP6503补充HIP6020或符合ACPI的微处理器和计算机应用。集成电路集成了四个线性电路控制器/调节器、开关、监控和控制在20针SOIC封装中发挥作用。一个线性控制器从ATX生成3.3V双/3.3V SB电压平面提供5VSB输出,为南桥和在休眠期间通过外部晶体管的PCI插槽状态(S3,S4/S5)。第二个晶体管用来接通在S0和S1/S2期间工作的ATX 3.3V输出(活动)工作状态。线性控制器/调节器可选择2.5V或3.3V存储器电源通过外部通过晶体管(3.3V设置开关)输入活动状态。在睡眠状态下,积分通过晶体管提供睡眠电源。另一个控制器通过切换ATX 5V为5V双平面供电输出处于活动状态,ATX5VSB处于睡眠状态。两个内部调节器输出两个专用、无噪音2.5V时钟芯片电源,以及1.8V ICH2恢复井电压。HIP6503的工作模式(活动输出或睡眠输出)可通过两个数字控制管脚进行选择,S3和S5。在5V双通道上启用睡眠状态支持输出通过EN5VDL引脚提供。在活动状态下3.3V双/3.3V SB和2.5V MEM/3.3V MEM线性稳压器使用外部N通道通过mosfet连接直接输出到ATX电源提供的3.3V输入供应,以减少损失。处于睡眠状态,电源接通两个输出都被传输到NPN晶体管。活动状态通过一个外部NPN晶体管。5V双输出通电通过两个外部的MOS晶体管。在睡眠状态下,aPMOS(或PNP)晶体管从ATX传导电流5VSB输出;在激活状态下,电流传输连接到ATX5V输出的NMOS晶体管。这个5V双输出的操作不仅由S3和S5引脚的状态,但EN5VDL引脚的状态为好。3.3V双/3.3V SB和1.8V SB输出激活只要ATX5VSB电压被施加到芯片上。2.5V CLK输出仅在S0和S1/S2期间激活,并且使用3V3管脚作为内部通道的输入源元素。

特征

提供5个ACPI控制电压-5V双USB/键盘/鼠标-3.3V双/3.3V SB PCI/辅助/LAN-2.5V内存RDRAM或3.3V内存SDRAM-2.5V时钟/处理器终端-1.8V SB ICH2恢复良好卓越的输出电压调节-所有输出:温度过高±2.0%(如适用)体积小;外部组件数量非常低RDRAM/SDRAM/DDRAM内存支持所有输出的欠压监测故障报告和温度停机提供无铅加退火(符合RoHS)

应用

符合ACPI的主板电源规范

绝对最大额定值热信息

电源电压,V 5VSB。+7.0伏12伏。接地-0.3V至+14.5VDLA,DRV2。接地-0.3伏至12伏+0.3伏所有其他管脚。接地-0.3V至5VSB+0.3V静电放电分类。3级

推荐操作条件

电源电压,V 5VSB。+5V±5%最低5VSB电源电压保证参数。+4.5伏数字输入,V SX,V EN5VDL。0至+5.5V环境温度范围。0°C至70°C结温范围。0°C至125°C热阻(典型,注1)θJA(摄氏度/瓦)SOIC包(注1)。60个

最高结温(塑料包装)。150摄氏度

最高储存温度范围。-65°C至150°C

最高引线温度(焊接10s)。300摄氏度(SOIC-仅限铅头)

注意:超过“绝对最大额定值”中列出的应力可能会对设备造成永久性损坏。这是一个压力等级和操作在本规范操作章节中所述的上述条件或任何其他条件下的装置并不隐含。

注:

1.θJA是用安装在自由空气中的高效热导率测试板上的元件测量的。

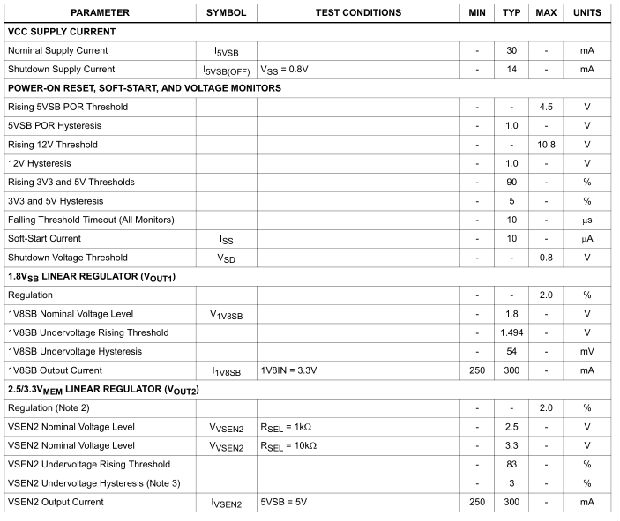

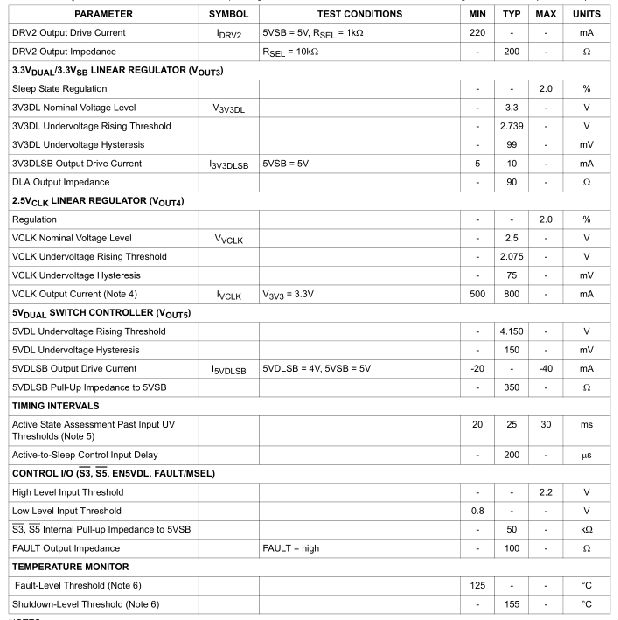

电气规范推荐的操作条件,除非另有说明,参考图1、2和3

电气规范推荐的操作条件,除非另有说明,参考图1、2和3(续)

笔记:

2.仅适用于3.3V设置的睡眠状态

3.5VSB<4.0V的参数不保证。

4.环境温度低于50°C时。

5.由相关性保证。

6.由设计保证。

功能管脚说明

3V3(引脚7)将此引脚连接到ATX 3.3V输出。此pin提供2V5CLK引脚的输出电流,并监测电能质量。5VSB(引脚1)为集成电路提供一个良好的去耦5V偏置电源这个引脚连接到ATX5VSB输出。这个别针提供VSEN1和VSEN2管脚的输出电流,以及Q2的基波电流。这个引脚的电压是出于上电复位(POR)目的进行监控。5V(引脚18)将此引脚连接到ATX 5V输出。此pin提供基极偏置电流为Q1,并监测电能质量。12V(引脚17)将此引脚连接到ATX 12V输出。此pin提供Q3、Q5和Q6的栅极偏置电压,并监测电能质量。接地(引脚11)IC的信号接地。测量所有电压水平关于这个别针。S3和S5(插脚9和10)这些引脚将集成电路的工作状态从激活(S0,S1/S2)至S3和S4/S5睡眠状态。这些是数码的内部50kΩ(典型)电阻上拉至的输入5磅。内部电路排除这些引脚的故障干扰持续时间长达2微秒(通常)。附加电路阻止任何非法的状态转换(如S3到S4/S5或反之亦然)。分别将S3和S5连接到计算机系统的SLP-us3和SLP-us5信号。EN5VDL(引脚8)此pin启用或禁用5V双输出响应S3和S4/S5请求。这个是只能更改其状态的数字输入引脚在激活状态操作期间或芯片关闭期间(SS通过外部开路漏极装置或芯片偏压接地的引脚低于POR水平)。当进入睡眠状态,并跟随5VSB POR释放或退出关机。EN5VDL为内拉式高通40微安电流源。

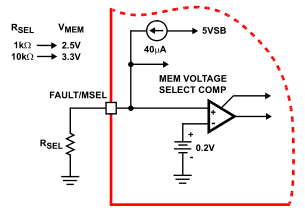

故障/MSEL(引脚12)这是一个多路功能管脚,允许设置存储器输出电压为2.5V或3.3V(对于RDRAM或SDRAM存储系统)。内部40微安电流源在外部电阻上产生一个电压-这个电压将电平与内部200mV参考电压和设置内存调节器输出电压。如果任何受控输出电压过低,在任何受监控的ATX设备上,或在过热事件,此引脚用于报告故障被拉到5VSB的状态。SS(插脚16)将此引脚连接到一个小型陶瓷电容器(不小于5nF;建议0.1微F)。内部软启动(SS)电流源与外部电容器一起产生用于控制输出斜坡上升的电压斜坡电压。用开放式排水装置将此销拉低会关闭关闭所有输出,并强制将故障引脚调低。这个C SS电容器也用于提供受控电压上的活动到睡眠转换期间的转换速率3.3V双/3.3V SB和2.5V MEM/3.3V MEM输出。VSEN2(针脚20)将此引脚连接到内存输出(V OUT2)。在睡眠中状态下,该引脚通过内部通道调节为2.5V能够输出300毫安的晶体管(通常)。这个此引脚的激活状态电压通过连接在DRV2引脚上的外部NPN晶体管。在所有工作状态下,此引脚的电压都会受到监控欠压事件。

DRV2(引脚19)将此引脚连接到适当的NPN晶体管的底座上。这个通过晶体管调节来自ATX的2.5V输出3.3V,在激活状态下运行。3V3DL(引脚5)将此引脚连接到3.3V双/备用输出(V输出3)。在睡眠状态下,该引脚的电压调节为3.3V;在活动状态,ATX 3.3V输出传送到此节点通过一个全通N-MOS晶体管。在所有操作过程中状态下,此引脚被监视是否存在欠压事件。3V3DLSB(引脚4)

将此引脚连接到适当的NPN晶体管的底座上。在休眠状态,该晶体管用于调节3V3DL引脚连接到3.3V。DLA(引脚13)将该引脚连接到合适的N-mosfet的栅极上,该栅极在激活状态下,将ATX 3.3V和5V输出切换到3.3V内存,3.3V双/3.3V SB和5V双输出,分别是。5VDL(针脚15)将此引脚连接到5V双输出(V输出5)。在任何一个工作状态下,该引脚上的电压通过完全在MOS晶体管上。此pin也被监视为低于-电压事件。5VDLSB(引脚14)将该引脚连接到合适的P-MOSFET或双极PNP。在睡眠状态下,晶体管被打开,将ATX 5VSB输出连接到5V双调节器输出。

1V8SB(引脚3)该引脚是内部1.8V调节器(V OUT1)的输出。这个内部调节器在5VSB适用于HIP6503。监视此pin是否低于-电压事件。1V8IN(针脚2)该引脚是1.8V内部调节器的输入电源传递元素。将此插脚连接到3.3V DUAL/3.3V SB输出。VCLK(引脚6)该引脚是内部2.5V时钟芯片调节器的输出(输出4)。此内部调节器仅在激活状态下工作状态(S0,S1/S2)并在任何睡眠状态下关闭,不管芯片的配置如何。这个别针是监控欠压事件。

说明

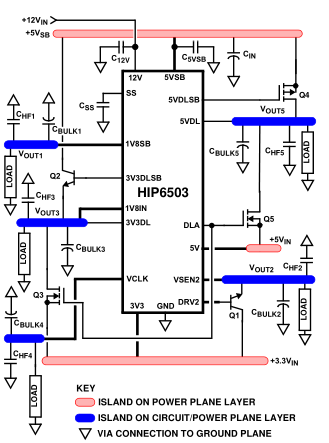

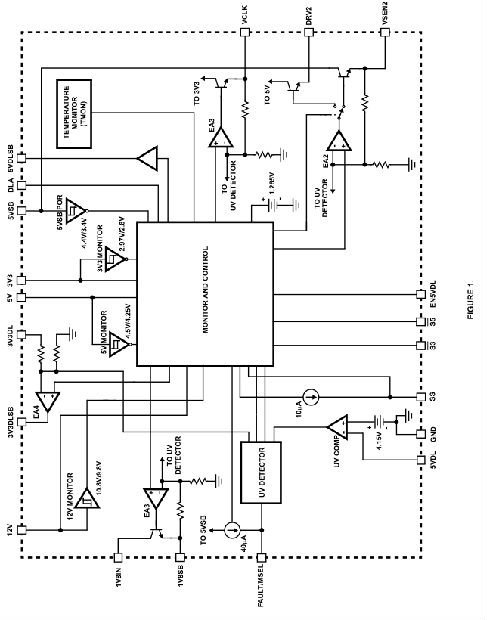

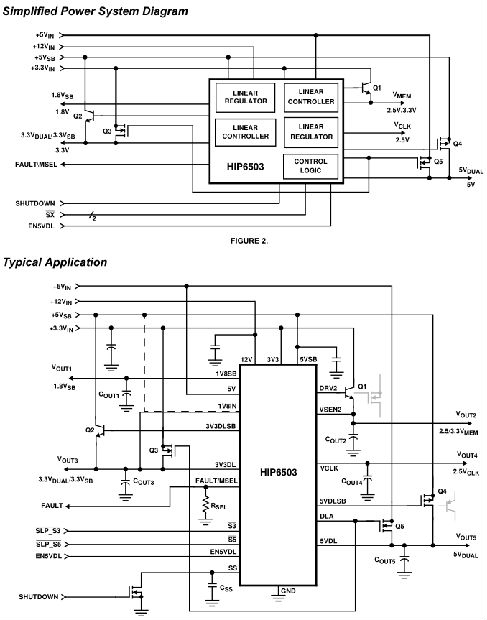

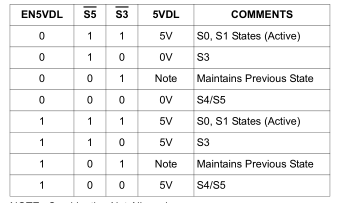

操作 :HIP6503控制5个输出电压(参考图1,2和3)。它是为微机设计的3.3V、5V、5VSB和12V偏置输入的应用ATX电源。集成电路由三个线性电路组成提供计算机系统的控制器/调节器1.8V SB(V输出1)、3.3V SB和PCI插槽的3.3V辅助电源(V输出3)、2.5V RDRAM和3.3V SDRAM内存电源(V输出2),一个专用于2.5V的集成调节器时钟芯片(V OUT4),提供5V双电压(V输出5),以及所有控制和完成ACPI所需的监控功能实施。初始化HIP6503在收到输入时自动初始化权力。上电复位(POR)功能持续监测5VSB输入电源电压,启动3.3V双/3.3V SB和1.8V SB快速软启动操作超过POR阈值后。3毫秒(通常)后两个输出完成它们的加速,EN5VDL和MSEL状态被锁定,芯片继续上升剩余电压,根据需要。操作真值表EN5VDL引脚提供支持或禁用选项5V在S3和S4/S5睡眠状态下的双输出。表1描述与此输出相关的真相组合。

注意:不允许组合。

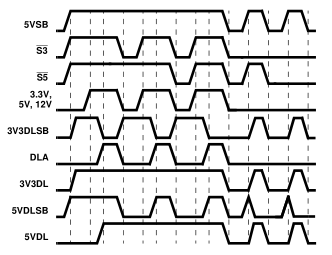

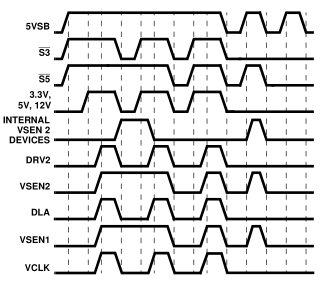

内部电路不允许从S3转换(挂起到RAM)状态到S4/S5(挂起到磁盘/软关闭)状态或相反。唯一的“合法”过渡是活动状态(S0,S1)到睡眠状态(S3,S5)和副反之亦然。功能时序图图4到图6是详细说明功率的时序图响应于启用(EN5VDL)和休眠状态引脚(S3,以及ATX电源的状态。

EN5VDL引脚的状态只能在当偏置电源(5VSB引脚)为低于POR电平,或在芯片关闭期间(SS引脚对接地或在5VSB POR的3ms内);此的状态改变睡眠状态下的pin被忽略。

这些图表中没有显示使用的脱胶功能防止误睡眠状态跳闸。S3和S5引脚通过2μs滤波器(通常为1-4微秒)。此功能在嘈杂的计算机环境中非常有用,如果控制信号必须经过很长的距离。此外,S3引脚具有200微秒的延迟过渡到睡眠状态。一旦S3引脚变低内部计时器被激活。在200微秒间隔结束时,如果S5引脚低,HIP6503切换到S5休眠状态;如果S5引脚高,HIP6503进入S3睡眠状态。

软启动进入睡眠状态(S3、S4/S5)5VSB POR函数启动软启动序列。一个内部10μA电流源为外部电容器充电。误差放大器参考输入被钳制到一个水平与SS(软启动)引脚电压成比例。作为SS引脚电压从大约1.25伏转换到2.5伏,输入钳位允许快速和可控的输出电压上升。

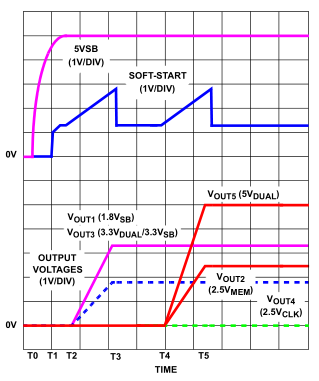

图7显示了典型的应用程序在所有输出电压的睡眠状态下启动启用。在T0 5VSB(偏置)施加到电路时。在时间T1 5VSB超过POR水平。内部禁食充电电路迅速提高SS电容电压大约1V,然后10微安的电流源继续充电。软启动电容电压达到在时间T2时约为1.25V,此时3.3V双/3.3V SB和1.8V SB误差放大器参考输入开始转换,导致输出电压按比例增加。上升趋势一直持续到时间当两个电压达到设定值时。作为柔软的-启动电容器电压达到2.75V左右该输出的欠压监测电路被激活软启动电容器快速放电至3ms(典型)超时后约1.25V在T3和T4之间,MSEL和EN5VDL选择是锁定,软启动电容器启动一秒设计成平稳上升系统所需的电压。在T5时,所有电压为在规定范围内,当SS电压达到2.75V,所有剩余的紫外线监视器都被激活,并且SS电容器迅速放电至1.25V保留到下一个转换。因为2.5V CLK输出只有处于活动状态时才会出现,但是而是等到ATX的主要输出在监管限制。

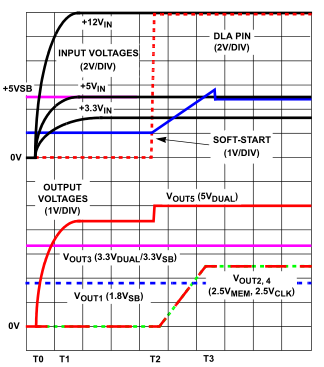

软启动进入激活状态(S0,S1)如果S3和S5在5VSB为应用时,HIP6503将假定激活状态唤醒,并且在一段时间内(通常为25毫秒)保持所需的输出应用程序使用ATX的主要输出(3.3V,5V和12V)超过设置的阈值。这次暂停为了确保ATX的主要输出,功能是必要的是稳定的。超时还可以确保平稳过渡当睡眠状态处于支持。3.3V双/3.3V SB和1.8V SB输出,其操作仅取决于5V SB的存在,将出现就在偏压超过POR水平之后。

从睡眠状态转换为活动状态期间当输出最初为0V时(如S5到S0转换在EN5VDL=0的5V双输出上,或简单通电序列直接进入激活状态),存储器(3.3V和5V双输出通过准软启动通过N通道的体二极管被拉高这些输出和3.3V之间连接的mosfet和5V ATX输出。图8显示了这个启动案例,以5V双输出为例。当主ATX输出为打开,时间T0。由于+5V加速5V双输出电容器通过体二极管充电Q5(见图3)。在时间T1,所有主ATX输出超过HIP6503的欠压阈值,以及启动内部25毫秒(典型)计时器。在T2超时启动软启动,2.5V内存和时钟输出增加,在T3时达到规定限值。与存储器和时钟的开始同时电压上升,在时间T2,DLA引脚被拉高,在此过程中打开Q3和Q5,并将5V双输出调节。在T3之后不久,作为党卫军电压达到2.75V,软启动电容器动作迅速放电至2.45伏左右直到从系统接收到有效的睡眠状态请求。

故障保护所有输出都针对欠压事件进行监控。一个由于任何输出,反过来会导致特定的输出突然下降。如果任何输出电压低于其设定值的80%(典型值),该事件由将故障/MSEL引脚拉至5V。此外,超过集成电路的最大额定电流调节器(芯片上带通调节器的输出)可能导致输出电压下垂;如果过大,这种下垂可以最终使欠压探测器跳闸并发送故障向计算机系统发送信号。控制时输出端发生的故障状态通过一个外通晶体管只会触发故障标志,它不会关闭或锁定电路。当输出端通过内通晶体管控制,将触发故障标志,它将关闭相应的故障仅限调节器。如果整个电路的关闭或闭锁如果出现故障,不管是什么原因,这都是必需的通过外部拉动或锁紧SS销来实现。将SS引脚拉低也会迫使故障引脚变低并重置任何内部锁定的输出。特别考虑了初始启动顺序。如果在5VSB POR事件之后1.8V SB或3.3V双/3.3V SB输出增强在控制电压升高,然后故障输出变高,整个IC锁存关闭。栓锁可通过循环偏置电源(5V SB)重置条件。1.8V SB和在任何其他时间处理3.3V双/3.3V SB输出根据第二段的描述在当前标题下。另一个可以触发故障标志的条件是芯片温度过高。如果HIP6503到达内部温度为140°C(典型),故障标志被设置,但是芯片继续工作直到温度达到155°C(典型),无条件关闭所有输出发生了。在140°C下恢复运行,并且温度循环一直持续到出现故障为止被移除。

在HIP6503应用程序中,任何一个活动ATX输出的丢失(3.3V英寸、5V英寸或12V英寸;通过车载电压检测监视器)在激活状态操作期间导致芯片切换到S5睡眠状态,除了报告输入紫外线故障/MSEL引脚的状态。离开这个强迫-S5状态只能通过返回故障输入来实现电压高于其紫外线阈值,通过复位芯片消除5V SB偏置电压,或将SS引脚置于电位低于0.8V。输出电压输出电压是内部设置的,不需要任何外部组件。V MEM存储器的选择电压是通过一个连接的外部电阻来实现的在故障/MSEL引脚和接地之间。内部40微安(典型的)电流源在这上面产生一个电压降电阻器。每3.3V SB升压或芯片复位(见软启动电路),该电压与内部参考和设置被锁定。基于此相比之下,输出电压设置为2.5V(R选择=1kΩ)或3.3V(R选择=10kΩ)。这很重要没有电容器连接到FAULT/MSEL引脚此引脚上存在电容元件可能导致错误存储器电压选择。详见图9

应用指南

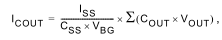

软启动间隔典型ATX电源的5VSB输出能够725毫安。在睡眠状态下通电时,它需要提供足够的电流充电所有的输出电容器和同时为输出提供一定的电流荷载。从5VSB中提取过多电流ATX的输出会导致电压崩溃并导致连续重新启动的模式,对系统的行为或健康。内置的软启动电路可对回转进行严格控制-HIP6503控制的输出电压的加速,从而使ups不受掉电事件的影响。由于输出以线性方式递增,因此专门为输出电容器充电的电流可以是计算公式如下:

I SS-软启动电流(通常为10微安)软启动电容器V BG-带隙电压(通常为1.26V)(C OUT x V OUT)-之间的乘积之和电容和输出电压(总电荷交付所有输出)由于各种系统计时事件,建议软启动间隔不超过30ms。

关闭

如果出现可能危及计算机系统,或在任何其他时间,所有HIP6503通过拉动下面的SS销可以关闭输出规定的停堆水平(通常为0.8V),排水明沟或能够下沉至少2毫安。低拉不锈钢销有效地关闭所有传递元素。释放SS引脚后,HIP6503进行新的软启动循环并恢复正常根据ATX电源和控制引脚进行操作状态。

布局注意事项

使用HIP6503的典型应用程序是直接实施。就像其他线性的监管机构,必须注意少数潜在的敏感的小信号组件,例如到敏感节点或提供关键旁路的节点当前。功率元件(通过晶体管)和控制器集成电路应该放在第一位。控制器应放置在主板上靠近内存的中央位置尽可能加载,但不要离时钟芯片太远或处理器。为1V8SB、DRV2和VSEN2投保连接尺寸适当,可承载250毫安重要的电阻损耗;类似的指南适用于VCLK输出,可输出高达800毫安(典型)。因为VCLK输出的电流是由ATX提供的3.3V,从3V3引脚到3.3V平面的连接其大小应能承载最大时钟输出电流同时表现出可忽略的电压损失。同样地5VSB和5V引脚的当前-为了获得最佳效果,请确保它们与通过适当尺寸的痕迹确定各自的来源。这个通电晶体管应放置在能够散热匹配设备的功耗。在哪里?适用,多通孔连接到大型内平面可显著降低局部器件的温升。去耦电容器和大容量电容器的放置应跟随一个反映他们目的的位置。因此高频去耦电容器应放置在尽可能接近负载,它们是分离的;那些将控制器与控制器引脚分离解耦靠近负载连接器或加载本身(如果嵌入)。即使体积电容(铝电解或钽电容器)放置没有高频电容器的位置那么重要,使这些电容器接近它们所服务的负载是更好。关键的小信号部件包括软启动电容器、C SS以及存储器选择电阻器,R选择。将这些部件靠近相应的销控制IC的,并通过一个通孔将其接地靠近地垫放置。尽量减少泄漏来自这些节点的电流路径,因为内部电流源仅为10微安(10微安至40微安)。