ADC1005是10位μP兼容的A/D转换器

日期:2020-5-20特征

*与所有微处理器的简单接口

*差分模拟电压输入

*按比例或使用5 VDC电压基准或模拟量程调整电压基准运行

*0V至5V模拟输入电压范围,单个5V供给

*片上时钟发生器

*TLL/MOS输入/输出兼容

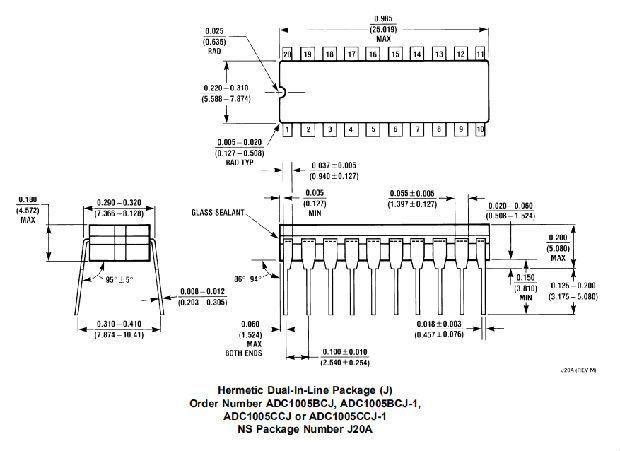

*0.3分“标准宽度20针浸渍

主要规格

*分辨率10位

*线性误差±1/2 LSB和±1 LSB

*转换时间50微秒

一般说明

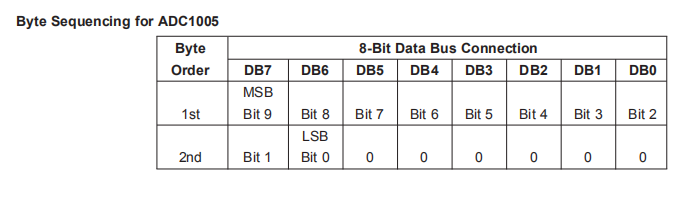

ADC1005是一个CMOS 10位逐次逼近a/D转换器。20针ADC1005以双字节格式输出10位数据,用于8位接口微处理器ADC1005具有差分输入,允许共模信号被抑制,允许模拟输入范围为偏移,也允许信号转换不被接地。此外,可以调整参考电压,允许以10位分辨率测量较小的电压范围。

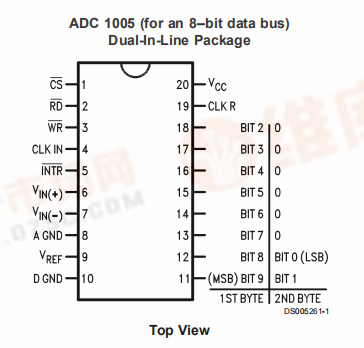

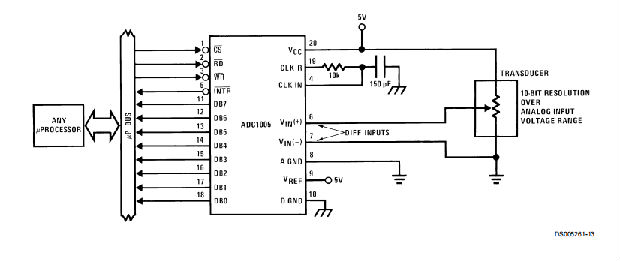

接线图

功能图

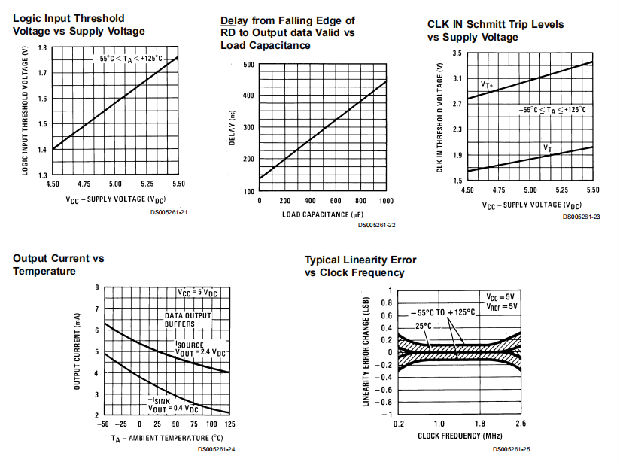

典型性能特征

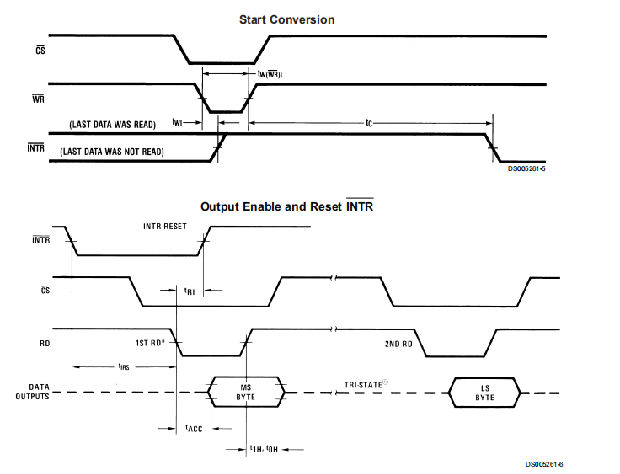

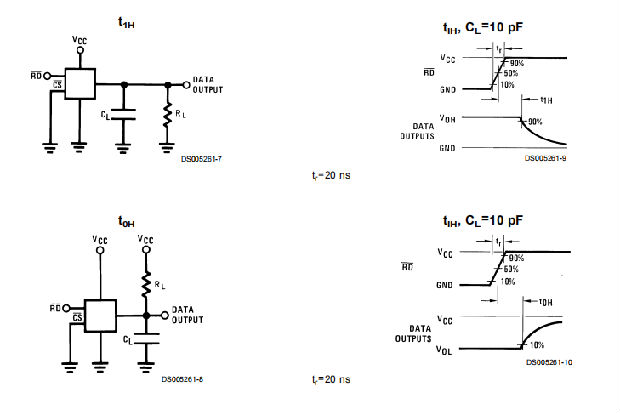

时序图

注:所有正时均从50%电压点开始测量。

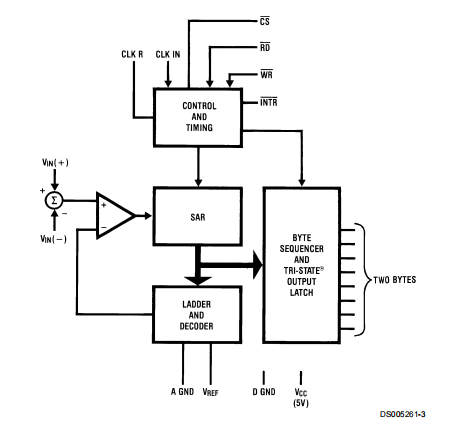

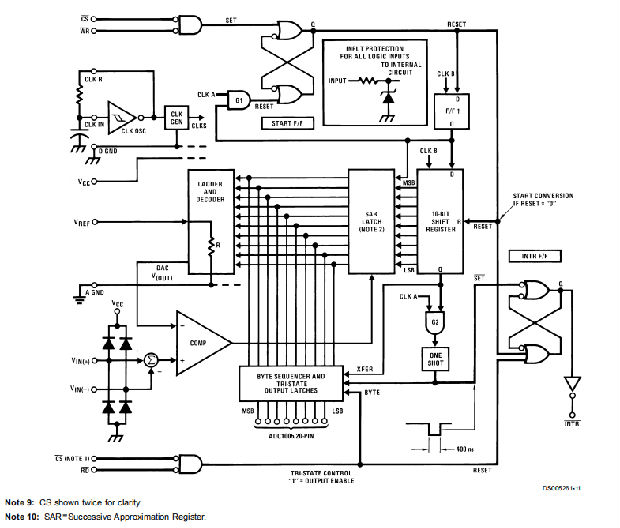

方块图

功能描述

1.0条一般操作

A/D转换器的框图如图1所示。所有的输入和输出都被显示出来,主要的逻辑控制路径被画成更重的线。

1.1款变频器运行

ADC1005采用先进的电位电阻梯形网络。模拟输入以及这个梯形网络的抽头被转换成一个加权电容器阵列。该电容器阵列的输出是采样数据比较器的输入。该比较器允许逐次逼近逻辑将模拟输入电压[VIN+–VIN(-)]与R网络上的抽头相匹配。首先测试最高有效位,在10次比较(80个时钟周期)后,将数字10位二进制代码(全部“1”s=满标度)传输到输出锁存器。

1.2款开始转换

转换通过将CS和WR同时设为低值来初始化。这将设置开始触发器(F/F),结果“1”电平将重置10位移位寄存器,重置中断(INTR)F/F,并向位于10位移位寄存器输入端的D触发器F/F1输入“1”。内部时钟信号然后将该“1”传输到F/F1的Q输出。和门,G1,将这个“1”输出与时钟信号结合起来,为启动F/F提供复位信号。如果设置信号为否更长的存在时间(WR或CS是“1”),开始F/F被重置,然后10位移位寄存器可以有“1”时钟进入,允许转换过程继续。如果设置信号仍然存在,则此复位脉冲将无效,10位移位寄存器将继续保持在复位中模式。因此,该逻辑允许宽CS和WR信号。在这些信号中至少有一个返回高电平并且内部时钟再次为启动F/F提供复位信号之后,转换器将启动。

总而言之,在WR输入的从高到低的转换中,内部SAR锁存器和移位寄存器级被重新-

准备好了。只要CS输入和WR输入保持低,A/D将保持在复位状态。转换将在至少达到最高转换点后开始。

1.3款输出控制

在“1”通过10位移位寄存器(完成SAR搜索)计时后,它会使新的数字字传输到三态输出锁存器。当XFER信号从高到低转换一发即中-输入输入F/F,然后由一个反向缓冲器提供输入输出信号。

请注意,这组对INTR F/F的控制在大约400 ns内保持低电平。如果数据输出连续为en-启用(CS和RD都保持在低位)INTR输出仍将发出转换结束的信号(通过从高到低的转换)。这是因为,即使复位输入始终处于“1”级,设置输入也可以控制INTR F/F的Q输出。因此,在设定信号期间,该INTR输出将保持低。

当要读取数据时,CS和RD的组合低将导致INTR F/F复位,并启用三态输出锁存器。

1.4款自由运行和自动计时模式

在自由运行模式下运行时,应在通电后使用初始化脉冲,以确保电路运行。在这个应用中,CS输入接地,WR输入与INTR输出相连。该WR和INTR节点应在通电循环后立即强制逻辑低,以确保启动。

A/D的时钟可以从CPU时钟派生,也可以添加外部RC以提供自时钟。CLK-IN使用Schmitt触发器,如图2所示。

2.0条参考电压

应用于这些转换器的参考输入的电压定义了模拟输入的电压范围(VIN(MAX)和VIN(MIN)之间的差异),1024个可能的输出代码在此范围内应用。这种装置既可以用于比率测量应用,也可以用于要求绝对精度的系统。参考引脚必须连接到能够驱动参考输入电阻的电压源4.8条kΩ。此引脚是用于逐次近似转换的电阻分压器字符串的顶部。

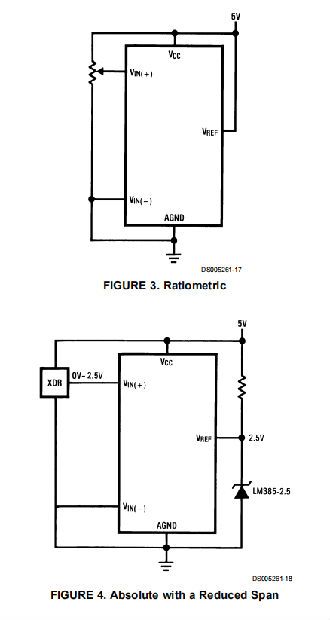

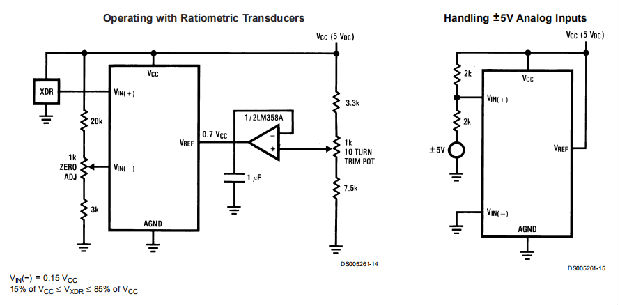

在比率测量系统(图3)中,模拟输入电压与a/D参考电压成正比。该电压通常是系统电源,因此VREF引脚可以连接到VCC。当模拟输入和A/D参考同时移动时,该技术放宽了系统参考的稳定性要求,在给定的输入条件下保持相同的输出代码。

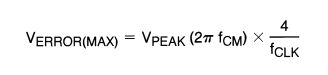

对于绝对精度(图4),当模拟输入在非常特定的电压限制之间变化时,可以使用时间和温度稳定的电压源对参考管脚进行偏置。LM385和LM336参考二极管是与这些转换器一起使用的良好的低电流器件。

参考电压的最大值仅限于VCC电源电压。然而,最小值可以很小,以允许传感器输出的直接转换,提供小于5V的输出范围。必须特别小心在噪声拾取、电路布局和系统误差电压源方面,由于转换器的灵敏度增加(1lsb等于VREF/1024),当以减小的跨度运行时。

3.0条模拟输入

3.1款模拟差分电压输入与共模抑制

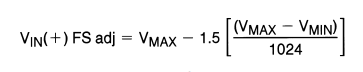

这些转换器的差分输入减少了共模输入噪声的影响,共模输入噪声被定义为所选“+”和“-”输入共同的噪声(60赫兹是最典型的)。采样“+”输入和“-”输入之间的时间间隔是内部时钟周期的一半。这个在此短时间间隔内,共模电压的变化会导致转换错误。对于正弦共模信号,此误差为:

其中fCM是共模信号的频率,VPEAK是其峰值电压值,fCLK是CLK IN pin的时钟频率。

对于60 Hz共模信号,产生/4 LSB误差(1.2款mV)变频器在1.8款兆赫,它的峰值必须是1.46伏一个如此大的共模信号比一般的数据采集系统要大得多。

3.2款输入电流

由于模拟输入的采样性质,在转换过程中,短时间的电流尖峰进入“+”输入并在时钟上升沿退出“-”输入。当内部比较器在时钟周期结束时被触发时,这些电流迅速衰减,不会引起误差。

3.3款输入旁路电容器

输入端的旁路电容器将平均3.2款并使直流电流流过模拟信号源的输出电阻。这种电荷泵的作用对于在满标度下与VIN(+)输入电压的连续转换更为不利。对于连续转换1.8款MHz时钟频率,输入电压为5V,该直流电流最大约为5微安。因此,旁路电容器不应对于高电阻源(>1 kΩ),使用VREFpin的分析输出。如果输入旁路电容器是噪声滤波所必需的,而高源电阻是使电容器尺寸最小化所需要的,则通过该输入电阻的电压降的有害影响是由输入电流的平均值引起的,当给定的源电阻和输入旁路电容都在适当位置时,可以通过满标度调整消除。这是可能的,因为输入电流的平均值是差动输入电压的线性函数。

3.4款输入源电阻

不使用输入旁路电容器的大源电阻值,如果输入电流在比较时间之前稳定,则不会导致错误。如果系统中需要低通滤波器,则使用低值串联电阻(≤1 kΩ)作为无源RC段,或添加运放RC有源低通滤波器。低源电阻应用(≤0.1分kΩ)输入端的4700 pF旁路电容器将防止由于长导线的串联导线感应而引起的拾取。如果使用的话,一个100Ω的串联电阻可以用来将这个电容器(R和C都放在反馈回路之外)与运算放大器的输出隔离。

3.5条噪声

通向模拟输入(插脚6和7)的导线应尽可能短,以尽量减少输入噪声耦合。噪声和不希望的数字时钟耦合到这些输入都会导致系统错误。通常,这些输入的源电阻应保持在1 kΩ以下。源电阻值越大,系统噪声越大皮卡。输入旁路电容器,从模拟输入到接地,可以减少系统噪声拾取,但可以造成模拟规模误差。见章节3.2款, 3.3款,和3.4款如果要使用输入过滤。

4.0条偏移和参考调整

4.1款零偏移

A/D转换器的零误差与传递函数第一提升管的位置有关,可以通过将V(-)输入接地并将小幅度正电压施加到V(+)输入来测量。零误差是仅使输出数字代码从00 0000转换到00 0000 0001所需的实际直流输入电压与理想/2 LSB值(/2 LSB=2.45分VREF的mV=5.0条直流电)。

A/D的零点通常不需要调整。然而,对于车辆识别号(MIN)未接地的情况,以及在减小量程应用中(VREF<5V),可能需要进行偏移调整。通过在该电压下偏置A/D的车辆识别号(-)输入,转换器可以输出任意输入的全零数字代码。这利用了A/D的差分输入操作。

4.2款满标度

满标度调整可以通过施加从所需模拟满标度电压范围向下1/2lsb的差分输入电压,然后调整刚刚从11 1111 1110变为11 1111 1111的数字输出代码的VREF输入的大小来进行。

4.3条任意模拟输入电压范围的调整

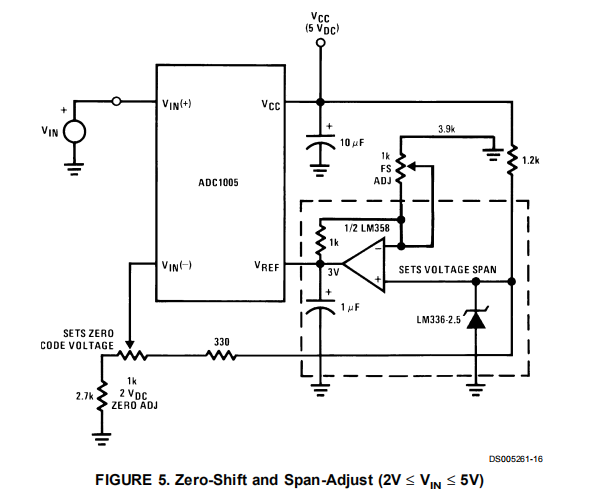

如果A/D的模拟零电压从地面移开(例如,为了适应不接地的模拟输入信号),则应首先正确调整新的零参考。将等于所需零参考电压加/2 LSB(其中LSB是为所需模拟量距计算的,1 LSB=模拟量距/1024)的车辆识别号(+)电压施加到所选“+”输入端,然后应调整相应“-”输入端的零参考电压,以获得000HEX 001HEX代码转换。

应[在施加适当的车辆识别号(-)电压]的情况下,通过强制向以下给出的车辆识别号(-)输入施加电压来进行满标度调整:

其中VMAX=模拟输入范围的高端,VMIN=模拟范围的低端(偏移零点)。(均为地面参考)。

然后调整VREF(或VCC)电压,以提供从3FFHEX到3FEHEX的代码更改。这就完成了调整过程。

有关示例,请参见下面的零点偏移和量程调整电路。

5.0条电源

VCC电源线上的噪声尖峰可能会导致转换误差,因为比较器将对此噪声作出响应。应在靠近转换器VCC引脚的地方使用低电感钽滤波电容器,建议使用1μF或更大的值。如果系统中有未调节的电压-tem,一个单独的LM340LAZ-5.0条,TO-92,5V电压调节器用于转换器(和其他模拟电路)将大大降低VCC电源上的数字噪声。

独立于逻辑的单点模拟接地应使用接地点。电源旁路电容器和自动时钟电容器(如果使用)都应返回数字接地。任何VREF旁路电容器、模拟输入滤波器电容器或输入信号屏蔽应返回到模拟接地点。

典型应用

三态测试电路及波形

物理尺寸英寸(毫米),除非另有说明。