DRV8301-Q1是双电流分流放大器汽车三相前置驱动器以及降压调节器

日期:2020-8-7特点

•适合汽车应用

•AEC-Q100测试结果如下:

–设备温度等级1:–40°C至125°C环境工作温度范围

–设备HBM ESD等级H2

–设备CDM ESD分类等级C4A

•工作电源电压6V–60V

•2.3A水槽和1.7A源极驱动电流能力

•具有可调增益和偏移的集成双并联电流放大器

•集成降压转换器,可支持高达1.5A的外部负载

•3或6个PWM输入的独立控制

•具有100%占空比支持的引导门驱动器

•可编程死区时间,以保护外部FET不被射穿

•用于减少电磁干扰的转换速率控制

•外部MOSFET的可编程过电流保护

•支持3.3V和5V数字接口

•SPI接口

•热增强型56针TSSOP衬垫式DCA封装

应用

•汽车三相无刷直流电动机和永磁同步电动机

•水、油、燃油泵

说明

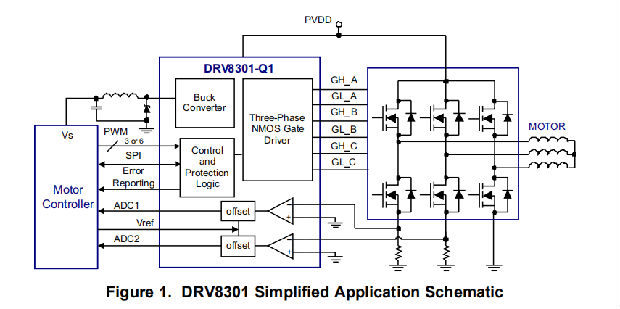

DRV8301-Q1是一种用于三相电机驱动应用的汽车门驱动器IC。它提供了三个半桥驱动器,每个驱动器都能驱动两个N型mosfet,一个用于高侧,一个用于低侧。它支持高达2.3A sink和1.7A源峰值电流能力,只需要一个从6V到60V的宽范围电源。DRV8301-Q1使用带涓流充电电路的引导栅极驱动器,以支持100%的占空比。当高边场效应晶体管或低边场效应晶体管切换时,栅极驱动器使用自动握手来防止电流击穿。在过电流情况下,感测FET的Vds以保护外部功率级。

DRV8301-Q1包括两个电流分流放大器,用于精确的电流测量。电流放大器支持双向电流感应,并提供高达3V的可调输出偏移。

DRV8301-Q1也有一个集成开关模式降压转换器,输出和开关频率可调,以支持MCU或其他系统电源需求。巴克能够驱动高达1.5A负载。

SPI接口提供详细的故障报告和灵活的参数设置,如电流分流放大器的增益选项、门驱动器的转换速率控制等。

这些设备具有有限的内置ESD保护。在储存或搬运过程中,应将引线短接在一起,或将设备放置在导电泡沫中,以防止对MOS门造成静电损伤。

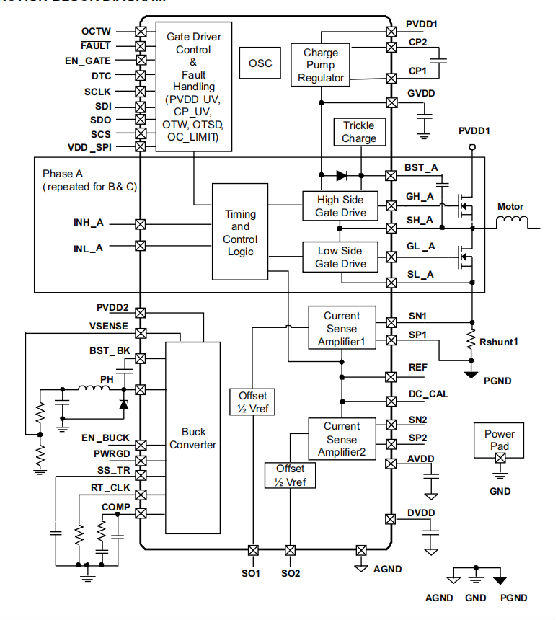

功能框图

功能描述

三相门驱动器

DRV8301-Q1提供了三个半桥驱动器,每个驱动器都能够驱动两个N型MOSFET,一个用于高压侧,一个用于低压侧。

门驱动器具有以下特点:

•开关转换期间,高压侧和低压侧FET之间的内部握手,以防止电流击穿。

•通过SPI接口可编程转换速率或电流驱动能力。

•支持高达200kHz的开关频率,Qg(TOT)=25nC或总30mA栅极驱动平均电流

•提供外部FET的逐周期电流限制和闩锁过电流(OC)关闭。电流通过FET漏源电压感应,过电流水平可通过SPI接口编程

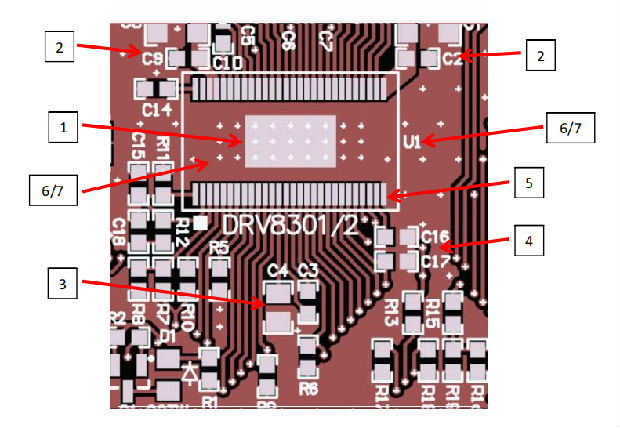

•Vds传感范围可从0.060V编程至2.4V,并通过SPI具有5位可编程分辨率。

•高压侧栅极驱动将承受半桥负输出,最高-10V,持续10ns

•在EN_栅极引脚低和故障情况下,栅极驱动器将保持外部FET处于高阻抗模式。

•通过DTC引脚可编程死区时间。死区时间控制范围:50ns到500ns。短DTC针脚对地将提供最短的死区时间(50ns)。只要外部死区时间长于死区时间设置,外部死区时间将覆盖内部死区时间(为了防止击穿电流,不能缩短最小握手时间)。

•引导带用于三相预栅驱动器的高侧场效应晶体管。涓流充电电路用于补充自举阀盖的电流泄漏,并支持100%的占空比运行。

电流分流放大器

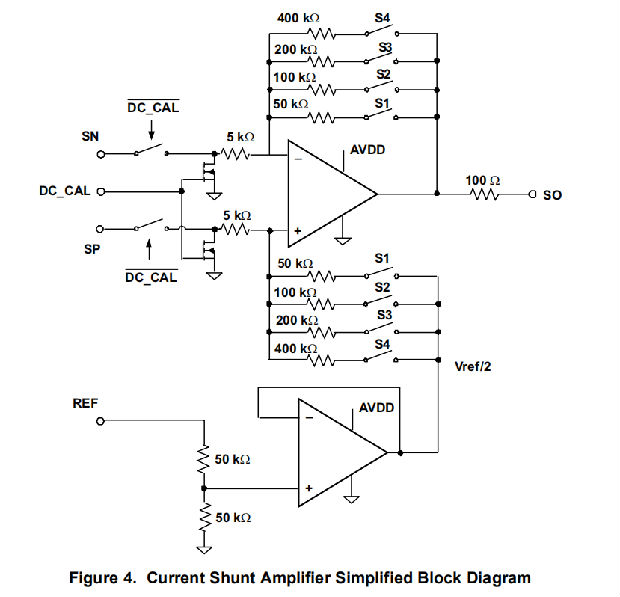

DRV8301-Q1包括两个高性能电流分流放大器,用于精确的电流测量。

电流放大器提供高达3V的输出偏移,以支持双向电流感应。

电流分流放大器具有以下特点:

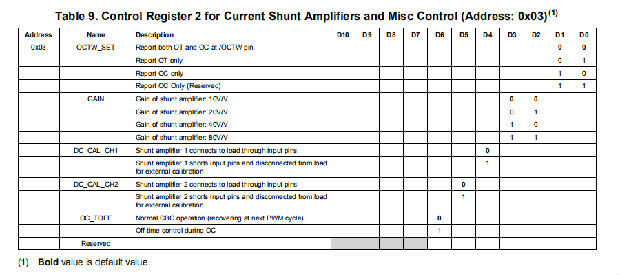

•可编程增益:通过SPI命令设置4个增益

•通过参考引脚的可编程输出偏移(Vref的一半)

•通过SPI命令或直流校准引脚进行直流校准,使直流偏移和温度漂移最小化。当直流校准启用时,装置将短路电流分流放大器的输入并断开负载。直流校准可以在任何时候进行,即使当FET开关,因为负载断开。为了获得最佳结果,在无负载的情况下,在关闭期间执行直流校准,以减少对放大器的潜在噪声影响。

电流分流放大器的输出可计算为:

其中,Vref是参考电压,G是放大器的增益;SNx和SPx是通道x的输入。SPx应连接到电阻接地,以获得最佳共模抑制。

图4显示了电流放大器的简化框图。

BUCK变换器

DR8301中的buck转换器与TPS54160 buck转换器相同。尽管集成在同一个器件中,buck变换器的设计完全独立于其余的栅极驱动电路。由于buck将支持外部MCU或其他外部电源需求,buck操作的独立性对于一个可靠的系统来说是非常关键的;这将使buck从门驱动器操作中受到的影响最小。例如:当门驱动器因任何故障而关闭时,buck仍将工作,除非故障是buck本身造成的。buck保持在3.5V的低PVDD下工作,这将确保当栅极驱动器由于低PVDD而无法工作时,系统能够平稳地上电和断电。

buck有一个集成的高边n沟道MOSFET。为了提高线路和负载瞬变期间的性能,该装置实现了恒定频率、电流模式控制,减少了输出电容,简化了外部频率补偿设计。

在选择输出滤波器组件时,300kHz到2200kHz的宽开关频率允许效率和尺寸优化。开关频率通过RT峎CLK引脚上的接地电阻进行调整。该设备在RT_ck引脚上有一个内部锁相环(PLL),用于将电源开关接通与外部系统时钟的下降沿同步。

buck转换器的默认启动电压约为2.5V。EN_buck引脚有一个内部上拉电流源,可用于通过两个外部电阻器调整输入电压欠压锁定(UVLO)阈值。此外,上拉电流提供了一个默认条件。当EN_BUCK引脚浮动时,设备将运行。在不切换和空载时,工作电流为116μA。当设备被禁用时,电源电流为1.3μA。

集成的200mΩ高侧MOSFET允许高效率的电源设计,能够向负载提供1.5安培的连续电流。集成高压侧MOSFET的偏置电压由启动端到PH引脚上的电容器提供。启动电容电压由一个UVLO电路监控,当启动电压低于预设阈值时,将关闭高压侧MOSFET。由于启动UVLO,buck可以在高占空比下工作。输出电压可以降低到0.8V参考电压。

BUCK有一个功率良好的比较器(PWRGD),当调节输出电压小于标称输出电压的92%或大于109%时,该比较器会进行判断。PWRGD引脚是一个开路漏极输出,当VSENSE引脚电压在标称输出电压的94%和107%之间时,该引脚会断开,允许引脚在使用上拉电阻器时转换为高电平。

该BUCK通过利用OV功率良好比较器来最小化过电压(OV)瞬态。当OV比较器被激活时,高侧MOSFET被关闭并屏蔽,直到输出电压低于107%。

SS_-TR(慢启动/跟踪)引脚用于最小化涌入电流或在通电期间提供电源顺序。一个小值电容器应耦合到引脚上,以调整慢启动时间。电阻分压器可与引脚耦合,以满足关键电源排序要求。在输出通电之前,SS_TR引脚被放电。这种放电确保了超温故障后可重复重启,

此外,在过载情况下,BUCK通过过载恢复电路对慢启动电容器进行放电。一旦故障条件消除,过载恢复电路将缓慢启动从故障电压到标称调节电压的输出。频率折叠电路在启动和过电流故障条件下降低开关频率,以帮助控制电感器电流。

保护特性

功率级保护

DRV8301-Q1为MOSFET功率级提供过流和欠压保护。在故障关闭条件下,所有门驱动器输出将保持低,以确保外部FET处于高阻抗状态。

过电流保护(OCP)和报告

为了保护功率级不受大电流的损坏,在DRV8301-Q1中安装了VDS传感电路。基于功率mosfet的RDS(on)和最大允许id,可以计算出一个电压阈值,当超过该阈值时,触发OC保护特性。该电压阈值水平可通过SPI命令进行编程。

SPI中共有4个OC_模式设置。

1.模式限流

当电流限制模式被启用时,设备在OC事件期间操作电流限制而不是OC关闭。过电流事件通过OCTW引脚报告。在同一个PWM周期内或在最大64μs的时间段(内部计时器)内,OCTW报告应保持低水平,以便外部控制器有足够的时间对警告信号进行采样。如果在报告过程中,其他FET获得OC,则OCTW报告将保持低并重新计数另一个64μs,除非两个FET上的PWM周期结束。

在电流限制模式下有两个电流控制设置(在SPI中按一位选择,默认为CBC模式)。

–设置1(CBC模式):在OC事件期间,检测到OC的FET将关闭,直到下一个PWM周期。

–设置2(关闭时间控制模式):

–在OC事件期间,如果PWM信号仍然保持高电平,则检测到OC的FET将关闭64us作为关闭时间,然后恢复正常(因此相同的FET将再次打开)。由于所有三相或6个FET共用一个定时器,如果不止一个FET发生OC,那么在发生OC事件的所有FET通过64μs之前,FET不会恢复正常。

–如果在定时器运行期间切换了该场效应晶体管的脉宽调制信号,则该开关场效应晶体管的设备将恢复正常运行。所以在这种情况下,实时关闭时间可能小于64uS。

–如果在定时器运行期间,两个FET获得OC,而一个FET的PWM信号被切换,则该FET将恢复正常,而另一个FET将关闭直到计时器结束(除非其PWM也被切换)

2.OC闩锁关闭模式

当发生OC时,如果同一相的任何一个FET中有OC,则该器件将同时关闭该相的高侧和低压侧FET。

3.仅报告模式

在此模式下不会执行任何保护操作。OC检测将通过OCTW引脚和SPI状态寄存器报告。外部MCU应根据其自身的控制算法采取行动。将在OCTW管脚上实现64μS的脉冲拉伸,以便控制器有足够的时间来检测OC信号。

4.OC禁用模式

设备将忽略所有OC检测,也不会报告它们。

欠压保护(UVP)

为了在启动、关闭和其他可能的电压条件下保护功率输出级DRV8301-Q1通过在PVDD低于6V(PVDD_-UV)或GVDD低于7.5V(GVDD_-UV)时驱动其低输出,提供功率级欠压保护。当UVP被触发时,DRV8301-Q1输出被驱动低,外部mosfet将进入高阻抗状态。

过电压保护(GVDD_-OV)

如果GVDD电压超过16V,装置将关闭栅极驱动器和充电泵,以防止与GVDD或充电泵相关的潜在问题(例如,外部GVDD盖或充电泵短路)。该故障为锁定故障,只能通过EN_门引脚上的转换复位。

过热保护

实现了两级超温检测电路:

•1级:超温警告(OTW)

OTW通过OCTW引脚(过流温度警告)报告,用于默认设置。OCTW引脚只能通过SPI命令设置为报告OTW或OCW。参见SPI寄存器部分。

•2级:门驱动器和电荷泵(OTSD_gate)的超温(OT)锁定关闭

故障将报告给故障引脚。这是一个闭锁关闭,因此即使OT状态不再存在,门驱动器也不会自动恢复。在温度低于预设值tOTSD\U CLR后,需要通过引脚或SPI(复位门)复位门驱动器,使其恢复正常运行。

SPI操作仍然可用,只要PVDD仍在定义的操作范围内,OTSD操作期间寄存器设置将保留在设备中。

故障及保护处理

故障引脚指示发生了关机错误事件,例如过电流、过温、过压或欠压。请注意,故障是开路漏极信号。在启动期间,当门驱动器准备好接收PWM信号时,故障将变高(内部EN_gate变高)。

OCTW引脚指示与关机无关的过电流事件和过热事件。

以下是所有保护功能及其报告结构的摘要:

引脚控制功能

EN_GATE

EN_GATE low用于将栅极驱动器、电荷泵、电流分流放大器和内部调节块置于低功耗模式以节省能源。在此状态期间不支持SPI通信。只要PVDD仍然存在,器件将把MOSFET输出级置于高阻抗模式。

当EN_门引脚到高电平时,它将经历一个通电序列,并启用门驱动器、电流放大器、电荷泵、内部调节器等,并重置与门驱动器块相关的所有锁定故障。它还将重置SPI表中的状态寄存器。除非故障仍然存在,否则当在错误事件后切换EN_GATE时,所有锁定的故障都可以复位。

当EN_门从高到低时,它会立即关闭栅极驱动块,因此栅极输出可以使外部fet处于高阻抗模式。然后它将等待10秒,然后完全关闭其余的街区。快速故障复位模式可以通过短时间(小于10μS)切换EN_GATE引脚来实现。这将防止设备关闭其他功能块,如电荷泵和内部调节器,并带来更快和简单的故障恢复。SPI仍然可以在这种快速的门重设模式下工作。

重置所有故障的另一种方法是使用SPI命令(reset_GATE),它将只重置门驱动器块和所有SPI状态寄存器,而不关闭其他功能块。

一个例外是重置GVDD_-OV故障。快速门快速故障复位或SPI命令复位在GVDD\U OV故障下不起作用。复位GVDD_OV故障需要一个低电平保持时间超过10μS的完整EN_GATE。强烈建议在发生GVDD_OV时检查系统和板。

EN_BUCK

降压使能引脚,内部上拉电流源。拉到1.2V以下禁用。浮动以启用。

故障诊断码

死区时间可通过DTC引脚编程。在故障诊断码(DTC)与接地之间应连接一个电阻,以控制死区时间。死区时间控制范围从50ns到500ns。短DTC针脚对地将提供最短的死区时间(50ns)。电阻范围为0至150kΩ。死区时间在这个电阻范围内线性设定。

电流直通保护将始终在装置中启用,与死区时间设置和输入模式设置无关。

VDD_SPI

VDD_SPI是SDO引脚的电源。它必须连接到MCU用于SPI操作的同一电源(3.3V或5V)。

在通电或断电瞬态过程中,VDD_SPI引脚可能很快为零电压。在此期间,系统中任何其他设备的SDO引脚不应出现任何SDO信号,因为这会导致DRV8301-Q1中的寄生二极管从SDO导至VDD U SPI引脚短路。在系统电源顺序设计中应考虑和防止这一点。

直流电

当直流校准被启用时,装置将短路并联放大器的输入并断开与负载的连接,因此外部微控制器可以进行直流偏移校准。直流偏移校准也可以用SPI命令完成。如果只使用SPI进行直流校准,则直流电插头可以连接到GND。

SPI引脚

SDO引脚必须是3态的,这样一条数据总线就可以连接到多个SPI从设备。SCS引脚处于低激活状态。当SCS较高时,SDO处于高阻抗模式。

启停顺序控制

在通电期间,所有门驱动输出保持在低水平。从高电平到低电平的门极放大器可以从高电平到低电平。如果不存在错误,DRV8301-Q1准备好接受PWM输入。只要PVDD在功能范围内,即使在门禁用模式下,栅极驱动器也可以控制功率场效应晶体管。

从SDO到VDD_SPI之间有一个内部二极管,因此VDD_SPI需要始终以与其他SPI设备相同的功率电平供电(如果有来自其他设备的SDO信号)。在SDO引脚上出现任何信号之前,VDD U SPI电源应首先通电,在SDO引脚完成所有通信后关闭电源。

SPI通信

SPI接口

SPI接口用于设置设备配置、运行参数和读取诊断信息。DRV8301-Q1 SPI接口在从属模式下工作。

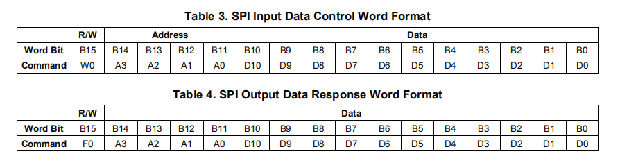

SPI输入数据(SDI)字由16位字组成,11位数据和5位(MSB)命令。SPI输出数据(SDO)字由16位字组成,11位寄存器数据、4位MSB地址数据和1个帧故障位(活动1)。当一个帧无效时,帧故障位将设置为1,其余的SDO位将移出零。

有效帧必须满足以下条件:

1.当/SCS变低时,时钟必须很低。

2.我们应该有16个完整的时钟周期。

3.当/SCS变高时,时钟必须低。

当SCS被断言为高电平时,SCLK和SDI引脚上的任何信号都将被忽略,SDO被强制进入高阻抗状态。当SCS从高电平转换到低电平时,SDO被启用,SPI响应字根据前一时钟周期SPI中的5位命令加载到移位寄存器中。

当SCS转换为低电平时,SCLK引脚必须为低电平。当SCS较低时,在时钟的每个上升沿,响应位在SDO管脚上串行移出,MSB首先移出。

当SCS较低时,在时钟的每个下降沿,新的控制位在SDI管脚上采样。SPI命令位被解码以确定寄存器地址和访问类型(读或写)。MSB将首先在中移位。如果发送到SDI的字小于16位或大于16位,则视为帧错误。如果是写命令,数据将被忽略。SDO(MSB)中的故障位将在下一个16位字周期中报告1。

在第16个时钟周期之后或当SCS从低转换到高时,在写访问类型的情况下,SPI接收移位寄存器数据被传输到地址与解码的SPI命令地址值匹配的锁存器中。只要SCS保持低激活状态,位之间可以经过任何时间。这允许使用两个8位字。

对于SPI中的一个读取命令(第N个周期),SP0将在下一个周期(N+1)中发送寄存器中的数据,并在读取命令中添加地址。

对于SPI中的写入命令,SPO将在下一个16位字周期(N+1)中发送状态寄存器0x00h中的数据。在大多数情况下,当有一个写命令时,这个特性将使SPI通信效率最大化,但是仍然可以在不发送额外的读命令的情况下返回故障状态值。

SPI格式

SPI输入数据控制字长16位,包括:

•1读或写位W[15]

•4个地址位A[14:11]

•11个数据位D[10:0]

SPI输出数据响应字的长度为16位,其内容取决于上一个周期中给定的SPI命令(SPI控制字)。当一个SPI控制字被移入时,SPI响应字(在相同的转换时间内被移出)是对上一个SPI命令(移入SPI控制字“N”和移出SPI响应字“N-1”)的响应。

因此,每个SPI控制/响应对需要两个完整的16位移位周期才能完成。

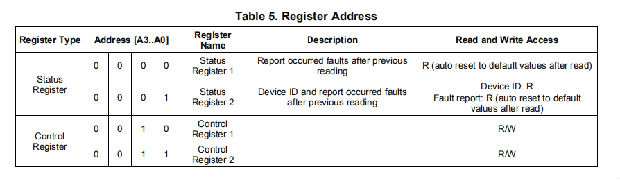

SPI控制和状态寄存器

读/写位

SDI字(W0)的MSB位是读/写位。当W0=0时,输入数据是一个写命令;当W0=1时,输入数据是一个读命令,寄存器值将在同一个字周期内从SDO从D10发送到D0。

地址位

SPI数据位

状态暂存器

•所有状态寄存器位处于锁定模式。读取每个状态寄存器将重置该寄存器中的位。读取故障寄存器两次以获取更新的状态条件。

•当“低”电平保持时间超过10μS时,EN_GATE切换将强制关闭和启动序列,并重置状态寄存器中的所有值,包括GVDD_OV故障。

•低电平保持小于10uS的EN_GATE togging(快速故障复位)或GATE_reset high(在SPI中)将重置状态寄存器中的所有值,gvd_OV fault仍将被锁定为故障。

•当发生任何故障导致停机(GVDD U UV、PVDD U UV、OTSD、OCSD、GVDD_OV)时,故障为高故障,这与故障硬件引脚相反。

控制暂存器

过流调整

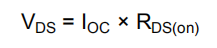

当外部MOSFET被打开时,输出电流流过MOSFET,从而产生电压降VDS。当VDS超过预设值IOC时,将启用过电流保护事件。OC跳闸值可通过SPI命令编程。假设MOSFET的导通电阻为RDS(on),则Vds可计算为:

VDS是通过slux和SH_x引脚为低侧MOSFET测量的。对于高侧MOSFET,VDS是通过PVDD1(内部)和SH_x测量的。因此,限制PVDD1电源上的纹波对于精确的高压侧电流传感非常重要。

同样重要的是要注意,对于OC跳闸点,通道之间的公差可以高达20%。这是为了保护,而不是用来调节电机相位的电流。

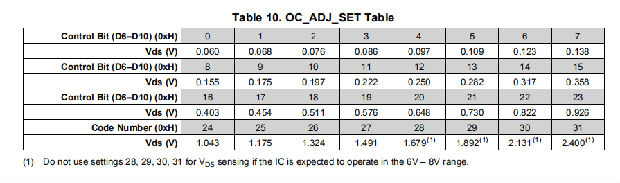

应用示意图示例

例子:

降压:PVDD=3.5V–40V,Iout_max=1.5A,Vo=3.3V,Fs=570 kHz。

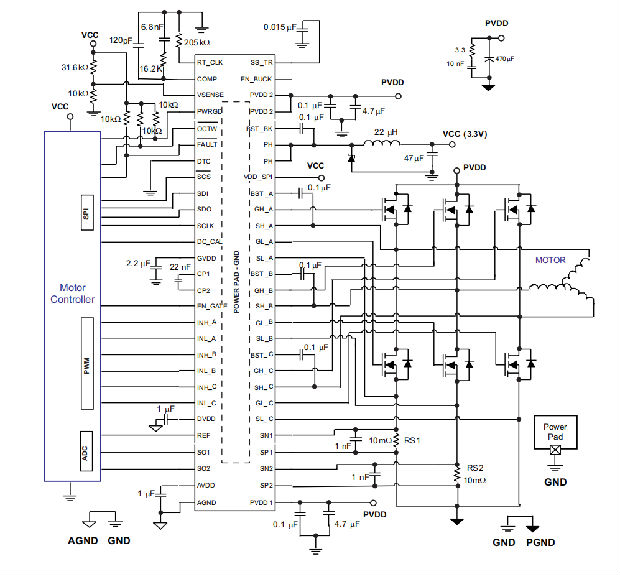

PCB布局建议

以下是为DRV8301-Q1设计PCB时使用的一些布局建议。

1.DRV8301-Q1通过电源板与GND进行电气连接。始终检查以确保PowerPAD已正确焊接(参见PowerPAD应用报告,SLMA002)。

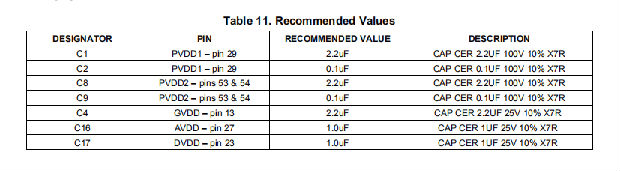

2. C1/C2/C8/C9,PVDD去耦电容器应靠近其相应的管脚,并通过低阻抗路径连接到设备GND(PowerPAD)。

3.C4,gvd电容器应放置在靠近其相应引脚的低阻抗路径的设备GND(PowerPAD)。

4.C16/C17、AVDD和DVDD电容器应放置在靠近其相应引脚的位置,并采用低阻抗路径连接至AGND引脚。最好在同一层建立这种连接。

5.AGND应该通过低阻抗跟踪/铜填充连接到设备GND(PowerPAD)。

6.添加缝合过孔,以减少从上到下的GND路径的阻抗。

7.试着清理DRV8301-Q1周围和下方的空间,以便更好地从电源板散热。