MT41K256M16TW-107 IT:P

日期:2018-3-28

品牌:Micron

型号:MT41K256M16TW-107 IT:P

封装:FGBA96

包装:2000

年份:1806+

数量:80000

产地:马来西亚

瑞利诚科技(深圳)有限公司

联系人:Eason

电话:13312991513

qq:1134043964

邮箱:13312991513@163.com

DDR3L SDRAM

mt41k1g4–128梅格×4×8银行

mt41k512m8–64梅格×8×8银行

mt41k256m16–32梅格×16×8银行

描述

DDR3L SDRAM(1.35V)是一种低电压版本的

DDR3 SDRAM(1.5V)。指DDR3 SDRAM(1.5V)

运行时的数据表规范

1.5v兼容模式。

特征

•V DD = V = 1.35v DDQ(1.283–1.45v)

•向后兼容V DD = V DDQ = 1.5v±0.075v

–支持DDR3L设备落后的COM—

在1.5V的应用程序兼容

•差分双向数据选通

•8N位预取架构

•差分时钟输入(CK,CK #)

•8家内部银行

•名义和动态终结(ODT)

用于数据、选通和掩模信号

•可编程CAS(读)延迟(CL)

•可编程的CAS附加延迟(al)

•编程CAS(写)潜伏期(CWL)

•固定突发长度(BL)的8和突发印章(BC)的4

(通过模式寄存器集[ MRS ])

•可选BC4或BL8上飞(OTF)

•自我刷新模式

MT41K256M16TW-107 IT:P:关键时序参数

速度等级的数据速率(吨/ S)目标T T rp-cl RCD

t RCD (ns) t RP (ns)

CL (ns)

093 1 2 2133 13.09 13.09 13.09 14-14-14

107 1 1866 13.91 13.91 13.91 13-13-13

125 1600 13.75 13.75 13.75 11-11-11

注:1。向后兼容1600,CL = 11(- 125)。

2。向后兼容1866,CL = 13(- 107)。

MT41K256M16TW-107 IT:P:寻址

参数1,x 4,512,MEG,x 8,256,MEG,x 16

配置128 MEG x 4×8银行64梅格x 8×8银行32梅格x 16×8银行

刷新计数8k 8k 8k

行地址64k(一个[ 15:0 ](一)64k [ 15:0 ](一)32k [ 14 ])

银行地址8(BA [2:0])8(八[2:0])8(八[2:0])

列地址2k(一个[ 11 ],9:0)1k(一个[ 9 ](一)1k [ 9:0 ])

页面大小1kb 1kb 2kb

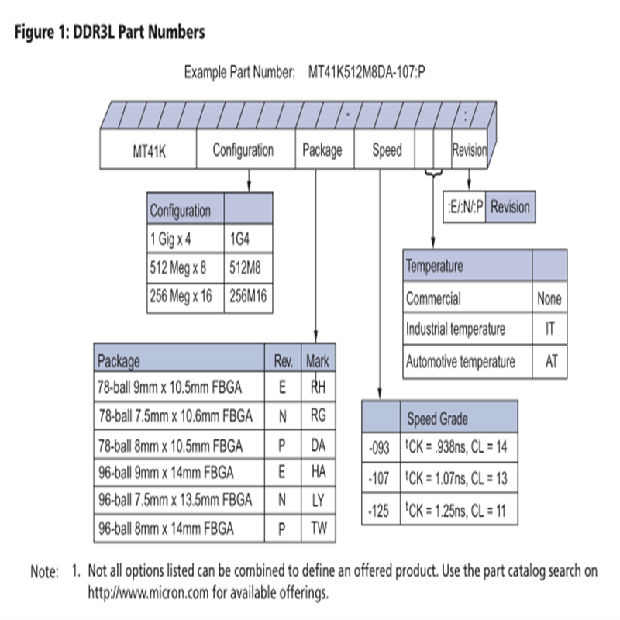

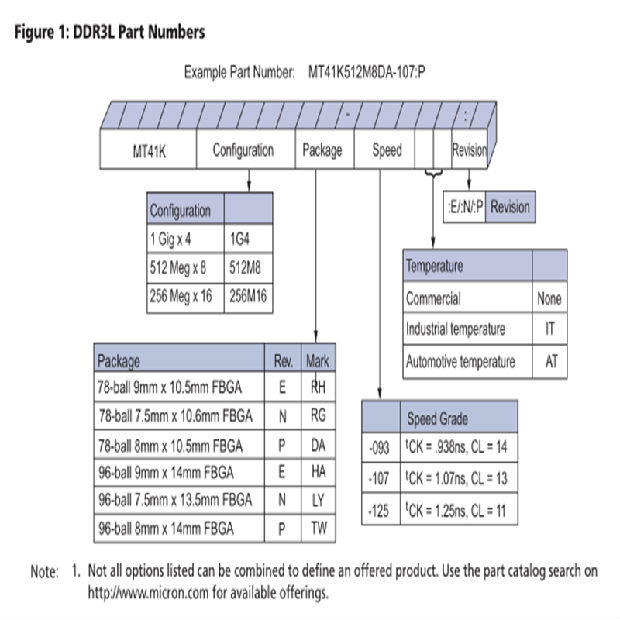

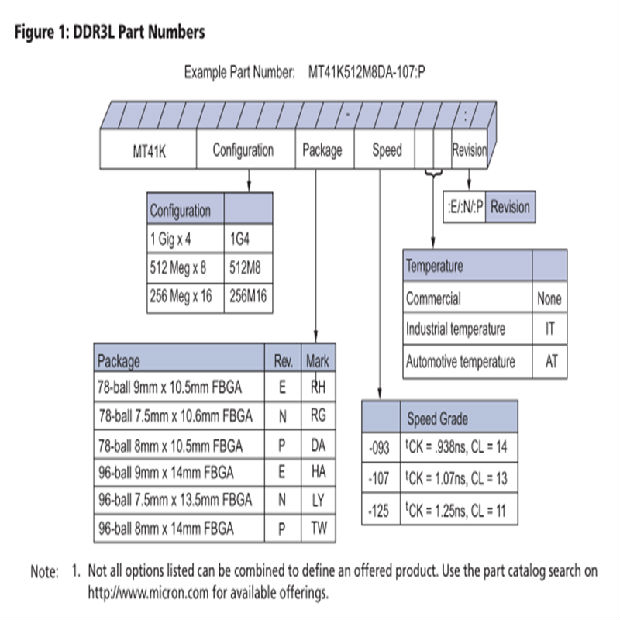

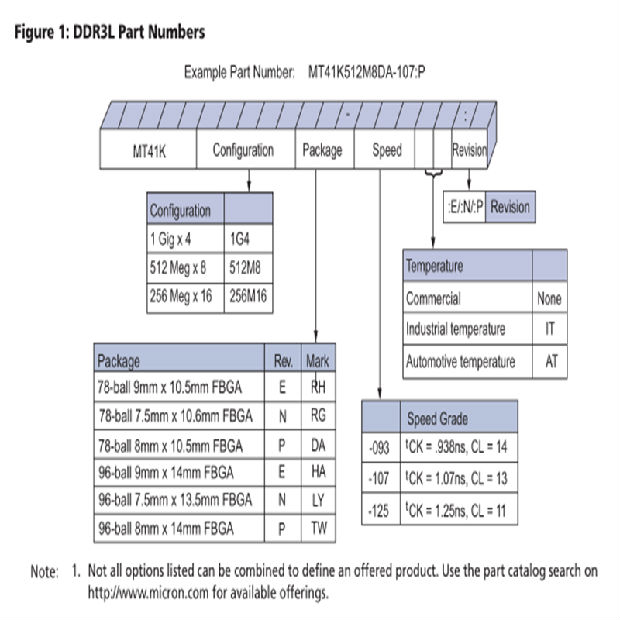

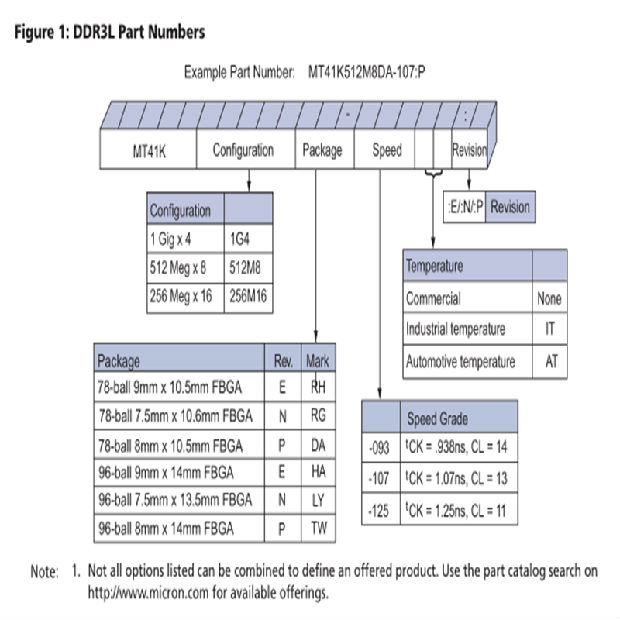

图1:DDR3L的零件号

注:1。并不是所有列出的选项都可以组合来定义一个提供的产品。使用零件目录搜索

FBGA封装标记的解码器

功能描述

DDR3 SDRAM的使用双数据速率架构实现高速运行。

双数据率的架构是一个接口8n预取架构—

在I/O引脚上每个时钟周期传输两个数据字。单个读写

对于DDR3 SDRAM操作有效地组成一个单一的8N位宽,四钟—

周期数据传输在内部的DRAM核心和相应的八n-bit-wide,一—

在I/O引脚上的半时钟周期数据传输。

差分数据选通(DQS,DQS #)外部传输,以及数据,为

在DDR3 SDRAM输入接收机捕获使用数据。DQS是中心对齐数据

为写。读取的数据是由DDR3 SDRAM和边缘对齐的

数据选通。

DDR3 SDRAM工作在差分时钟(CK和CK #)。肌酸激酶杂交

要高,CK #要低,被称为CK阳性边缘。控件—

需求,和地址信号在每个上升沿注册的对照。输入数据为—

执行DQS的第一个上升沿后写的序言,和输出数据参考—

erenced DQS的第一个上升沿后读序言。

读写访问的DDR3 SDRAM的突发性。访问从SE开始—

选择位置和继续编程数量在一个程序的位置

序列。访问首先从激活命令的注册开始,然后

接着是读或写命令。地址位与寄存器一致。

激活命令用于选择要访问的银行和行。广告—

与读写命令相一致的衣服位用来选择。

突发访问的银行和起始列位置。

该设备采用了读、写和BC4 BL8。自动预充电功能可以是

启用提供在突发结束时启动的自定时行预充电。

访问。

与标准的DDR SDRAM,流水线,DDR3 SDRAM多组结构

允许并行操作,从而通过隐藏行预存提供高带宽—

充电激活时间。

提供了一种自刷新模式,以及省电、省电模式。

工业温度

工业温度装置要求外壳温度不要超过。

- 40°C或95°C。JEDEC规格要求刷新率加倍当T C超过。

85°C;这也需要使用高温自刷新选项。此外,

ODT电阻和输入/输出阻抗必须强制降级时,T C<0°C或

> 95°C。

汽车温度

汽车温度(AT)装置要求外壳温度不要超过。

–40°C或105°C.微米规范要求的刷新率超过4倍当T C

95°C;这也需要使用高温自刷新选项。此外,

ODT电阻和输入/输出阻抗必须强制降级时,T C<0°C或

> 95°C。

此数据表中讨论的功能和时序规范是

dll启用操作模式(正常操作)。

•整个数据表,各种数字和文本参照DQS为“DQ,DQ将

解释为任何和所有DQ集体,除非另有具体说明。

•术语“DQS”和“CK”发现整个数据表来解释

DQS,DQS #和CK,CK #分别,除非特别说明,否则。

完整的功能可以在整个文档中描述;任何页面或直径—

克可能被简化,以传达一个主题,可能不包括所有RE—

要求。

•任何具体要求优先于一般声明。

•没有明确说明的任何功能都被认为是未定义的、非法的,而不是支持的—

移植,并可能导致未知操作。

行寻址表示为[ n:0 ]。举例来说,12(13),

x8);2gb:n = 13(x16)和2GB:n = 14(X4、X8);4GB:n = 14(x16);和4GB:n = 15(X4,

x8)。

•动态ODT具有特殊用途的情况下:当DDR3器件设计中使用

单级存储器阵列,ODT球可以连接高而不是路由。参考

对动态ODT特殊用例切片。

•x16设备的DQ总线是由两个字节。如果只有一个字节需要

使用,使用较低的字节进行数据传输,并终止如上所示的上字节:

–连接udqs地通过1k?*电阻。

–连接udqs # V DD通过1k?*电阻。

–连接UDM V DD通过1k?*电阻。

–连接DQ [15:8]分别为V,V DD,或V REF通过1k?电阻器,*或浮子

DQ [15:8]。

*如果ODT使用1k?电阻应改为4X,选片。

热特性

表7:热特性

Notes 1 - 3适用于整个表

参数符号值单位注释

工作温度-商用T C 0至85°C

工作温度-工业吨C - 40至95°C 4

工作温度-汽车T C - 40他的°C 5

注:1。最大操作温度T C是在包的中心测量的,如图所示

下面。

2。必须设计热溶液以确保设备不超过

术中最大t值。

三.如果设备超过最大T C,则不能保证设备功能。

操作。

4。如果t超过85°C,但小于95°C,则必须在2倍时手动刷新DRAM—

新鲜度,这是一个3.9秒的间隔刷新率。使用自刷新温度(SRT)或

必须启用自动自刷新(ASR)。

5。如果T C超过95°C,但小于105°C,DRAM必须手动重新刷新在4X—

新鲜度,这是一个1.95秒的间隔刷新率

电气规范. DD规范和条件

在下面的DD测量表中,以下定义和条件

除非另有说明,否则使用:

•低:V在?V IL(AC)最大值;高电平:V?v IH(ac)min。

•中层:输入V ref = V DD / 2。

•R组有关/ 7(34?)。

•R TT,NOM组有关/ 6(40?)。

•R TT(R)设置有关/ 2(120?)。

•问下是启用MR1。

•ODT是启用MR1(R TT,NOM)和MR2(R TT(WR))。

•tdqs是残疾人在MR1。

•外部DQ / DQS / DM负载电阻为25?V DDQ / 2。

•BL8突发长度是固定的。

•铝等于0(除了我dd7)。

•在设备正确初始化后测试DD规格。

•输入转换率由AC参数测试条件指定。

•可选ASR已禁用。

读突发式采用蚕食的顺序(MR0 [ 3 ] = 0)。

循环模式必须至少在当前测量开始之前执行一次。

:用于DD测量的定时参数-时钟单元

我的DD

187e 25E - 25 - 187 - 15E - 15 - 125 - 107 - 093 125e

7-7-7 5-5-5 6-6-6 8-8-8 9-9-9 10-10-10 10-10-10 11-11-11 13-13-13 14-14-14

T(min)I DD

2.5 1.875 1.5 1.25 1.07 0.938纳秒

CL I DD 5 6 7 8 9 10 10 11 13 14 CK

T细胞(分钟)我的DD

5,6,7,8,9,10,10,11,13,14,CK

RC(min)i DD

20,21,27,28,33,34,38,39,45,50,CK

T ras(min)I

15,15,20,20,24,24,28,28,32,36,CK

T RP(min)

5,6,7,8,9,10,10,11,13,14,CK

T一汽

X4、X8 16 16 20 20 20 20 24 24 26 27对照

20 20 27 27 30 X16 30 32 32 33 38对照

T RRD

我的DD

X4、X8 4 4 4 4 4 4 5 5 5 6对照

4 4 6 6 5 X16 5 6 6 6 7对照

T RFC

1GB的44 44 59 59 74 74 88 88 103 118对照

2GB 64,64,86,86,107,107,128,128,150,172,CK

104 139 139 4GB 104 174 174 208 208 243 279对照

8GB的140 140 187 187 234 234 280 280 328 375对照

电气规范-直流和交流

直流操作条件

表23:DDR3L 1.35v直流电气特性和操作条件

所有电压都参考V。

参数/条件符号

电源电压V DD 1.283 - 1.35 - 1.45 V - 1 - 7

I/O电源电压V DDQ 1.283 1.35 1.45 7 1–V

输入漏电流

任何输入为0VVV DD,V REF引脚0v?V?1.1v

(所有其他引脚不测试= 0v下)

我I - 2 - 2微米

电源泄漏电流

V refdq = V DD / 2或V refca = V DD / 2

(所有其他引脚不测试= 0v下)

我––μVREF 1 1 8, 9

注:1。V DD和V DDQ必须跟踪另一个。V DDQ必须?V DD。V = V SSQ。

2。V DD

直流(0赫兹到250千赫)规格。V DD和V DDQ必须在同一水平的有效交流

定时参数。

三.最大直流值不得大于1.425V。直流值线性平均

V DD / V DDQ(T)在一段很长的时间(例如,1秒)。

4。这些电源电压的条件下,该装置操作这DDR3L规格。

5。如果最大输入电平超出限制,应受DDR3规格。

6。在1.5V的操作下,这是一个符合标准的设备—

根据该装置定义的相同速度定时的阳离子。

7。一旦初始化为DDR3L DDR3运行操作,才能使用

复位时V DD和V DDQ是DDR3操作改变(见VDD电压开关—

8。最低限度要求是用于测试目的。v上的漏电流

引脚应该是最小的。

9。V REF(见表24)。

输入操作条件

表24直流电特性和输入条件

所有电压都参考V。

参数/条件符号

V低;DC /命令/地址总线V IL V SS N / A见表25 V

V高;DC /命令/地址总线V IH见表25 N / A V DD V

命令/地址总线的输入参考电压V refca(DC)0.49×V DD 0.5×V DD 0.51×V DD V 1, 2

I / O参考电压V refdq DQ总线(DC)0.49×V DD 0.5×V DD 0.51×V DD V 2, 3

I / O参考电压DQ总线在自刷新V refdq(SR)V SS 0.5×V DD V DD V 4

命令/地址终止电压

(系统级,而不是直接DRAM输入)

V TT–0.5×V DDQ–V 5

注:1。V refca(DC)预计约为0.5×V DD和跟踪变化的直流

水平。外部产生的噪声峰值(非普通模式)V refca不得超过

±1%×V DD在V refca(DC)值。峰值交流噪声对V refca不前—

2%项±V refca(DC)。

2。DC值被确定为小于20兆赫的频率。DRAM必须符合规范—

如果DRAM引起额外的交流噪声大于20兆赫的频率。

三.V refdq(DC)预计约为0.5×V DD和跟踪变化的直流

水平。外部产生的噪声峰值(非普通模式)V refdq不得超过

±1%×V DD在V refdq(DC)值。峰值交流噪声对V refdq不前—

2%项±V refdq(DC)。

4。V refdq(DC)5 V refdq过渡(SR)和回V refdq(DC)在自刷新,

在自我刷新部分中列出的限制内。

5。v TT不直接应用到设备上。V是信号终端的系统电源—

晶体管。最小值和最大值是依赖于系统的。

25输入输出交换条件-命令和地址

参数/状态符号ddr3l-800 / 1066 / 1600 / 2133单位ddr3l-1866 ddr3l-1333

命令和地址

输入交流电压:1 V逻辑高IH(ac160),最小5 160 160–MV

V IH(ac135),最小5 135 135 135 MV

V IH(ac125),分5––125 MV

输入直流电压:1 V逻辑IH(DC90),最小90 90 90 MV

输入低电压:0 V逻辑IL(DC90),90 min––90–90 MV

输入交流电压过低:逻辑0 V IL(ac125),分5–––125 MV

V IL(ac135),分5–135–135–135 MV

V IL(ac160),分5–160–160–MV

DQ和DM

输入交流电压:1 V逻辑高IH(ac160),最小5 160 160–MV

V IH(ac135),最小5 135 135 135 MV

V IH(ac125),分5––130 MV

512-2efd-4712-9333-e34c20dc88d7.jpg" title="MT41K256M16TW-1071_副本.jpg" />

输入直流电压:1 V逻辑IH(DC90),最小90 90 90 MV

输入低电压:0 V逻辑IL(DC90),90 min––90–90 MV

输入交流电压过低:逻辑0 V IL(ac125),分5–––130 MV

V IL(ac135),分5–135–135–135 MV

V IL(ac160),分5–160–160–MV

注:1。所有电压都参考V参考。V是V REF refca控制、命令和地址。所有

在DRAM球上指定转换速率和设置/保持时间。V是V REF refdq DQ

DM输入。

2。输入设置定时参数(T和T DS)是引用在V IL(AC)/ V IH(AC),而不是V REF(DC)。

三.输入保持定时参数(T IH和T DH)被引用在V IL(dc)/ V IH(dc),而不是V REF(DC)。

4。单端输入转换速率= 1伏/纳秒,最大输入电压摆幅测试下

900mv(峰峰值)。

5。当两个V IH(ac)值(和两个相应的V IL(ac)值)列为一个特定的

速度仓,用户可以选择输入电平的任一值。两者的价值

使用时,还必须使用交流电平的相关设置时间。此外,一

V IH(ac)值可用于地址/命令输入和其他V IH(ac)值。

用于数据输入。

例如,对于ddr3-800,定义了两输入交流水平:V IH(ac160),min

V IH(ac135),min(对应V IL(ac160),min和V IL(ac135),min)。对于ddr3-800,地址/

命令输入必须使用V IH(ac160),min(T是ac160)的210ps或V IH(ac150),min

用T(ac135)的365ps;独立,数据输入必须使用V IH(ac160),min

T DS(ac160)的75ps或V IH(ac150),min(T DS ac150)的125ps。

DDR3L 1.35v差动输入操作条件(CK,CK #和DQS,DQS #)

参数/条件符号最小最大单位注释

差分输入逻辑高-旋转V IH,差分(AC)旋转180 N / mv mv 4

差分输入逻辑低-旋转V IL,差分(AC)旋转N / A - 180毫伏4

差分输入逻辑高V IH,差分(AC)2×(V IH(AC)V REF)V,V,V,5

差分输入逻辑低V IL,diff(AC)V / V SSQ 2×(V IL(AC)V REF)MV 6

差动输入交叉电压

相对于V DD / 2 DQS,DQS #;CK,

CK #

v IX V REF(DC)- 150 V REF(DC)+ 150 MV 5, 7, 9

差动输入交叉电压

相对于V DD / 2,CK、CK #

v九(175)V REF(DC)- 175 V REF(DC)+ 175 MV 5, 7 - 9

因为闪光灯单端高电平

V说

V DDQ / 2 + 160 V DDQ MV 5

CK单端高电平,CK # V DD / 2 + 160 V DD MV 5

对于单端低电平选通

V SEL

V SSQ V DDQ / 2 - 160 mV 6

CK单端低电平,CK # V V DD / 2 - 160 mV 6

注:1。时钟被引用到v DD和V SS。数据选通是参照V DDQ和V SSQ。

2。引用V refca(DC)时钟和V REFDQ(DC)闸门。

三.差分输入转换速率= 2伏/纳秒。

4。定义相对于输入交叉电压的转换速率参考点。

5。最小直流限制是相对于单端信号的,超调指标是应用—

电缆。

6。最大直流极限是相对于单端信号;下冲规格AP—

适用。

7。V IX典型值(AC)预计约0.5×V DD的发射装置,

和V IX(AC)预计将跟踪在V DD的变化。v(ac)表示电压。

差动输入信号必须交叉。

8。V IX扩展范围(±175mv)只允许用于时钟;V IX扩展范围

只有在满足下列条件时才允许:单端输入信号

是单调的,有单端摆V SEL,V说至少V DD / 2±峰峰值为250mV,和

CK的转换率差,CK #大于3 V / NS。

9。V IX必须提供25mv(单端)的电压分离。

DDR3L 1.35v摆率定义为单端输入信号

设置(T是和T DS)标称上升率信号的转换率被定义为转换率是—

最后一次v交叉和v(ac)min的第一次交叉。设置(t和t)

下降信号的标称转换率定义为最后一个交叉点之间的转换速率。

v参考和v(ac)max的第一次交叉。

保持(T - IH和T DH)标称上升率信号的转换率被定义为转换率是—

v(DC)max最后一个交叉点和v的第一个交叉点。保持(t和t)

下降信号的标称转换率定义为最后一个交叉点之间的转换速率。

v(DC)min和V REF的第一个交叉