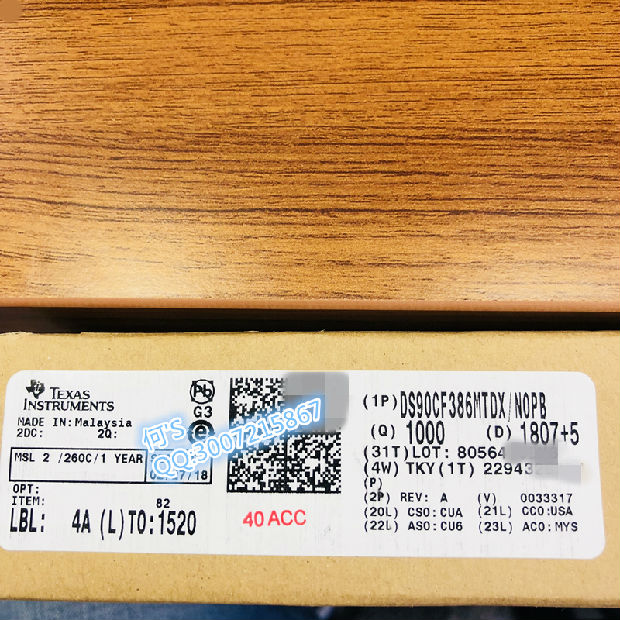

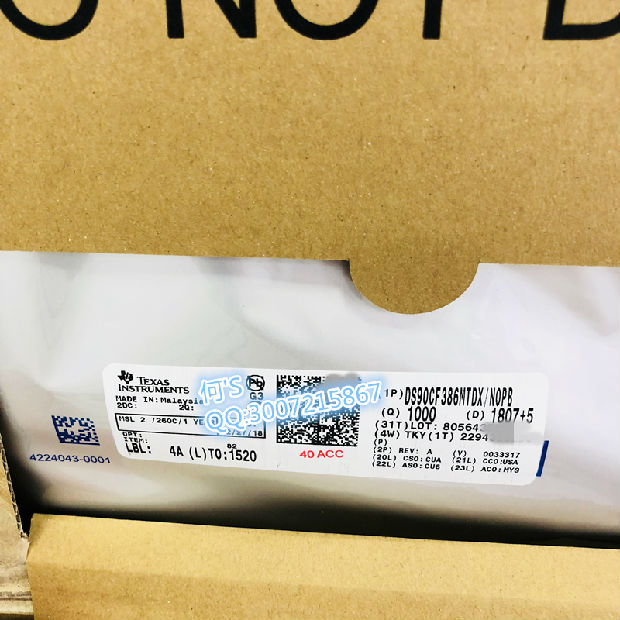

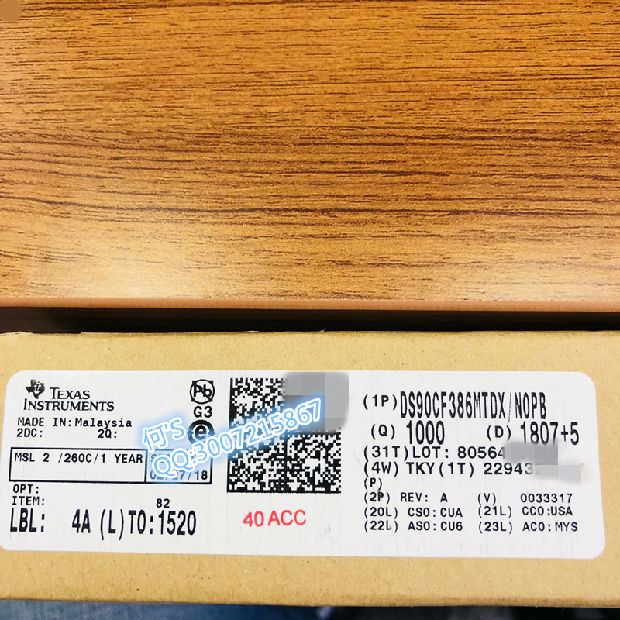

DS90CF386MTDX/NOPB

日期:2018-7-2 DS90CF386MTDX.jpg" />

DS90CF386MTDX.jpg" />

描述

DS90CF386接收器将四个LVDS(低压差分信号)数据流转换回并行的28位LVCMOS数据。同样可用的DS90CF366接收器可将三个LVDS数据流转换回并行的21位LVCMOS数据。两个接收器的输出在下降沿频闪。上升沿或下降沿选通发射器将与下降沿选通接收器互操作,无需任何转换逻辑。

接收器LVDS时钟的工作频率为20 MHz至85 MHz。器件锁相到输入LVDS时钟,在LVDS数据线上对串行比特流进行采样,并将它们转换为并行输出数据。在85 MHz的输入时钟频率下,每个LVDS输入线路的运行速率为595 Mbps,DS90CF386的最大吞吐量为2.38 Gbps,DS90CF366的吞吐量为1.785 Gbps。

DS90CF386MTDX 2.jpg" />

DS90CF386MTDX 2.jpg" />

这些串行链路器件的使用非常适合解决与在宽,高速并行LVCMOS接口上传输数据相关的EMI和电缆尺寸问题。两种器件均采用TSSOP封装。 DS90CF386还采用64引脚,0.8 mm,细间距球栅阵列(NFBGA)封装,与56引脚TSSOP封装相比,PCB占位面积减少了44%。

特性

支持20 MHz至85 MHz移位时钟

Rx功耗<142 mW(典型值)

85-MHz灰度

Rx掉电模式<1.44 mW(最大值)

ESD额定值> 7 kV(HBM),> 700 V(EIAJ)

支持VGA,SVGA,XGA和单像素

SXGA

PLL不需要外部组件

兼容TIA / EIA-644 LVDS标准

薄型56引脚或48引脚TSSOP封装

DS90CF386还提供64引脚,0.8 mm,

精细间距球栅阵列(NFBGA)封装

DS90CF3x6 3.3V LVDS接收器24位或18位平板显示器(FPD)链路,85 MHz

1功能

1•20MHZ至85MHz的移位时钟支持

•Rx功耗<142 mW(典型值)at

85-MHz灰度

•Rx掉电模式<1.44 mW(最大值)

•ESD额定值> 7 kV(HBM),> 700 V(EIAJ)

•支持VGA,SVGA,XGA和单像素

SXGA

•PLL不需要外部组件

•兼容TIA / EIA-644 LVDS标准

•薄型56引脚或48引脚TSSOP封装

•DS90CF386还提供64引脚,0.8毫米,

精细间距球栅阵列(NFBGA)封装

2应用

•视频显示

•打印机和成像

•数字视频传输

•机器视觉

•打开LDI到RGB桥

3说明

设备锁相到

输入LVDS时钟,对串行比特流进行采样

LVDS数据线,并将它们转换为并行

输出数据。在85 MHz的输入时钟频率下,

每个LVDS输入线以比特率运行

595 Mbps,最大吞吐量为

DS90CF386为2.38 Gbps,而为1.785 Gbps

DS90CF366。

DS90CF386MTDX.jpg" />

DS90CF386MTDX.jpg" />

使用这些串行链路设备是理想的选择

解决与EMI相关的EMI和电缆尺寸问题

通过宽,高速并行传输数据

LVCMOS接口。两种设备都提供

TSSOP包。 DS90CF386也提供

64引脚,0.8 mm,细间距球栅阵列(NFBGA)

封装使PCB减少44%

与56引脚TSSOP封装相比,占位面积更