AD9948是10位精密定时CCD信号处理器™ 核心

日期:2020-3-4特征

相关双采样器(CDS);0分贝至18分贝像素增益放大器(PxGA);6分贝至42分贝10位可变增益放大器(VGA);10位25 MSPS A/D转换器;带可变电平控制的黑色电平钳;完整的片上定时驱动器;800 ps分辨率的精密定时核心;片上3V水平和RG驱动器;40铅LFCSP包。

应用

数码相机;高速数字成像应用。

一般说明

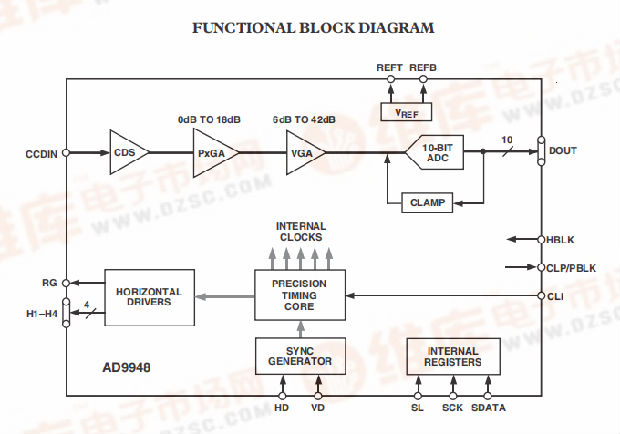

AD9948是一款高度集成的CCD信号处理器,用于数码相机应用。以像素速率指定,最高可达25兆赫,AD9948由一个完整的模拟前端组成与A/D转换,结合可编程定时驱动器。精密定时核心允许高800 ps分辨率的速度时钟。

模拟前端包括黑色电平钳位、CDS、PxGA,VGA和25兆赫10位a/D转换器。定时驱动器为RG和H1-H4提供高速CCD时钟驱动器。使用3线串行接口对操作进行编程。

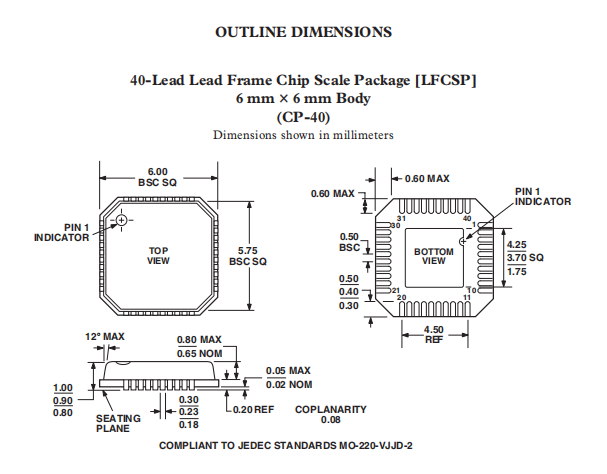

封装在节省空间的40铅LFCSP封装中AD9948的工作温度范围为–20°C至+85°C。

术语

微分非线性(DNL)

理想的ADC显示的代码转换正好是1 LSB间隔。DNL是这个理想值的偏差。因此,每个代码都必须有一个有限的宽度。保证10位分辨率的无丢失代码表示所有1024个代码必须在所有操作条件下分别存在。

峰值非线性

峰值非线性,全信号链规范,是指AD9948的输出与真实直线的峰值偏差。用作零刻度的点在第一个代码转换之前出现0.5 LSB。正满标度定义为超出最后一个代码转换的1级LSB和0.5级LSB。从每个特定输出代码的中间到真正的直线测量偏差。然后将误差表示为2v ADC满标度信号的百分比。输入信号总是被适当地放大以满足ADC的满标度范围。

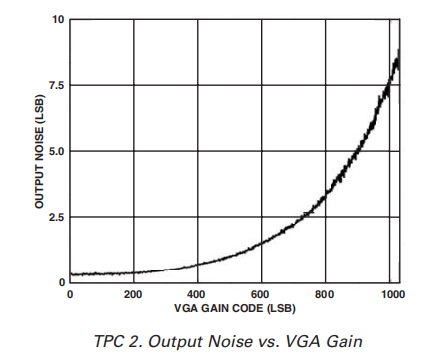

总输出噪声

利用直方图技术测量均方根输出噪声。

ADC输出码的标准偏差以LSB计算,表示指定增益设置下整个信号链的均方根噪声级。利用这种关系,输出噪声可以转换成等效电压:

其中n是ADC的位分辨率。对于AD9948,1 LSB约为1.95 mV。

电源抑制(PSR)

PSR通过施加在电源引脚上的阶跃变化来测量。PSR规范是根据给定的供电电压阶跃变化的数据输出的变化来计算的。

典型性能特征——AD9948

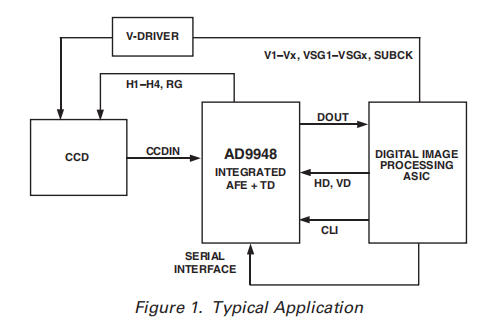

系统概述

图1显示了公元9948年。CCD输出由AD9948的AFE电路处理,该电路由一个CD、一个PxGA、一个VGA、一个黑色电平钳和一个a/D转换器组成。数字化的像素信息被发送到数字图像处理器芯片,在那里进行所有的后处理和压缩。为了操作CCD,CCD定时参数通过3线串行接口从图像处理器编程到AD9948中。由图像处理器提供的系统主时钟CLI,AD9948产生高速CCD时钟和所有内部AFE时钟。所有AD9948时钟都与VD和HD同步。所有AD9948的水平脉冲(CLPOB、PBLK和HBLK)都在内部编程和生成。

H1-H4和RG的H驱动程序包含在AD9948中,允许这些时钟直接连接到CCD。AD9948支持3 V的H驱动电压。

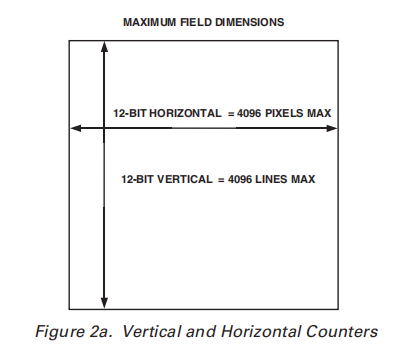

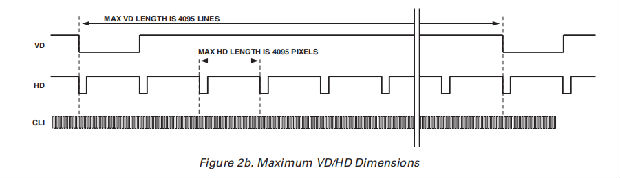

图2a显示了AD9948的水平和垂直计数器尺寸。所有内部水平时钟是用这些尺寸来指定线和像素位置编程的。

串行接口定时

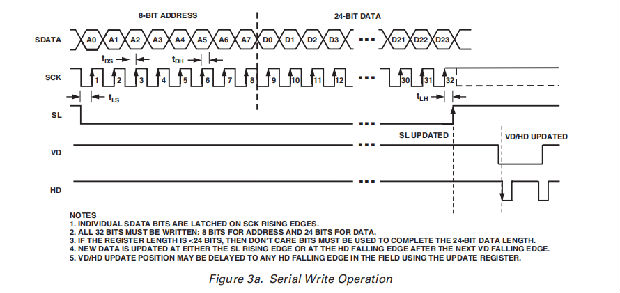

AD9948的所有内部寄存器都通过3线串行接口访问。每个寄存器由一个8位地址和一个24位数据字组成。8位地址和24位数据字都是从LSB开始写入的。要写入每个寄存器,需要32位操作,如图3a所示。尽管许多寄存器的宽度小于24位,但必须为每个寄存器写入所有24位。如果寄存器只有16位宽,那么上面的8位就不重要了,在串行写入操作期间可以用零填充。如果写入的数据少于24位,则寄存器将不会用新数据更新。

图3b显示了使用AD9948的地址自动递增功能向寄存器写入数据的更有效的方法。使用此方法,首先写入所需的最低地址,然后写入多个24位数据字。每个新的24位数据字将自动写入下一个最高寄存器地址。通过消除写入每个8位地址的需要,可以实现更快的寄存器加载。地址自动递增可以从任何寄存器位置开始使用,并且可以用于写入两个或整个寄存器空间。

完整的寄存器列表

所有地址和默认值都用十六进制表示。所有寄存器都如图3a所示进行了VD/HD更新,除了对于表I中所示的寄存器,它们是SL更新的。

精密定时高速定时产生

AD9948使用精密定时核心产生灵活的高速定时信号。该核心是产生用于CCD和AFE的定时的基础;复位门RG、水平驱动器H1-H4和SHP/SHD采样时钟。独特的结构使得系统设计者可以通过对水平CCD读数和AFE相关双采样的精确控制来优化图像质量。

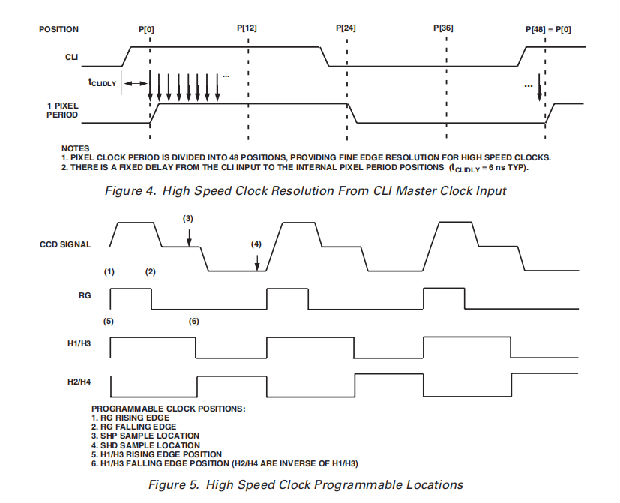

定时分辨率

精密定时核心使用1×主时钟输入(CLI)作为参考。该时钟应与CCD像素时钟频率相同。图4说明了内部定时核心如何将主时钟周期划分为48步或边缘位置。因此,精密定时核的边缘分辨率为(tCLI/48)。有关使用CLI输入的更多信息,请参阅应用程序信息部分。

高速时钟可编程性

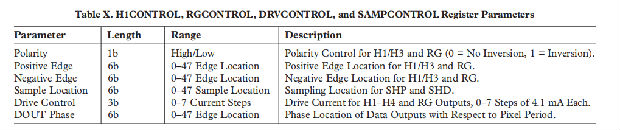

图5显示了高速时钟RG、H1-H4、SHP和SHD是如何生成的。RG脉冲具有可编程的上升和下降边缘,并且可以使用极性控制反转。水平时钟H1和H3具有可编程的上升和下降边缘,以及极性控制。H2和H4时钟总是分别与H1和H3相反。表X总结了高速定时寄存器及其参数。

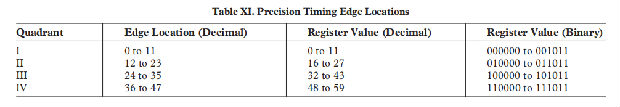

每个边缘位置设置的宽度为6位,但只有48个有效边缘位置可用。因此,寄存器值被映射成四个象限,每个象限包含12个边缘位置。表XI显示了相应边缘位置的正确寄存器值。

H驱动器和RG输出

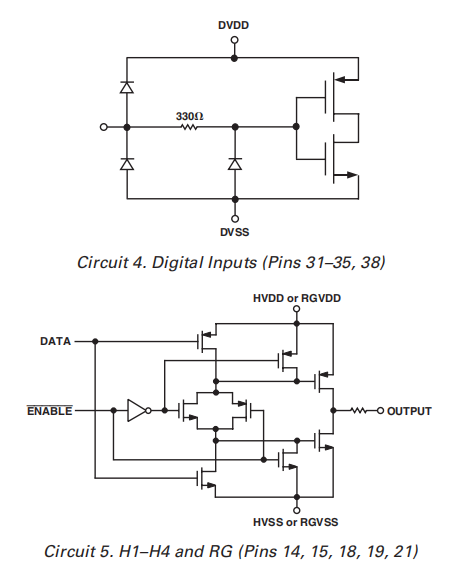

除了可编程定时位置外,AD9948还具有用于RG和H1–H4输出的片内输出驱动器。这些驱动器足够强大,可以直接驱动CCD输入。可调节H驱动器和RG驱动器电流

通过使用

DRV控制寄存器(地址x062)。DRV控制寄存器分为五个不同的3位值,每个值以4.1毫安的增量可调。最小设置0等于关闭或三种状态,最大设置7等于30.1毫安。

如图6所示,H2/H4输出与H1/H3相反。由信号反转引起的内部传播延迟小于l ns,这明显小于驱动CCD负载的典型上升时间。这导致在大约50%的输出摆幅下产生H1/H2交叉电压。交叉电压不可编程。

数字数据输出

AD9948数据输出阶段可使用双相寄存器(地址x064)。0到47之间的任何边可编程,如图7a所示。管道延迟数字数据输出如图7b所示。

AD9948数据输出相位可使用双相寄存器(地址x064)编程。从0到47的任何边都可以编程,如图7a所示。数字数据输出的管道延迟如图7b所示。

水平夹紧下料

AD9948的水平夹紧和消隐脉冲是完全可编程的,以适应各种应用。为每个信号定义单独的序列,然后在图像读出期间将其组织成多个区域。这允许在读出的每个阶段改变暗像素夹紧和消隐模式,以适应不同的图像传输定时和高速线移动。

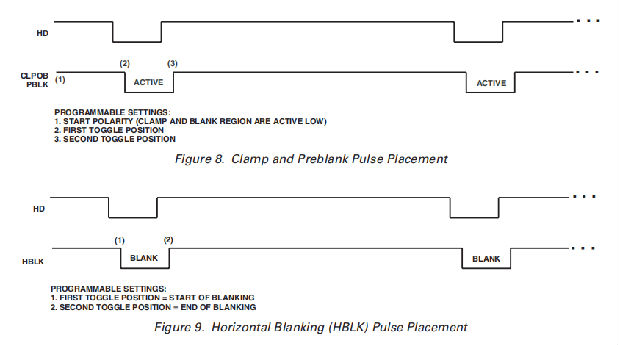

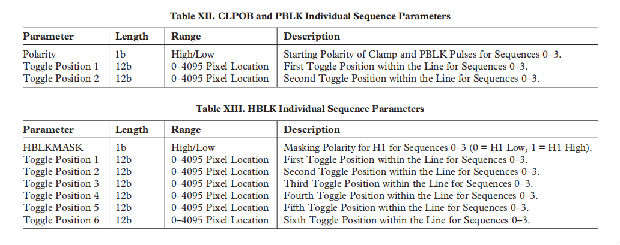

单个CLPOB和PBLK序列AFE水平定时由CLPOB和PBLK组成,如图8所示。这两个信号使用表XII所示的参数独立编程。开始极性、第一拨动位置和第二拨动位置对于每个信号都是完全可编程的。CLPOB和PBLK信号处于低激活状态,应进行相应编程。每个信号最多可创建四个单独的序列。

单个HBLK序列

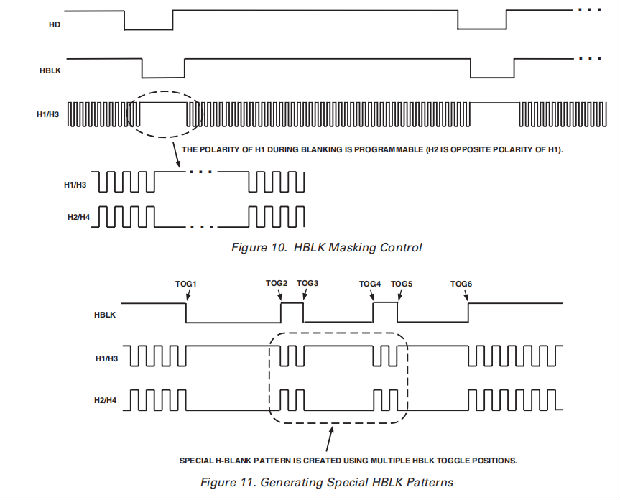

图9所示的HBLK可编程定时与CLPOB和PBLK类似。但是,没有启动极性控制。只有切换位置用于指定消隐周期的开始位置和停止位置。此外,还有一个极性控制,即HLBK掩模,它指定消隐期间的水平时钟信号H1-H4的极性。如图10所示,设置HBLKEMAX高电平将在消隐期间设置H1= H3=低和H2=H4=高。HBLK最多可使用四个单独的序列。

生成特殊的HBLK模式

六个切换位置可用于HBLK。通常,只有两个切换位置用于生成标准HBLK间隔。然而,额外的切换位置可用于生成特殊的HBLK模式,如图11所示。本例中的模式使用所有六个切换位置在HBLK间隔期间生成两组额外的脉冲。通过改变切换位置,可以创建不同的模式。

水平顺序控制

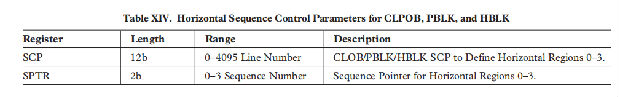

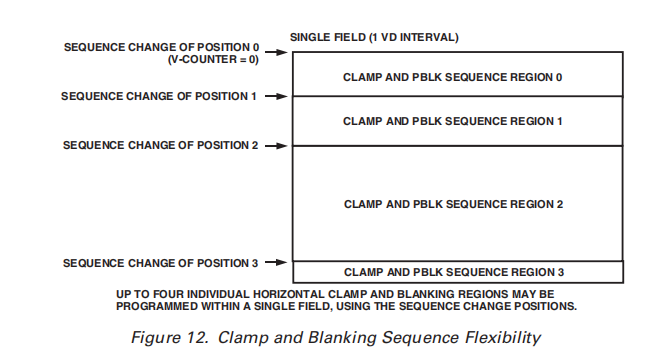

AD9948使用序列改变位置(SCP)和序列指针(SPTR)来组织各个水平序列。多达四个scp可用于将读出分为四个单独的区域,如图12所示。SCP 0总是硬编码到第0行,SCP1–SCP3是寄存器可编程的。在SCP限定的每个区域中,SPTR寄存器指定每个信号使用的序列。CLPOB、PBLK和HBLK各有一组单独的SCP。例如,CLPOBSCP1将为CLPOB定义区域0,并且在该区域中,可以使用CLPOBSPTR寄存器选择四个单独的CLPOB序列中的任何一个。下一个SCP定义一个新的区域,并且在该区域中,每个信号可以被分配到不同的单独序列。顺序控制寄存器汇总在表XIV中。

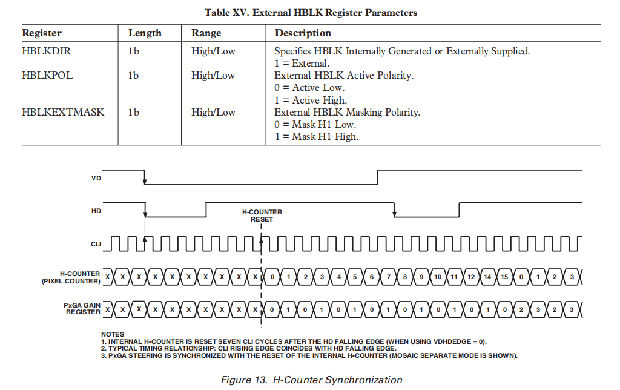

外部HBLK信号

AD9948也可与外部HBLK信号一起使用。将HBLKDIR寄存器(地址x040)设置为高将禁用内部HBLK信号生成。使用HBLKPOL寄存器指定外部信号的极性,使用HBLKMASK寄存器指定H1的屏蔽极性。表XV总结了使用外部HBLK信号时的寄存器值。

H计数器同步

H计数器重置在HD下降沿之后发生七个CLI周期。PxGA转向与内部H计数器复位同步(见图13)。

建议的通电顺序

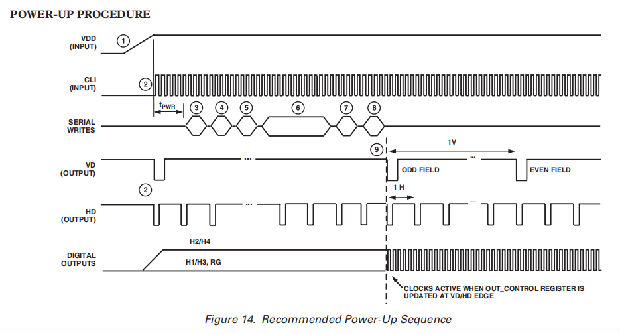

当AD9948通电时,建议按以下顺序操作(每个步骤参见图14):

1、打开AD9948的电源。

2、应用主时钟输入、CLI、VD和HD。

3、尽管AD9948包含一个片上通电复位,但建议对内部寄存器进行软件复位。将1写入SW_RST寄存器(地址x010),该寄存器将所有内部寄存器重置为其默认值。此位是自清除的,将自动重置回0。

4、必须通过将0写入TGCORE_RSTB寄存器(地址x012)然后将l写入TGCORE_RSTB寄存器来重置精确计时核心。这将启动内部计时核心操作。

5、将1写入预防更新寄存器(地址x014)。这将阻止串行寄存器数据的更新。

6、写入所需寄存器以配置高速计时和水平计时。

7、将1写入输出控制寄存器(地址x011)。这将允许输出在下一个VD/HD上升沿之后变为活动状态。

8、将0写入预防更新寄存器(地址x014)。这将允许在下一个VD/HD下降沿更新串行信息。

下一个VD/HD下降沿允许发生寄存器更新,包括使所有时钟输出都可用的OUT U控制。

模拟前端描述和操作

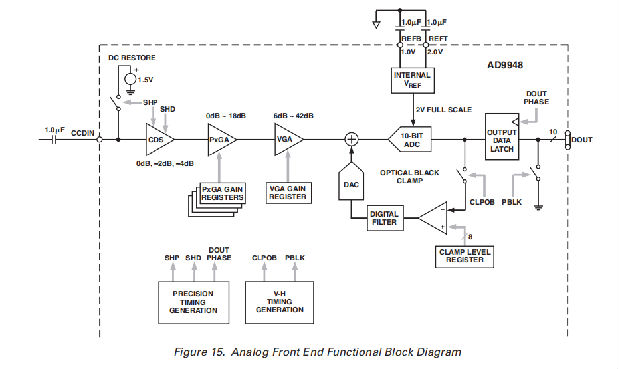

AD9948信号处理链如图15所示。每个处理步骤对于从原始CCD像素数据获得高质量图像至关重要。

直流还原

为了减小CCD输出信号的大直流偏移,采用了外接0.1μF串联耦合电容的直流恢复电路。这将使CCD信号的直流电平恢复到大约1.5v,以与AD9948的3v电源电压兼容。

相关双采样器

CDS电路对每个CCD像素进行两次采样,提取视频信息,抑制低频噪声。图5所示的定时说明了如何使用两个内部生成的CDS时钟SHP和SHD分别对基准电平和CCD信号电平进行采样。SHP和SHD采样边的位置由位于地址0x63的SAMPCONTROL寄存器的设置确定。这两个时钟信号的放置对于从CCD获得最佳性能至关重要。

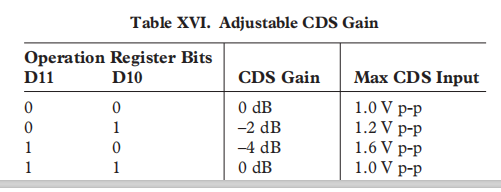

默认情况下,CDS的增益固定在0db。使用AFE操作寄存器中的位D10和D11,增益可以降低到-2db或-4db。这将允许AD9948接收大于1V p-p的输入信号。寄存器详情见表VIII。

PxGA

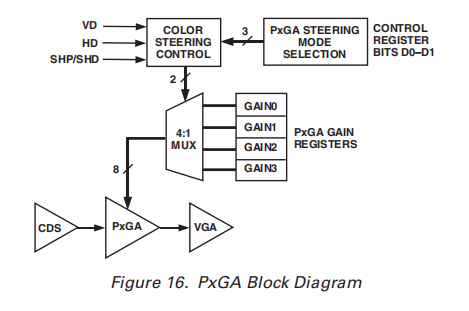

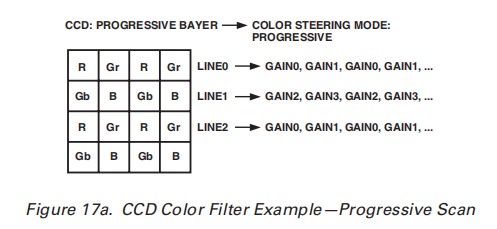

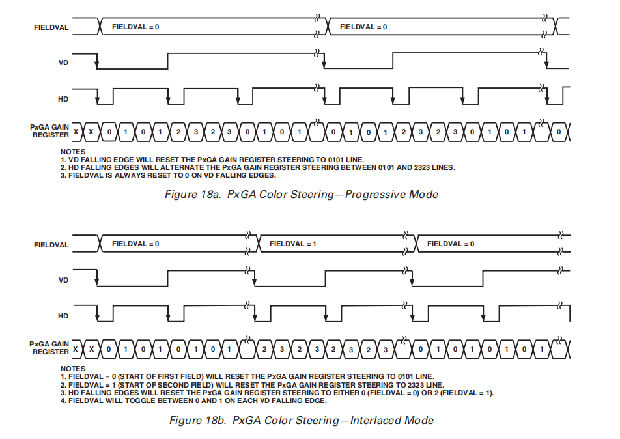

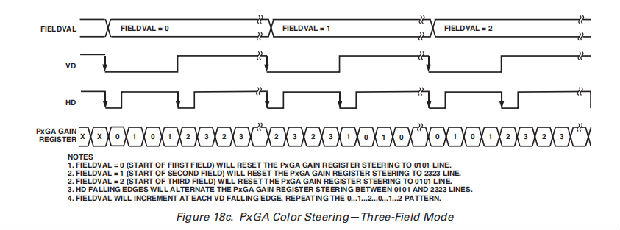

PxGA为各个颜色像素提供单独的增益调整。PxGA是一种具有四个独立值的可编程增益放大器,它能够在像素到像素的基础上复用其增益值(见图16)。这允许获得较低的输出颜色像素,以匹配较高的输出颜色像素。此外,PxGA可用于调整白平衡的颜色,减少所需的数字处理量。四个不同的增益值根据颜色控制电路进行切换。在地址0x03的AFE CTLMODE寄存器中,可编程三种不同类型的CCD彩色滤光片阵列的不同颜色控制模式(时序示例见图18a至18c)。例如,渐进式转向模式适应了流行的拜耳红、绿、蓝三色滤光片(见图17a)。

同样的拜耳模式也可以隔行扫描,隔行扫描模式应该与这种类型的CCD一起使用(见图17b)。颜色控制执行R、G和B增益值的正确多路复用(加载到PxGA增益寄存器中),并由用户使用垂直(VD)和水平(HD)同步脉冲进行同步。有关计时信息,请参见图18b。

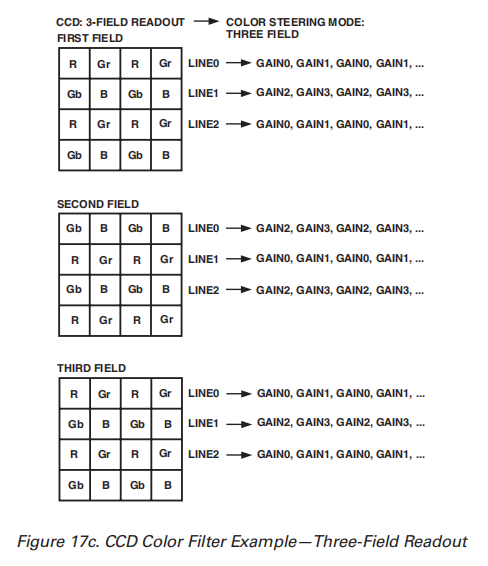

第三种类型的读出使用拜耳模式分为三个不同的读出领域。这种类型的CCD应使用三场模式(见图17c)。颜色控制执行R、G和B增益值的正确多路复用(加载到PxGA增益寄存器中),并由用户使用垂直(VD)和水平(HD)同步脉冲进行同步。有关计时信息,请参见图18c。

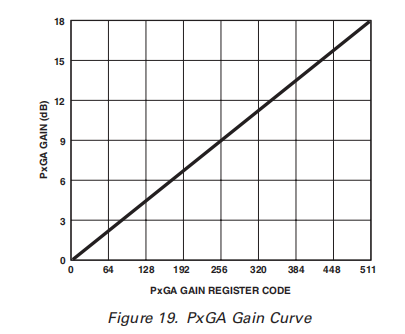

四个通道中的每个通道的PxGA增益在512步中从0db变为18db,使用PxGA GAIN01和PxGA GAIN23寄存器指定。PxGA增益曲线如图19所示。PxGA GAIN01寄存器为PxGA Gain0和Gain1各包含9位,PxGA GAIN23寄存器为PxGA Gain2和Gain3各包含9位。

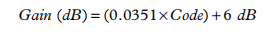

可变增益放大器

VGA级提供6分贝至42分贝的增益范围,可通过串行数字接口以10位分辨率编程。最小增益6db需要将1v输入信号与2v的ADC满标度范围相匹配。与1v满标度系统相比,等效增益范围为0db到36db。

VGA增益曲线遵循线性in-dB特性。使用公式可以计算任何增益寄存器值的精确VGA增益:

其中代码范围是0到1023。

对可应用于信号的最大增益量有限制。PxGA可以增加多达18分贝,而VGA能够提供多达42分贝。然而,来自PxGA和VGA的最大总增益被限制在42db。如果寄存器被编程为指定总增益大于42分贝,则总增益将被剪裁为42分贝。

A/D转换器

AD9948采用高性能ADC架构,针对高速和低功耗进行了优化。微分非线性(DNL)性能通常优于0.5lsb。ADC使用2 V输入范围。AD9948的典型线性和噪声性能曲线见TPC 1和TPC 2。

光学黑夹

光学黑钳位环路用于消除信号链中的残余偏移,并跟踪CCD黑电平的低频变化。在每条线上的光学黑(屏蔽)像素间隔期间,ADC输出与由用户在钳位寄存器中选择的固定黑电平基准进行比较。

该值可在0 LSB和63.75 LSB之间编程,256步。对产生的误差信号进行滤波以降低噪声,并通过D/a转换器将校正值应用到ADC输入端。通常情况下,每一条水平线都会打开一次光学黑夹环路,但此环路可以更新得更慢,以适应特定的应用。如果在后处理期间使用外部数字钳位,则可以使用OPRMODE寄存器中的位D2禁用AD9948光学黑钳位。当环路被禁用时,钳位寄存器仍可用于提供可编程的偏移调整。

CLPOB脉冲应该放置在CCD的光学黑色像素期间。建议CLPOB脉冲持续时间至少为20像素宽,以最小化钳位噪声。可以使用较短的脉冲宽度,但钳位噪声可能增加,跟踪黑电平低频变化的能力将降低。有关计时示例,请参见水平夹紧和消隐以及应用程序信息部分。

数字数据输出

AD9948数字输出数据使用双相寄存器值锁存,如图15所示。输出数据计时如图7所示。也可以使输出锁存透明,以便数据输出立即从A/D转换器有效。将AFE控制寄存器位D4编程为1将设置输出锁存透明。也可以通过将AFE控制寄存器位D3设置为1来禁用数据输出(三个状态)。

数据输出编码通常是直接二进制的,但通过将AFE控制寄存器位D5设置为1,编码将变为灰色编码。

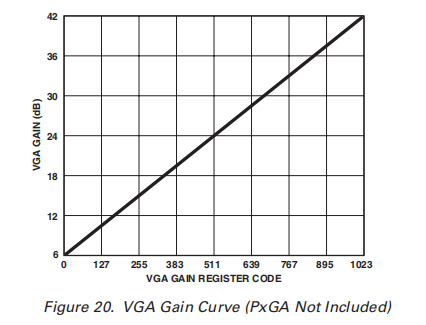

应用信息电路配置

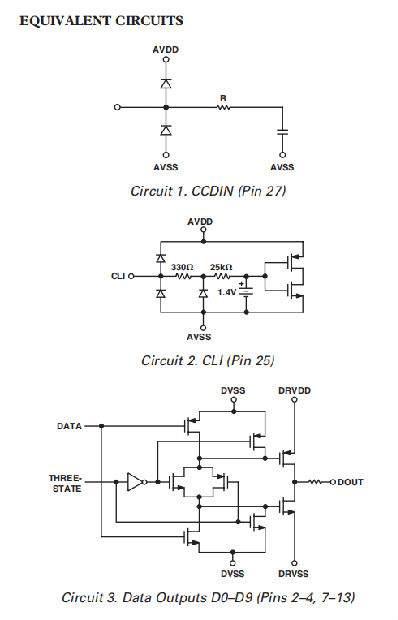

AD9948推荐的电路配置如图21所示。要从AD9948获得良好的图像质量,需要仔细注意PCB布局。所有信号的路由应保持低噪声性能。CCD输出信号应通过0.1μF电容器直接路由至引脚27。主时钟CLI应小心地路由到引脚25,以尽量减少对CCDIN、REFT和REFB信号的干扰。

数字输出和时钟输入位于引脚2至13和引脚31至39上,应与远离模拟和CCD时钟信号的数字ASIC连接。将串联电阻放在数字输出引脚附近可能有助于降低数字代码转换噪声。如果数字输出必须驱动大于20pf的负载,建议缓冲以最小化附加噪声。如果数字ASIC可以接受灰码,则可以选择AD9948的输出以使用控制寄存器位D5以灰码格式输出数据。与二进制编码相比,灰度编码有助于降低潜在的数字转换噪声。

H1-H4和RG记录道应具有低电感,以避免信号过度失真。由于CCD电容负载对H1-H4的瞬态电流需求较大,建议使用较重的记录道。如果可能的话,将AD9948物理定位在更靠近CCD的位置将减少这些线路上的电感。与往常一样,从AD9948到CCD的路由路径应尽可能直接。

接地和去耦建议

如图21所示,AD9948建议使用单一接地平面。接地平面应尽可能连续,尤其是插脚23至30周围。这将确保所有模拟去耦电容器在电源和旁路引脚及其各自接地引脚之间提供尽可能低的阻抗路径。所有高频去耦电容器应尽可能靠近封装引脚。建议将包装底部裸露的挡板焊接到一个大焊盘上,焊盘与地平面之间有多个通孔。

所有电源管脚必须用高质量高频片式电容器去接地。对于每个主电源AVDD、RGVDD、HVDD和DRVDD,也应该有4.7μF或更大的旁路电容器,尽管这对于每个单独的管脚是不必要的。在大多数应用中,更容易共享RGVDD和HVDD的电源,只要单独绕过各个电源管脚,就可以这样做。DRVDD可以使用单独的3V电源,但该电源引脚仍应与芯片的其余部分断开至同一接地平面。不建议为DRVSS单独接地。

参考旁路管脚(REFT,REFB)应尽可能靠近其各自的管脚与接地分离。模拟输入(CCDIN)电容器也应靠近管脚。

驱动CLI输入

AD9948的主时钟输入(CLI)可用于两种不同的配置,具体取决于应用程序。图23a显示了来自主时钟源的典型dc耦合输入。当使用直流耦合技术时,主时钟信号应为标准3v CMOS逻辑电平。如图23b所示,可以在时钟源和CLI输入之间使用1000 pF ac耦合电容器。在此配置中,CLI输入将自偏置到大约1.4v的适当直流电压电平。当使用交流耦合技术时,主时钟信号的振幅可以低至±500mv。

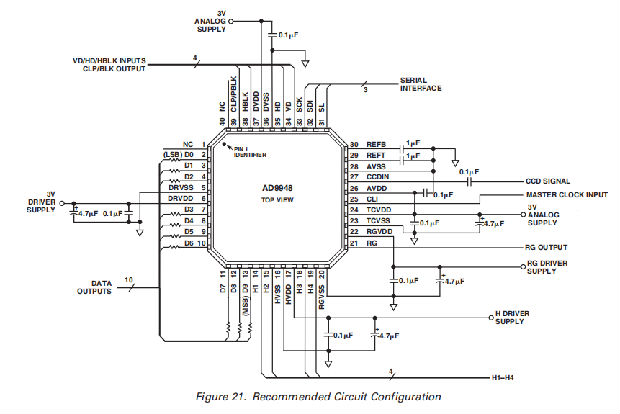

水平时序示例

图24显示了一个CCD布局示例。水平寄存器包含28个虚拟像素,这些像素将出现在从CCD计时的每一行上。在垂直方向上,在读出前端有10条黑色(OB)线,在读出后端有2条黑色(OB)线。水平方向在前面有四个OB像素,在后面有48个。

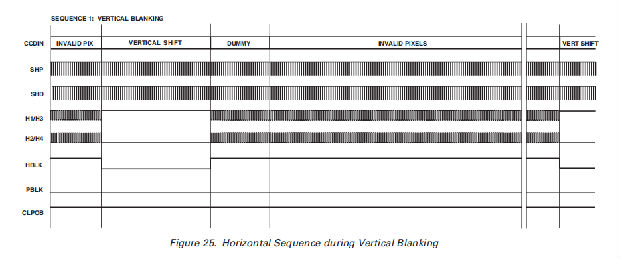

为配置此CCD的AD9948水平信号,可以使用三个序列。图25显示了在垂直消隐期间使用的第一个序列。在此期间,传感器没有有效的OB像素,因此不使用CLPOB信号。在这段时间内,可能会启用PBLK,因为没有有效的数据可用。

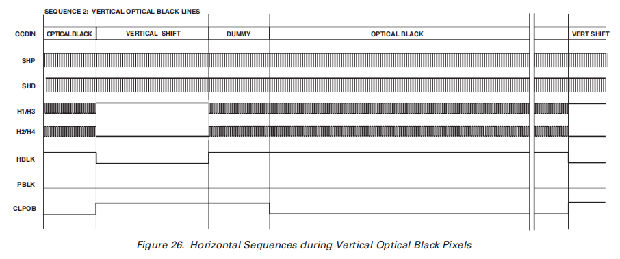

图26显示了垂直OB间隔的推荐顺序。为了稳定AD9948的钳位回路,钳位信号被用于整条线路。

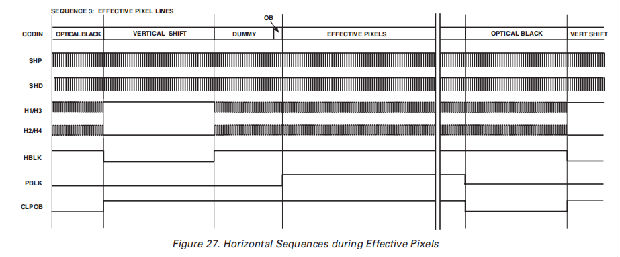

图27显示了有效像素读出的推荐顺序。每行末尾的48个OB像素用于CLPOB信号。

外形尺寸

40引线框架芯片级封装;6毫米6毫米机身(CP-40);尺寸单位为毫米