CY7C68300B/CY7C68301B

CY7C68320/CY7C68321

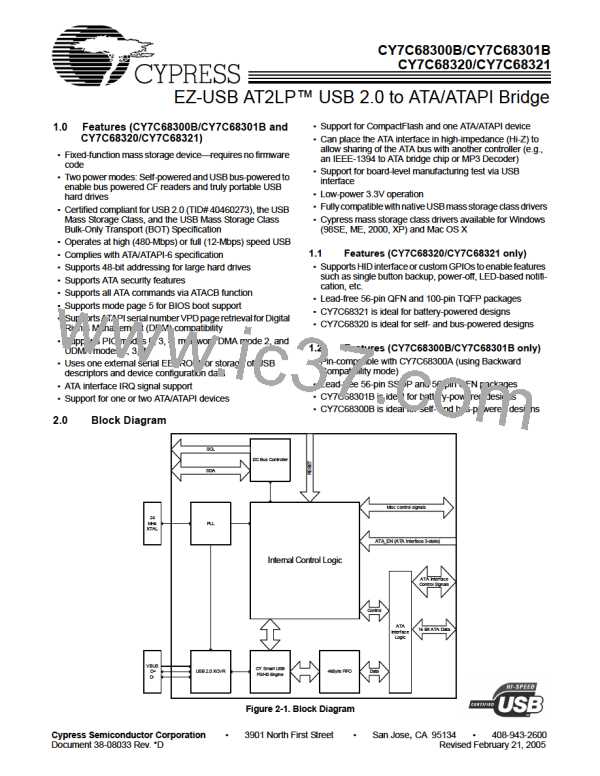

5.1

Pin Diagrams

1

2

56

DD13

DD12

DD14

DD11

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

3

DD15

DD10

4

GND

DD9

5

ATAPUEN (GND)

VCC

DD8

6

(ATA_EN) VBUS_ATA_ENABLE

7

GND

VCC

8

IORDY

RESET#

9

DMARQ

AVCC

GND

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

A RESET#

XTALOUT

XTALIN

AGND

(VBUS_PWR_VALID ) DA2

CS1#

CS0#

VCC

(DA2) DRVPWRVLD

DA1

DPLUS

DMINUS

GND

EZ-USB AT2LP

DA0

INTRQ

VCC

CY7C68300B

CY7C68301B

56-pin SSOP

VCC

GND

DMACK#

DIOR#

DIOW#

GND

PWR500# (PU 10K)

GND ( Reserved)

SCL

SDA

VCC

NOTE: Labels in italics denote pin functionality

during CY7C68300A compatibility mode.

VCC

DD0

DD1

DD2

DD3

GND

DD7

DD6

DD5

DD4

Figure 5-2. 56-pin SSOP Pinout (CY7C68300B/CY7C68301B only)

Document 38-08033 Rev. *D

Page 3 of 36

CYPRESS [ CYPRESS ]

CYPRESS [ CYPRESS ]