WM9705多媒体AC'97编解码器集成触摸屏控制器

日期:2019-4-27描述WM9705是一款高品质的立体声音频编解码器集成触摸屏控制器。音频部分符合Intel AC'97 Rev 2.2规格。它执行全双工18位编解码器功能和支持从8到48k样本/秒的可变采样率高信噪比。可选的AC'97功能包括3D声音增强,线路电平输出,立体声缓冲耳机输出,硬件采样率转换,主/辅模式操作和S / PDIF输出。耳机自动检测,I 2 S输出和耳机缓冲单声道输出包括在内。此外,WM9705还集成了完整的4线触控功能屏幕控制器,包括片上屏幕驱动程序,下笔检测功能和压力测量功能。5引脚数字双向AC-Link串行接口允许控制数据和DAC和ADC字的传输和传输AC'97控制器。 WM9705可在3V或5V下完全工作或混合3 / 5V电源,并在行业中包装标准48引脚TQFP封装,7mm主体尺寸,或者较小的7×7×0.9mm QFN。

特征

带有数字转换器的AC'97 rev2.2兼容编解码器

18位立体声音频编解码器

片上采样率转换

多通道输入混音器

S / PDIF数字音频输出

AUX和MONO输出上的耳机驱动程序

带有坐标和坐标的4线触摸屏界面压力测量和落笔检测

笔下唤醒从睡眠模式唤醒

3V至5V工作电压

广泛的电源管理功能,包括硬件断电选项

采用48引脚TQFP封装或48引脚的标准AC'97引脚排列

QFN包。

应用

个人数字助理和“智能手机”

PocketPC系统

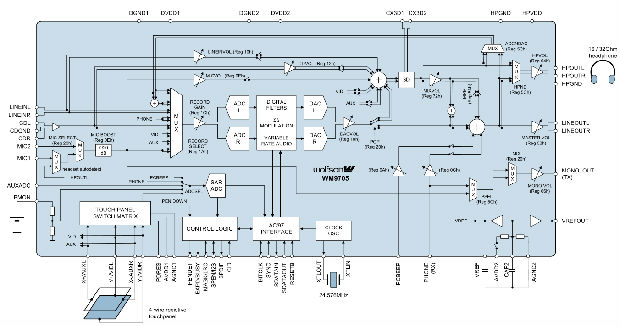

框图

绝对最大额定值绝对最大额定值仅为压力额定值。连续操作可能会对设备造成永久性损坏或超出这些限制。设备功能操作限制和保证的性能规格在Electrical下给出指定测试条件下的特性。ESD敏感器件。该器件采用CMOS工艺制造。因此通常易受影响过度静电电压造成的损坏。在处理和存放期间必须采取适当的ESD预防措施这个设备。Wolfson根据IPC / JEDEC J-STD-020B测试其封装类型的湿度敏感性,以确定可接受的存储表面贴装组装前的条件。这些级别是:MSL1 =在<30°C / 85%相对湿度下无限制的使用寿命。通常不存放在防潮袋中。MSL2 =在<30°C / 60%相对湿度下袋外储存1年。提供防潮袋。MSL3 =在<30°C / 60%相对湿度下袋外储存168小时。提供防潮袋。每种包装类型的湿度敏感度等级在订购信息中指定。注意:TQFP版本被归类为MSL1,不需要进行干式包装,但将以此类型提供,标记为MSL1。

条件MIN MAX

数字电源电压-0.3V + 7V

模拟电源电压-0.3V + 7V

电压范围数字输入DVSS -0.3V DVDD + 0.3V

电压范围模拟输入AVDD -0.3V AVDD + 0.3V

工作温度范围,T A -25 o C +85 o C.

焊接后的储存温度-65 o C +150 o C.

包装体温(焊接10秒)+240 o C.

包装体温(焊接2分钟)+ 183 o C

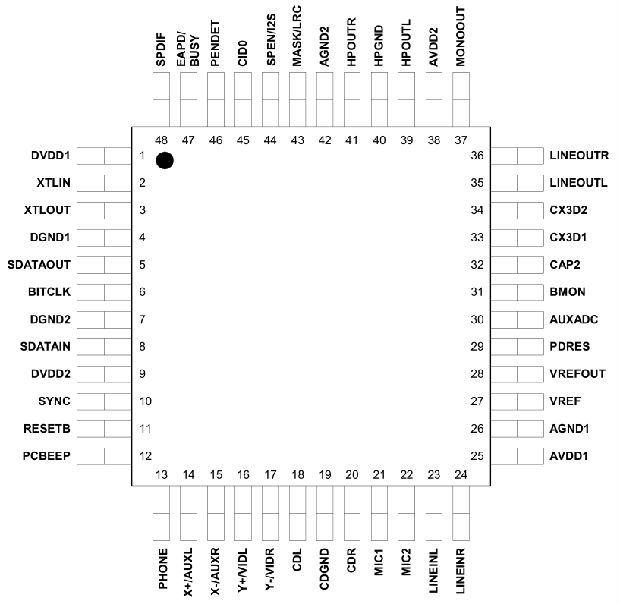

PIN配置

图1 TQFP引脚排列

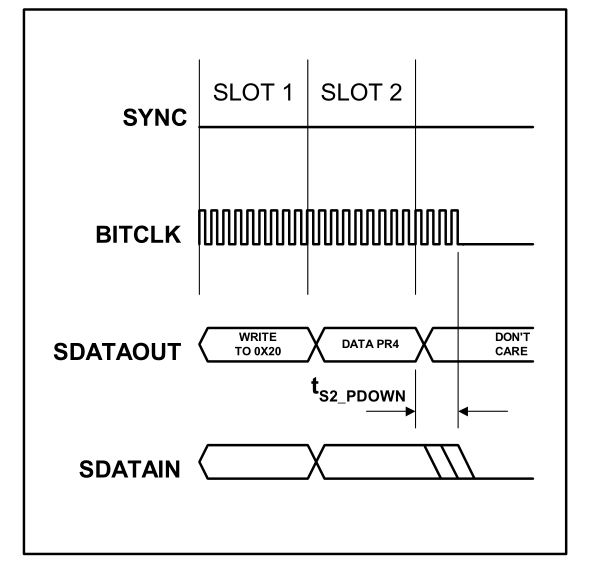

详细的时序图

测试特征:

除非另有说明,AVDD = 3.3V,DVDD = 3.3V,AGND = 0V ............ ..T A = 0 o C至+70 o C。

除非另有说明,否则所有测量均在10%至90%DVDD下进行。 以下所有时间信息均得到保证,

未经测试。

AC-LINK低功耗模式

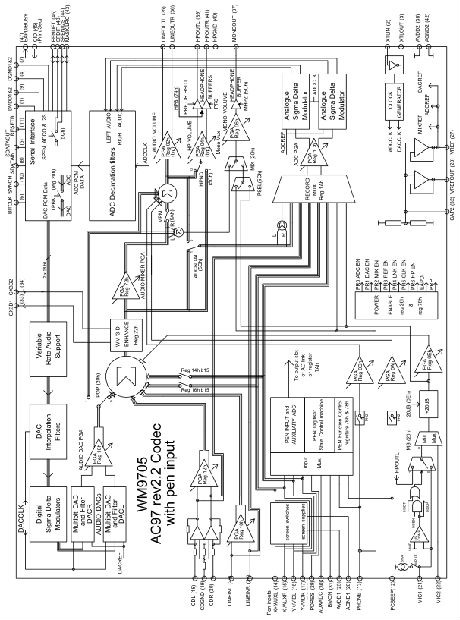

设备说明介绍本规范描述了WM9705音频编解码器,它设计为软件和硬件与Intel AC'97 rev2.2组件规范兼容。该设备是一个基本AC'97编解码器的衍生产品,增加了对电阻式触摸屏笔输入的支持。可变速率音频(VRA)支持英特尔rev2.1或rev2.2规范中定义的速率,并且提供SPDIF输出端口,其可以可选地用于输出PCM DAC信息到外部处理器。笔数字化器功能操作的一个关键特征是当笔从屏幕上抬起时,屏幕驱动器活动停止,从而最大限度地减少音频性能下降和降低功耗。WM9705提供以下功能:英特尔指定的立体声音频编解码器支持不同的音频采样率Pen Digitiser功能,具有4线笔接口,支持笔下检测,笔压力测量和唤醒。辅助ADC输入,用于温度,电源和电池监控。Pen-down标志和ADC BUSY标志,输出到引脚,以及MASK输入引脚,允许延迟在LCD活动中笔转换可选的SPDIF和I 2 S音频输出(SPDIF输出可能是硬件启用,所以不需要司机支持)耳机驱动功能和耳机或耳机插头的可选自动检测强烈建议同时研究英特尔AC'97 rev2.2规范文档:该规范可以从英特尔网站下载。WM9705完全可以在3V或5V或混合3 / 5V电源下工作,并且封装在行业标准48pin TQFP封装,7mm机身尺寸

AC'97特色WM9705实现了AC'97 rev2.2功能的基本设置,以及一些增强功能:支持所有rev2.2规定的可变音频采样率3-D立体声增强功能。AUX输出上的耳机支持(引脚39,41)通过CID0引脚的引脚编程实现主/次编解码器操作SPDIF音频输出,符合rev2.2控制设置。

非 - AC'97特点除了提供的AC'97功能外,WM9705还支持:带有集成屏幕驱动器的4线笔式数字转换器,具有高度灵活的操作模式,支持自主屏幕转换和辅助转换。屏幕X和Y.从AUX和VID立体声输入引脚驱动的连接仍然连接。MONO输出的耳机驱动能力,带有额外的信号路由开关PSEL,允许PHONE输入被路由到MONO输出混音器后的额外开关HPND允许没有DAC信号的MIX输出到耳机输出,因此允许没有MIX的DAC输出到LINE输出。I 2 S音频输出功能,除了SPDIF输出外,还支持额外的外部功能用于多通道解决方案的音频DAC。 SPDIF输出可能是硬件启用的。选择将立体声音频ADC输出路由到SPDIF和/或I 2 S数字输出自动检测插入AUX耳机输出的耳机或耳机,内置麦克风信号从耳机引脚到MIC1输入的路由。电池监控输入BMON支持直接连接电池电压高达6.5V。MPM开关允许将DAC +混频器输出混合到MONOUT和DAC +的独立混合将电话和/或PCBEEP连接到LINEOUT或HPOUT上。重置掉电覆盖 - 在复位时将MASK保持为高电平会覆盖PR位,从而强制执行WM9705进入低功耗模式

PEN DIGITIZER和AUXILIARY ADCWM9705包含4线输入笔数字转换器功能。该电路包括驱动电路驱动PDA上使用的典型电阻式触摸屏,加上12位分辨率的ADC转换笔输入值。该ADC还可用于执行额外的辅助ADC转换AUXADC,BMON,PCBEEP或PHONE引脚上的电平。控制位(寄存器78h中的PHIZ)用于允许PCBEEP和PHONE输入变高如果需要,阻抗(内部断开,因此信号路径被切断)。数字转换器功能的操作由数字转换器控制寄存器76h和78h控制。通过读取寄存器7Ah中位[11-0]的内容获得ADC转换结果,或者可选地通过启用AC链接SLOT传输方法,当结果被发回时AC'97插槽数据格式。笔式数字转换器ADC是12位逐次逼近型转换器具有出色的差分非线性性能。笔式数字转换器ADC可用于转换笔输入数据或存在的电压AUXADC,BMON,PCBEEP或PHONE引脚。电池监控等功能因此可以实施温度测量。以下数字数字转换器功能可用:支持唤醒笔笔下检测,压力测量,辅助转换MASK转换延迟覆盖或同步操作选项SLOT或R / W寄存器数据传输可编程屏幕驱动器采样延迟可编程击穿检测阈值笔式数字转换器操作的详细信息可在笔式数字转换器描述部分中找到。注意分配给X / Y屏幕连接的引脚是通常用于AUX和AUX的引脚传统AC '97编解码器中的VID立体声输入。在WM9705中,这些引脚保持连接混频器和ADC输入,可用作模拟输入,具有增益限制通过混频器输入固定为0dB。使用中的第15位提供正常的MUTE功能适当的登记。建议在屏幕上保留这些MUTE位“静音”被驱使。读回寄存器将报告0dB增益,并将MUTE值报告为已编程。AUX和VID输入的ADC增益控制正常工作。

三维立体声增强该设备包含一个立体声增强电路,旨在优化聆听体验当设备用于典型的PC操作环境时。也就是说,配有一对扬声器放置在显示器的两侧,几乎没有空间分隔。这个电路产生了不同通过对左右声道播放数据进行差分信号,然后使用滤波器对该差分信号进行滤波低通和高通滤波器,其时间常数使用连接的外部电容设置CX3D引脚33和34.通常,100nF和47nF的值设置为高通和低通极点分别约为100Hz和1kHz。该频带对应于范围耳朵对方向效应最敏感。滤波后的差分信号通过使用写入的4位值设置的量进行增益调整寄存器22h位3到0.值0h禁用,值Fh是最大效果。通常值为8h是最佳的。用户界面最通常使用滑块类型的控件来允许用户调整增强级别以适应程序材料。寄存器20h中的位D13 3D是整体3D启用位。复位寄存器00h以位D14至D10读回值11000。这对应于十进制24,它在英特尔注册为Wolfson Stereo Enhancement。注意,设置应用于差信号的滤波极的外部电容器可以是调整值,甚至替换为引脚之间的直接连接。如果这样调整然后,可以产生反馈到主信号路径中的差信号量显着的,并且可能导致可能限制,扭曲或过驱动信号路径的大信号扬声器。小心调整这些值,以选择首选的声学效果。没有提供伪立体声效果。单声道信号将不会应用增强(如果信号是同相和相同的幅度)。来自PCM DAC通道的信号可以具有立体声增强适用。

如果需要,它也可以被旁路。通过设置启用此功能寄存器20h中的POP位。可变采样率支持该器件上的DAC和ADC支持所有建议的采样率英特尔AC'97 rev2.1和rev2.2音频速率规范。默认速率为48ks / s。如果选择替代速率并启用可变速率音频(寄存器2Ah,位0),AC'97接口继续以每秒48k字的速度运行,但数据通过链路传输突发使得实现所选择的净采样率。这取决于AC'97 Revision 2.1 / 2兼容控制器,以确保数据提供给AC链路,并从AC链路接收,以适当的速度。通过写入寄存器2Ch(DAC)和32h(ADC)来选择可变速率。 ADC和DAC速率可以独立设置,左右声道始终保持相同的速率。注意注册2Ch只应在DAC上电时写入,类似地,寄存器32h应该只有当ADC上电时写入(参见寄存器26h进行功率控制)。设备支持按需抽样。也就是说,当DAC信号处理电路需要另一个样本时,a样本请求被发送到控制器,控制器必须在下一帧中用数据样本进行响应它发送。例如,如果选择24ks / s的速率,则设备平均会请求样本对于每个立体声DAC,每隔一帧从控制器开始。请注意,如果不支持如果速率写入其中一个速率寄存器,则速率将默认为最接近的速率。该然后,当被询问时,寄存器将以设备默认支持的速率响应。WM9705时钟将自动缩放,具体取决于MCLK频率,其中MCLK不等于24.576MHz。使用24MHz时钟,BCLK频率预计为12MHz和采样频率(SYNC0预期为BCLK / 256 = 46.875kHz。

SPDIF或I 2 S DIGITAL AUDIO DATA OUTPUT通过将引脚44(SPEN)保持为高电平,可以在硬件中启用WM9705 SPDIF输出RESETB变为高电平,或通过写入寄存器2Ah中的SPDIF控制位。如果SPDIF引脚48是通过弱上拉(例如100k)在启动时拉高,然后寄存器28h中的SPDIF能力位为设置为'0',即没有SPDIF功能。这允许填充选项,以便在SPDIF外部时没有提供组件,驱动程序将看到“没有SPDIF功能”和“灰色”相关的控制面板中的框。另外,数字音频可以使用引脚44(SPEN)作为数据输出以I 2 S格式输出,并将帧时钟或LRCLK输出到引脚43上。使用数据将数据输入到引脚44上常规BITCLK为256fs,如果数据被带到a,那么它也可以用作MCLK外部DAC。通过将寄存器5Ch中的位I 2 S置1来选择此模式下的操作。 64fs bitclk是通过将寄存器74h中的位I2S64置1,也可以在SPDIF上输出。注意I 2 S.操作仅支持48ks / s操作。 SPDIF操作的硬件选择引脚SPEN'hi'与I 2 S操作兼容,前提是弱上拉(大约100k)用于在启动时保持SPEN为高电平。当I 2 S为时,SPEN引脚变为I 2 S数据输出引脚使能,此引脚上的弱上拉被过驱动。对于SPDIF和I 2 S模式,输出的数据可以通过AC从WM9705发送链接在与普通DAC数据相同的插槽中,或者可以在不同的插槽中发送。输出插槽包含SPDIF / I 2 S数据由寄存器2Ah中的SPSA [1:0]位选择。 WM9705符合标准关于槽映射的AC'97 rev2.2规范;因此默认模式操作是从音频数据之后的下一个数据时隙输出SPDIF或I 2 S数据目前正在使用的插槽。或者,如果需要,可以从任何可用的数据映射数据通过使用SPSA位选择插槽。下表显示了音频的默认插槽映射DAC和SPDIF / I 2 S数据:(稍后在寄存器描述部分中进一步详述)。

但是,启用SPDIF操作时会对rev2.2映射表执行例外处理使用SPEN硬件使能引脚(在启动时保持高电平):在这种情况下,SPDIF数据为立即从DAC主插槽3和4输出。这允许无驱动器SPDIF操作,其中SPDIF或I 2 S输出只是主音频DAC中包含的数据通道。通道状态和控制位输出以及SPDIF数据如下所示SPDIF控制寄存器3Ah。如果需要,则可以改变SPDIF数据信道时隙映射通过根据需要设置SPSA位。有关详细信息,提供一种模式,ADC的输出作为SPDIF或I 2 S数据发送出去以上,而不是通过AC链路发送到DAC的数据。通过设置位使能该模式ADCO在5Ch注册。 ADC数据继续通过AC链路正常发送到控制器。WM9705仅以默认的48ks / s帧速率支持SPDIF和I 2 S数据。写入SPSR位在寄存器3Ah中,除了默认的48ks / s速率之外的任何值都将导致写入失败在随后读取这些值时返回48ks / s值。主要/次要身份证明支持WM9705支持作为主编解码器或辅助编解码器的操作。配置通过将CID0引脚45连接到封装上来选择器件作为主器件或辅助器件。从根本上说,标识为主要设备(ID = 0,CID0 ='hi')会产生BITCLK作为输出,而辅助(任何其他ID)必须提供BITCLK作为输入。这有显而易见的是,如果AC链路上的主设备被禁用,则辅助设备不能运作。 AC'97 Revision 2.2规范定义CID0引脚具有反相功能感觉,并提供内部弱上拉。因此,如果没有连接然后选择CID0引脚,引脚拉线和ID = 0,即初级线圈。外部接地(下拉从0到10kΩ)将选择编解码器ID ='1'。

耳机驱动器和耳机自动检测HPOUT输出引脚39和41(称为AUXOUT输入)提供耳机驱动功能AC'97 rev2.2规范)以及MONOOUT输出引脚37。阻抗通常从16Ω以上的耳机可以连接到这些引脚。 AC建议使用适当大小的电容耦合去除中轨DC这些输出上存在基座。 AC'97 rev2.2规格推荐使用32Ω耳机;如果一个耳机连接用作耳机,立体声耳机并行驱动,然后每个胶囊必须具有至少32Ω的阻抗。在许多应用中,希望能够将立体声耳机连接到耳机输出引脚或单声道耳机,包括耳机和麦克风。该麦克风信号通过典型3线插孔的尖端连接线发送。在这种情况下它是希望能够自动检测耳机或耳机的连接(用麦克风)。耳机和麦克风的主要特点相比耳机是麦克风阻抗通常远高于耳机胶囊(假设一个典型的动圈耳机)。因此,可以连接一个弱上拉到耳机插孔的尖端连接。

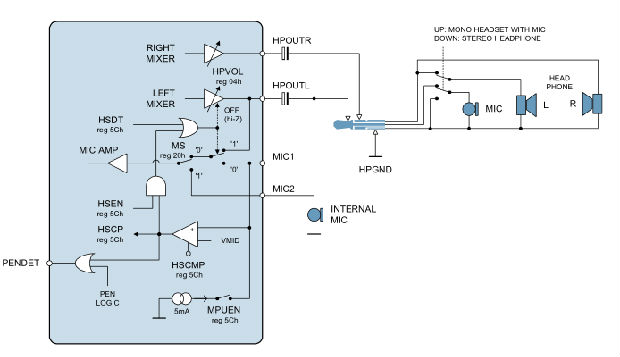

连接耳机时,耳机的低阻抗接地会拉低DC接近地面。如果插入带麦克风的耳机,则会出现高阻抗麦克风不会拉低尖端连接上的直流电平,此引脚上的DC现在上升接近正供应。检测到DC电平的这种变化,因此允许检测变化耳机到麦克风,(当然没有任何插入)。当检测到此事件时,驱动尖端连接的耳机放大器关闭,此引脚上的信号为而是作为麦克风输入路由到MIC1输入。通过设置HSCMP位使能该自动检测比较器。上拉电流由启用将寄存器5Ch中的MPUEN位置1,同时切换PENDET引脚上的中断信号。当HSDT位置1时,mic1输入连接到一个比较器,其阈值设置为轨。当比较器输出为低电平时,则启用耳机驱动器。当。。。的时候比较器输出变高(即上拉电流乘以外部阻抗)mic1引脚上的地线大于中间轨道),耳机放大器关闭了mic1信号从耳机输出引脚(39)内部获取。

示意性地显示了该功能 可以访问比较器的输出信号通过读取寄存器5Ch中的HSCP位。 可以通过设置HSEN位或外部来使用自动检测通过使用HSDT位进行控制,该位是强制耳机处于三态状态的重叠麦克风路径切换功能发生。例如,该功能允许使用具有麦克风的立体声耳机连接导线和开关。 该开关将耳机变为单声道耳机麦克风通过插孔上的尖端连接进行连接。 如果用于MP3等产品有能力的手机,它将允许用户简单地从耳机使用切换到耳机使用在耳机线中切换单个开关,同时接听或启动电话。 也可以使用上拉电流来提供所谓的“幻像”通过适当选择麦克风为动态麦克风供电。

AC-LINK DIGITAL SERIAL INTERFACE PROTOCOL

提供了一个数字接口来控制WM9705并从中传输数据。这个串行接口与Intel AC'97规范兼容。

主要控制界面功能是:

•通过混频器控制模拟增益和信号路径

•ADC和DAC字与AC'97控制器的双向传输

•选择省电模式

•控制笔数字化仪功能

•从编解码器传输笔数字化仪信息和辅助转换结果

WM9705采用5针数字串行接口,可将其连接到AC'97控制器。 AC-ink是双向,固定速率的串行PCM数字流。它处理多个输入和输出音频流,以及采用时分复用(TDM)的控制寄存器访问方案。 AC-link架构将每个音频帧分为12个传出和12个传入数据流,每个都具有20位样本分辨率。具有最低要求的DAC和ADC

分辨率为16位,AC'97也可以采用18或20位DAC / ADC分辨率实现,给出了AC-link架构提供的空间。 WM9705支持18-位音频操作。

WM9705控制器发出所有AC-link数据事务的同步信号。该WM9705将串行位时钟驱动到AC-link上,然后AC'97控制器符合a同步信号构造音频帧。固定为48kHz的SYNC是通过分频串行时钟(BITCLK)得到的。 BITCLK,固定在12.288MHz,提供必要的时钟粒度,支持12位,20位输出和传入时隙。 AC-link串行数据在BITCLK的每个上升沿转换。该AC链路数据的接收器,(WM9705用于输出数据,AC'97控制器用于输入数据),对BITCLK下降沿的每个串行位进行采样。AC链路协议提供特殊的16位时隙(时隙0),其中每个位传送a当前音频帧内相应时隙的有效标记。给定位位置为1时隙0表示当前音频帧内的相应时隙已经存在分配给数据流,并包含有效数据。如果标记的插槽无效,则为负责数据来源,(WM9705为输入流,AC'97控制器为输出流),在该时隙的活动时间内填充0的所有位位置。在每个音频帧的开头,SYNC保持高电平,总持续时间为16 BITCLK。SYNC为高的音频帧部分被定义为标签阶段。剩下的SYNC为低电平的音频帧定义为数据相位。另外,对于电源可以停止节省,所有时钟,同步和数据信号。这需要WM9705实现为静态设计,以允许其注册内容在输入时保持不变省电模式。

AC-LINK音频输出帧(SDATAOUT)音频输出帧数据流对应于所有数字输出的多路复用束针对WM9705的DAC输入和控制寄存器的数据。 正如前面简要提到的那样音频输出帧最多支持12个20位输出数据时隙。 插槽0是特殊保留的包含16位的时隙,用于AC链路协议基础设施。在时隙0内,第一位是全局位(SDATAOUT时隙0,位15),用于标记有效位整个音频帧。 如果有效帧位为1,则表示当前音频帧包含至少一个有效数据的时隙。 WM9705采样的下一个12位位置指示相应的12个时隙中的哪个包含有效数据。以这种方式,不同采样率的数据流可以在其固定的AC链路上传输48kHz音频帧率

新的音频输出帧从SYNC的低到高转换开始,如图13所示。SYNC与BITCLK的上升沿同步。在紧随其后的下降边缘BITCLK,WM9705采样SYNC的断言。这个下降的边缘标志着时间AC-link的两端都知道新音频帧的开始。在下一个上升的边缘BITCLK,AC'97将SDATAOUT转换为时隙0的第一个比特位置(有效帧比特)。每新的位位置在BITCLK的上升沿呈现给AC链路,随后被采样WM9705在BITCLK的下一个下降沿。此序列可确保数据转换传入和传出数据流的后续采样点是时间对齐的。基准AC'97指定的音频功能必须始终采样率转换为和在AC'97控制器上固定48ks / s。此要求对于确保互操作性是必要的除了其他方面,AC'97控制器和WM9705之间可以保证基线的定义指定AC'97特征。SDATAOUT的复合流是MSB对齐(MSB优先),具有所有无效的时隙位AC'97控制器塞满了0。如果在指定的有效时隙内有少于20个有效位,则AC'97控制器总是将20位时隙的所有尾随无效位位置填充为0。例如,考虑一个正在播放到WM9705之一的8位采样流的DAC。前8位位置呈现给DAC(MSB对齐),接着是下一个12位位位置,由AC'97控制器填充0。这确保了无论如何实现的DAC(16,18或20位)的分辨率,将不会引入DC偏置最低有效位。当单声道音频采样流从AC'97控制器输出时,有必要左右样本流时隙用相同的数据填充。

SLOT 1:COMMAND ADDRESS PORT命令端口用于控制功能,并监视WM9705功能的状态包括但不限于混音器设置和电源管理控制接口架构支持多达64位,16位读/写寄存器,在偶数字节边界上可寻址。只有偶数寄存器(00h,02h等)有效,奇数不鼓励注册(01h,03h等)访问(如果支持,它们应默认为在偶数字节边界之前 - 即对01h的读取将返回00h的16位内容。该WM9705的控制寄存器文件仍然可读和可写,以提供更强大的功能可测试性。音频输出帧插槽1传送控制寄存器地址和读/写命令信息到WM9705。命令地址端口位分配位(19)读/写命令(1 =读,0 =写)位(18:12)控制寄存器索引(64位16位,偶数寻址)字节边界)位(11:0)保留(填充0)WM9705采样的第一位(MSB)指示当前控制事务是否为a读或写操作。以下7位位置传送目标控制寄存器地址。插槽内的尾随12位位置是保留的,必须用0填充AC'97控制器。

SLOT 2:命令数据端口命令数据端口用于在发生的情况下传送16位控制寄存器写数据当前命令端口操作是写周期。 (如插槽1,第19位所示)。位(19:4)控制寄存器写数据(如果当前操作为0,则填充0阅读)位(3:0)保留(填充0)如果当前命令端口操作是读取,则整个时隙必须填充0由AC'97控制器。插槽3和4:PCM播放左侧和右侧通道音频输出帧插槽3和4是立体声数字音频左右播放流。在一个典型游戏兼容PC此数据由标准PCM(.wav)输出样本组成数字混合(在AC'97控制器或主机处理器上)与音乐合成输出样本。如果传输的分辨率小于20位的样本流,AC'97控制器必须全部填充在此时隙内用0跟踪非有效位位置。SLOT 5:可选调制解调器线路编解码器不支持此数据槽。插槽6和9:LFE和CENTER通道数据这些插槽中的数据可以映射到音频DAC上,也可以作为SPDIF / I 2 S数据输出控制寄存器28h中的映射位DSA [1:0]和寄存器2Ah中的SPSA [1:0]。第7和第8位:环绕声道数据这些插槽中的数据可以映射到音频DAC上,也可以作为SPDIF / I 2 S数据输出控制寄存器28h中的映射位DSA和寄存器2Ah中的SPSA。10号和11号槽:这些插槽中的数据可以映射到音频DAC上,也可以作为SPDIF / I 2 S数据输出控制寄存器28h中的映射位DSA和寄存器2Ah中的SPSA。SLOT 12:GPIO不支持此插槽中的数据。