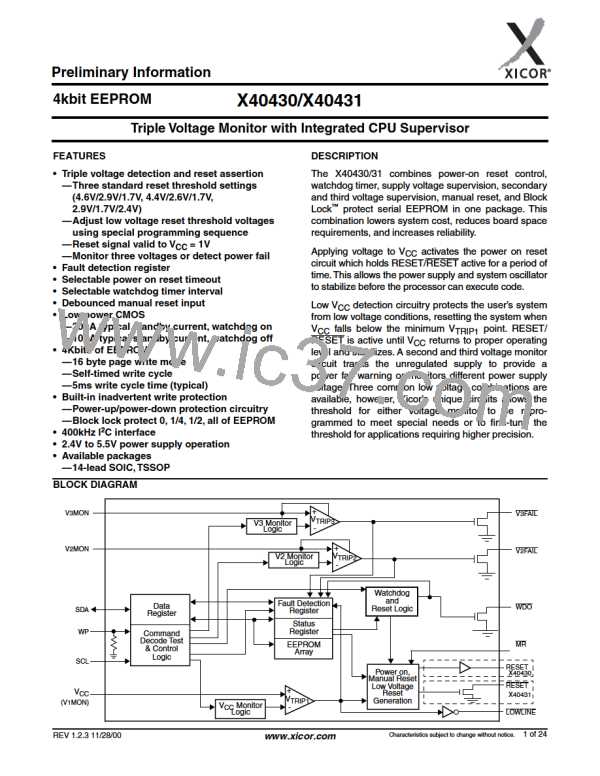

X40430/X40431 – Preliminary Information

A manual reset input provides debounce circuitry for

minimum reset component count.

The memory portion of the device is a CMOS Serial

EEPROM array with Xicor’s Block Lock protection. The

array is internally organized as x 8. The device features

a 2-wire interface and software protocol allowing opera-

tion on an I2C bus.

The Watchdog Timer provides an independent protec-

tion mechanism for microcontrollers. When the micro-

controller fails to restart a timer within a selectable time

out interval, the device activates the WDO signal. The

user selects the interval from three preset values. Once

selected, the interval does not change, even after

cycling the power.

The device utilizes Xicor’s proprietary Direct Write™

cell, providing a minimum endurance of 1,000,000

cycles and a minimum data retention of 100 years.

PIN CONFIGURATION

X40431

X40430

14-Pin SOIC, TSSOP

14-Pin SOIC, TSSOP

V

V2FAIL

V2MON

LOWLINE

NC

MR

RESET

V

V2FAIL

V2MON

1

2

3

4

14

13

12

11

1

2

3

4

14

13

12

11

CC

CC

WDO

V3FAIL

V3MON

WP

SCL

SDA

WDO

V3FAIL

V3MON

WP

SCL

SDA

LOWLINE

NC

MR

RESET

5

6

7

10

9

8

5

6

7

10

9

8

V

V

SS

SS

PIN DESCRIPTION

Pin

Name

Function

1

V2FAIL

V2 Voltage Fail Output. This open drain output goes LOW when V2MON is less than V

and

TRIP2

goes HIGH when V2MON exceeds V

. There is no power up reset delay circuitry on this pin.

TRIP2

2

V2MON

V2 Voltage Monitor Input. When the V2MON input is less than the V

voltage, V2FAIL goes

TRIP2

LOW. This input can monitor an unregulated power supply with an external resistor divider or can

monitor a second power supply with no external components. Connect V2MON to V or V

SS

CC

when not used.

3

LOWLINE Early Low V Detect. This CMOS output signal goes LOW when V

< V and goes high

TRIP1

CC

> V

CC

when V

.

CC

TRIP1

4

5

NC

MR

No connect.

Manual Reset Input. Pulling the MR pin LOW initiates a system reset. The RESET/RESET pin will

remain HIGH/LOW until the pin is released and for the t thereafter.

PURST

6

RESET/

RESET

RESET Output. (X40431) This open drain pin is an active LOW output which goes LOW whenever

falls below V voltage or if manual reset is asserted. This output stays active for the pro-

V

CC

TRIP

grammed time period (t

) on power up. It will also stay active until manual reset is released

PURST

and for t

thereafter.

PURST

RESET Output. (X40430) This pin is an active HIGH CMOS output which goes HIGH whenever

falls below V voltage or if manual reset is asserted. This output stays active for the pro-

V

CC

TRIP

grammed time period (t

and for t

) on power up. It will also stay active until manual reset is released

PURST

thereafter.

PURST

7

V

Ground

SS

Characteristics subject to change without notice. 2 of 24

REV 1.2.3 11/28/00

www.xicor.com

XICOR [ XICOR INC. ]

XICOR [ XICOR INC. ]