W134M/W134S直接Rambus时钟发生器

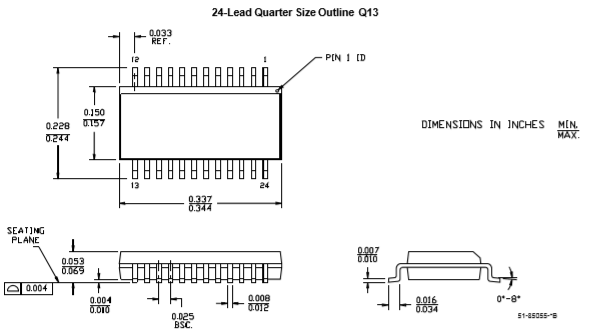

日期:2019-11-12特点:用于直接的RAMBUS存储器子系统的差分时钟源,用于高达800 MHz的数据传输速率。提供同步灵活性:RAMBUS®信道可以可选地与外部系统或处理器时钟同步。功率管理输出允许关闭RAMBUS信道时钟以最小化功耗。对于移动应用程序,Cypress CY2210、W133、W158、W159、W161和W167协同工作以支持英特尔体系结构平台,采用24针QSOP(150 mil SSOP)封装的低功耗CMOS设计

说明Cypress W134M/W134S为直接Rambus存储器子系统提供差分时钟信号。它包括使直接Rambus信道时钟与外部系统时钟同步的信号,但也可用于不需要同步Rambus时钟的系统。

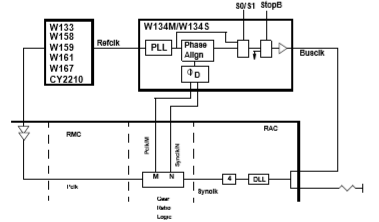

主要规格电源电压:VDD=3.3V±0.165V工作温度:……….0°C至+70°C输入阈值:1.5V典型的最大输入电压:…VDD+0.5V最大输入频率:…100 MHz输出占空比:40/60…最坏情况输出类型:…RAMBUS信令电平(RSL)DDLL系统结构和齿轮比逻辑分布式延迟锁定环(DDLL)系统架构,包括主系统时钟源、直接Rambus时钟发生器(DRCG)和包含Rambus访问单元(RAC)、Rambus存储器控制器(RMC)和传动比逻辑的核心逻辑。(此图抽象地将差分时钟表示为单总线时钟线。)DDLL的目的是在RMC/RAC边界处对核心逻辑和Rambus时钟(Pclk和Synclk)进行频率锁定和相位对齐,以便在不引起额外延迟的情况下允许数据传输。在DDLL体系结构中,PLL用于生成所需的Busclk频率,而分布式环路形成DLL以在RMC/RAC边界处对齐Pclk和Synclk的相位。主时钟源驱动系统时钟(Pclk)到核心逻辑,也驱动参考时钟(Refclk)到DRCG。对于典型的英特尔体系结构平台,Refclk将是CPU前端总线频率的一半。DRCG内的PLL与Refclk相乘以产生Busclk所需的频率,Busclk通过终端传输线(Rambus信道)驱动。在通道的中点,RAC使用自己的DLL感知Busclk进行时钟对齐,然后是生成Synclk的固定除以4。

Pclk是核心逻辑中的内存控制器(RMC)中使用的时钟,Synclk是RAC核心逻辑接口中使用的时钟。DDLL和齿轮比逻辑使用户能够直接从Pclk域到Synclk域交换数据,而不会产生额外的同步延迟。一般来说,Pclk和Synclk可以具有不同的频率,因此齿轮比逻辑必须选择适当的M和N分频器,以便Pclk/M和Synclk/N的频率相等。在一个有趣的例子中,Pclk=133mhz,Synclk=100mhz,M=4,而N=3,给出Pclk/M=Synclk/N=33mhz。带有齿轮比逻辑的时钟波形示例。齿轮比逻辑Pclk/M和Synclk/N的输出时钟从核心逻辑输出,并路由到DRCG相位检测器输入。Pclk/M和Synclk/N的路由必须在核心逻辑和板上匹配。在比较了Pclk/M和Synclk/N的相位后,DRCG相位检测器驱动相位校准器来调整DRCG输出时钟Busclk的相位。由于分布式环路中的其他所有东西都是固定延迟,因此调整Busclk调整Synclk的相位,从而调整Synclk/N的相位。这样,分布式环路调整Synclk/N的相位,以匹配Pclk/M的相位,从而消除DRCG相位检测器输入端的相位误差。当时钟对齐时,数据可以从Pclk域直接交换到Synclk域。最感兴趣的Pclk和Busclk频率的组合,按传动比组织。

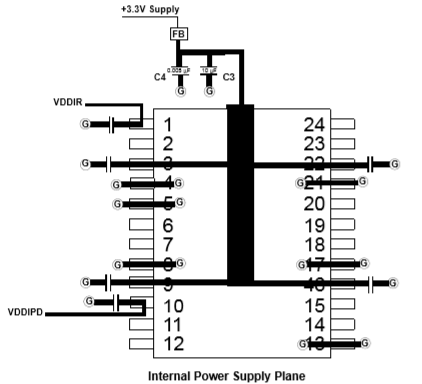

DDLL系统架构的更多细节,包括DRCG输出启用和旁路模式。相位检测器信号DRCG相位检测器从核心逻辑Pclk M(Pclk/M)和Synclk N(Synclk/N)接收两个输入。选择核心逻辑中的M和N分频器,使得PclkM和SynclkN的频率相同。相位检测器检测两个输入时钟之间的相位差,并通过分布式环路驱动DRCG相位校准器使输入相位误差为零。当环路被锁定时,PclkM和SynclkN之间的输入相位误差在状态转换部分给出的锁定时间之后,在设备特性表中给出的tERR,PD规范内。相位检测器将PclkM的上升沿与SynclkN的上升沿对齐。鉴相器输入时钟的占空比应在工作条件表中给出的DCIN,PD规范范围内。由于两个相位检测器输入时钟的占空比不一定相同,当上升沿对齐时,PclkM和SynclkN的下降沿可能不对齐。PclkM和SynclkN信号的电压电平由控制器确定。引脚VDDIPD用作鉴相器输入的电压参考,并应连接到控制器的输出电压电源。在某些应用中,DRCG PLL输出时钟将通过绕过相位校准器直接使用。如果不使用PclkM和SynclkN,则这些输入必须接地。用于选择PLL预分频器和反馈分配器以从输入Refclk确定PLL的倍率的逻辑。除法器A设置反馈,除法器B设置预分频器,因此PLL输出时钟频率由:PLLclk=Refclk*A/B设置。

表3显示了使用StopB输入信号启用时钟输出的逻辑。当StopB HIGH时,DRCG处于正常模式,Clk和ClkB是相位校准器输出(PAclk)之后的互补输出。当StopB低时,DRCG处于Clk停止模式,输出时钟驱动器被禁用(设置为Hi-Z),Clk和ClkB设置为直流电压VX,停止,如设备特性表所示。VX,STOP的电平由外部电阻网络设置。

表4显示了选择旁路和测试模式的逻辑。选择位S0和S1控制这些模式的选择。旁路模式产生全速PLL输出时钟,绕过相位校准器。测试模式将Refclk输入一直带到输出,绕过PLL和相位校准器。在输出测试模式(OE)中,Clk和ClkB输出都被置于高阻抗状态(Hi-Z)。这可以用于组件测试和板级测试。

频率和传动比几个支持的Pclk和Busclk频率、DRCG PLL中要求的相应A和B分频器以及传动比逻辑中相应的M和N分频器。列比给出定义为Pclk/Synclk的传动比(与M和N相同)F@PD列给出相位检测器处的分频(以MHz为单位),其中F@PD=Pclk/M=Synclk/N。状态转换时钟源有三个基本工作状态。图4显示了状态图,每个转换标记为A到H。注意,在状态转换期间,时钟源输出可能不是无故障的。设备通电后,设备可以进入任何状态,具体取决于控制信号、pwrdb和StopB的设置。在断电模式下,时钟源断电,控制信号pwrdb等于0。设备通电前,控制信号S0和S1必须稳定,并且只能在断电模式(pwrdb=0)下改变。参考输入,VDDR和VDDPD,在断电模式下可能保持接通或接地。

布局示例

包装图

Direct Rambus是Rambus Inc.的商标,Rambus是Rambus Inc.的注册商标。Intel是Intel Corporation的注册商标。