BiCMOS先进移相PWM控制器

日期:2019-11-14功能

可编程输出开启延迟

,自适应延迟集

,双向振荡同步

,电压模式或电流模式控制能力

,可编程软启动/软停止,通过单个引脚禁用芯片

,0%至100%占空比控制

,7MHz误差放大器

,运行至1MHz

,低有功电流消耗(500kHz时通常为5mA)

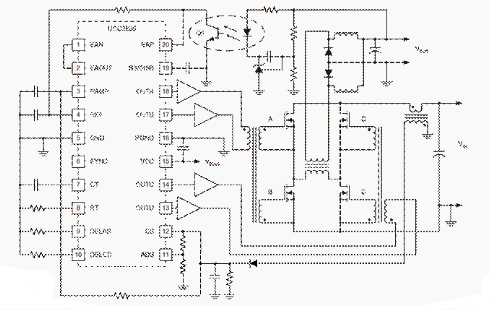

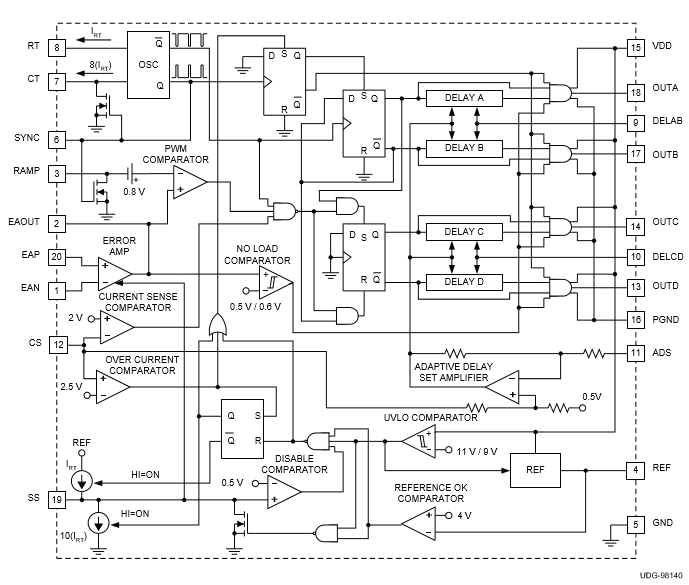

,欠压锁定期间的极低电流消耗(典型为150A)说明UCC3895是一种相移式脉宽调制控制器,通过相移一个半桥相对于另一个半桥的开关来实现对全桥功率级的控制。它允许恒定频率脉冲宽度调制与谐振零电压开关结合,在高频提供高效率。该部分既可用作电压模式控制器,也可用作电流模式控制器。

虽然UCC3895保持了UC3875/6/7/8系列和UC3879的功能,但它通过增强的控制逻辑、自适应延迟设置和关机功能等附加功能改进了该控制器系列。因为它是在BCDMOS中构建的,所以它的供电电流比双极性的同类产品要少得多。UCC38 95可以以1MHz的最大时钟频率工作。

UCC3895和UCC2895在20针SOIC(DW)封装、20针PDIP(N)封装、20针TSSOP(PW)封装和20针PLCC(Q)封装中提供。UCC1895提供20针CDIP(J)封装和20针CLCC封装(L)。

管脚说明

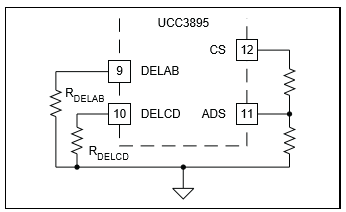

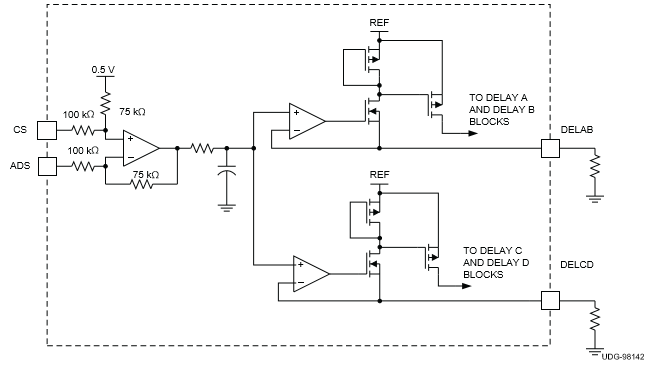

广告:自适应延迟集。此函数设置最大和最小编程输出延迟死区之间的比率。当ADS引脚直接连接到CS引脚时,不会发生延迟调制。最大延迟调制发生在ADS接地时。在这种情况下,当CS=0时,延迟时间是CS=2.0V(峰值电流阈值)时的4倍,ADS通过以下公式改变延迟管脚DELAB和DELCD上的输出电压:

VDEL=[0.75•(VCS-VADS)]+0.5V

其中VCS和VAD以伏特为单位。ADS必须限制在0V和2.5V之间,并且必须小于或等于CS。DELAB和DELCD也将被夹持至最小0.5V。

出口:误差放大器输出。它还内部连接到PWM比较器和空载比较器的非逆变输入。EAOUT内部固定在软启动电压。当EAOUT低于500mV时,空载比较器关闭输出级,当EAOUT高于600mV时,允许输出再次打开。

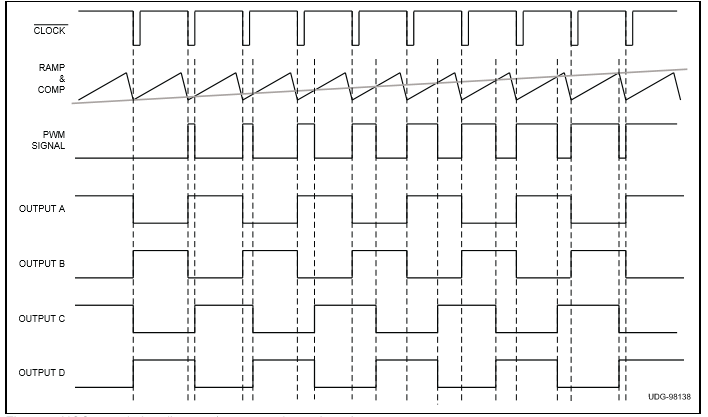

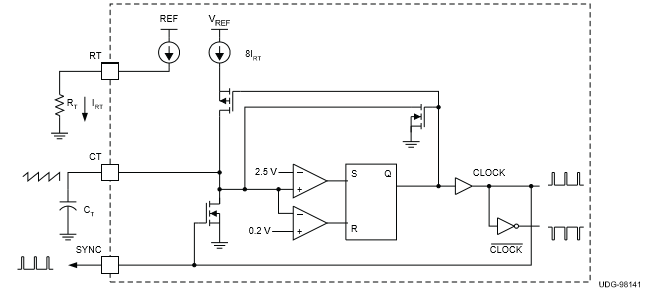

计算机断层扫描:振荡器定时电容器。(参考图1,振荡器框图)UCC3895的振荡器通过编程电流向CT充电。CT上的波形为锯齿形,峰值电压为2.35V,近似振荡器周期由以下公式计算:

5•RT•CT

tOSC公司=+120纳秒

其中,CT以法拉为单位,RT以欧姆为单位,tOSC以秒为单位。CT可以从100pF到880pF。请注意,大的CT和小的RT组合将导致CT波形的下降时间延长。增加的下降时间将增加同步脉冲宽度,从而限制OUTA、OUTB和OUTC、OUDD输出之间的最大相移,这限制了转换器的最大占空比。

反恐精英:现在的感觉。这是电流感应比较器的反向输入和过电流比较器的非反向输入,以及ADS放大器。电流检测信号用于峰值电流模式控制中的逐周电流限制,以及在所有具有输出关闭二级阈值的情况下的过电流保护。由过电流故障引发的输出禁用也会导致重启循环,称为

“软停止”,完全软启动。

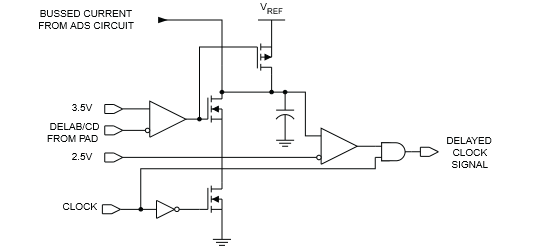

德莱布,德莱德:互补输出之间的延迟编程。DELAB编程在OUTA和OUTB切换之间的死区时间,DELCD编程在OUTC和OUTD之间的死区时间。这种延迟是在外部网桥的同一段中的互补输出之间引入的。UCC3895允许用户选择延迟,在该延迟中发生外部功率级的谐振切换。为两个半桥提供单独的延迟,以适应谐振电容充电电流的差异。每个阶段的延迟按以下公式设置:

(25 10•-12)•RDEL

t延迟=+25纳秒

VDEL,其中VDEL以伏特为单位,RDEL以欧姆为单位,tDELAY以秒为单位。DelAB和DelCD可以达到1Ma最大值。选择延迟电阻,使此最大值不超过。通过将DELAB和/或DELCD与REF连接,可消除可编程输出延迟。为了获得最佳性能,将这些管脚上的杂散电容保持在<10pF。

地面:除输出级外,所有电路的芯片接地。

出口A、出口B、出口C、出口D:这4个输出是100mA互补MOS驱动器,并优化驱动FET驱动电路。OUTA和OUTB是完全互补的(假设没有编程延迟)。它们工作在接近50%的占空比和一半的振荡频率。OUTA和OUTB用于驱动外部功率级中的半桥电路。OUTC和OUTD将驱动另一个半桥,并具有与OUTA和OUTB相同的特性。OUTC相对于OUTA相移,OUTD相对于OUTB相移。注意,改变OUTC和OUTD相对于OUTA和OUTB的相位关系,要求在这些瞬态期间,OUTC和OUTD的标称50%占空比除外。

PGND:第页输出级接地。为了保持关键模拟电路的输出开关噪声,UCC3895有两个不同的接地连接。PGND是高电流输出级的接地连接。GND和PGND必须在IC附近紧密地连接在一起。另外,由于PGND具有高电流,所以板迹必须是低阻抗的。

引脚说明(续)

斜坡:PWM比较器的反向输入。该引脚接收电压和平均电流模式控制下的CT波形,或峰值电流模式控制下的电流信号(加上斜率补偿)。内部放电晶体管设置在斜坡上,在振荡器死区期间触发。

室温:振荡器定时电阻器。(参考图1,振荡器框图)UCC3895中的振荡器通过用由RT编程的固定电流对外部定时电容CT充电来工作。RT电流计算如下:

3.0伏

式中,RT以欧姆为单位,IRT以安培为单位。RT可以从40kt到120kSoft启动充放电电流也由IRT编程。

SS/解散:软启动/禁用。这个管脚结合了两个独立的功能。

:芯片的快速关闭可通过以下任一方法完成:外部强制SS/DISB低于0.5V,外部强制REF低于4V,VDD下降到UNLO阈值以下,或检测到过电流故障(CS=2.5V)。

在REF被拉到4V以下或UVLO条件下,SS/DISB通过内部MOSFET开关被主动拉到地上。如果检测到过电流,

SS/DISB将吸收(10•IRT)电流,直到SS/DISB降至0.5V以下。

注意,如果SS/DISB被外部强制低于0.5V,引脚将开始产生等于IRT的源电流。还要注意,零件切换到低IDD电流模式的唯一时间是当零件处于欠压锁定状态时。

应用程序信息

故障或禁用条件通过后,VDD高于启动阈值,并且/或SS/DISB在软停止期间低于0.5V,SS/DISB将切换到软启动模式。管脚现在将产生电流,等于IRT。SS/DISB上用户选择的电容器确定软启动(和软启动)时间。此外,可以使用与电容器并联的电阻器,限制SS/DISB上的最大电压。注意,在软启动、软停止和禁用条件下,SS/DISB将主动将EAOUT引脚电压钳位到SS/DISB引脚电压。

同步:振荡器同步。该引脚是双向的。当用作输出时,SYNC可以用作时钟,这与芯片的内部时钟相同。当用作输入时,SYNC将覆盖芯片的内部振荡器并充当其时钟信号。此双向功能允许多个电源同步。同步信号还将对CT电容器和斜坡引脚上的任何滤波电容器进行内部放电。内部同步电路是电平敏感的,输入低阈值为1.9V,输入高阈值为2.1V。同步和GND之间可以连接一个小到3.9k的电阻,以减小同步脉冲宽度。

裁判:5V,1.2%参考电压。该基准向内部电路供电,也可向外部负载提供高达5毫安的电源。参考电压在欠压锁定期间关闭,但在所有其他禁用模式下都可以运行。为了获得最佳性能,旁路采用0.1F低ESR、低ESL电容对地。

申请信息(续)

自适应延迟集特性(ADS)允许用户在转换器的两个支路中的每个支路中改变开关命令之间的延迟时间。延迟时间调制通过将ADS(引脚11)连接到CS、GND或从CS到GND的电阻分压器来实现,以设置VAD。从上面的VDEL方程来看,如果ADS与GND绑定,那么VDEL与VCS成正比地增加,从而导致随着负载的增加tDELAY减少。在这种情况下,VDEL的最大值是2V。如果ADS连接到CS和GND之间的电阻分压器,则(VCS-VDS)变小,降低了VDEL的水平。这将减少延迟调制量。在与CS相连的ADS限制下,VDEL=0.5V,不发生延迟调制。在最大延迟调制(ADS=GND)的情况下,当电路从轻负载到重负载时,VDEL的变化是从0.5V到2V,这导致延迟时间随负载变化而变化4:1。

对自适应延迟进行编程的能力是一个理想的特性,因为最佳延迟时间是变压器一次绕组中电流的函数,并且可以随着电路负载的变化而改变10:1或更大的系数。参考文献[1]探讨了用于选择最有效功率转换的最佳延迟时间的许多相关因素,并说明了使用UC3879启用自适应延迟集的外部电路。在UCC3895控制器中简化了这种自适应特性的实现,使用户能够用最少的外部部件来调整延迟时间以适应特定的应用

电路描述

电路描述