AFE1124是HDSL/MDSL模拟前端

日期:2019-11-13特征

串行数字接口;28针SSOP;E1、T1和MDSL运行;64kbps至1168kbps运行;可缩放数据速率;250兆瓦功耗;完整的HDSL模拟接口;+5V电源(5V或3.3V数字)。

说明

通过提供所有主动模拟电路需要连接到一个数字信号处理器的所有模拟电路,大幅度降低了一个XDSL的尺寸和成本。外部妥协混合线变压器茶优化高位速率dsl而对于低速MDSL(“中速DSL”)和自适应速率dsl应用因为传输与接收滤波器响应自动变换时钟频率,AFE1124特别适用于RADSL和多速率DSL系统。从64kbps到1168kbps的一个宽范围的数据率操作装置。功能上,这个单元由一个发射机和一个隐形截面从2-bit数字符号数据的发送截面产生模拟信号并过滤该模拟信号模拟信号创建2B1Q符号板上微分线路驱动器提供13.5dbm信号到电话线隐形截面滤波器数字接收电话上的符号数据线此IC操作单元5V供应。该单元的数字电路可以连接到从3.3v到5v的一个供应方。该单元在一个28-PIN SSOP包装中。

操作理论

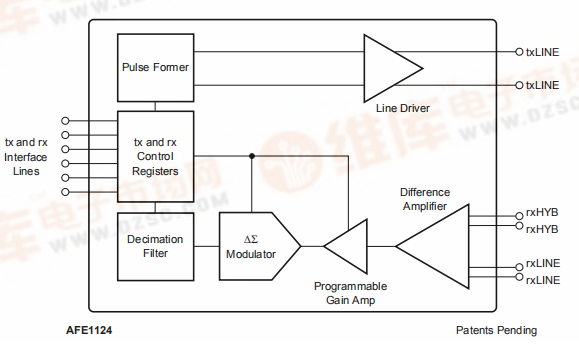

AFE1124由发射和接收信道组成。它通过一个六线串行接口、三线传输通道和三线接收通道与HDSL-DSP接口。它通过发送和接收模拟连接与HDSL电话线变压器和外部折衷混合接口。

传输通道由开关电容脉冲形成网络和差分线路驱动器组成。脉冲形成网络接收2位数字符号数据并产生滤波的2B1Q模拟输出波形。差分线路驱动器使用组合输出级,将B类操作(用于高效驱动大信号)与AB类操作(用于最小化交叉失真)相结合。

接收通道是围绕四阶delta-sigma a/D转换器设计的。它包括一个差分放大器,设计用于一阶模拟回波抵消的外部折衷混合。还包括增益为0dB至+12dB的可编程增益放大器。以24倍过采样率工作的δ-西格玛调制器以高达584kHz(1.168Mbps)的速率产生14位输出。

接收信道通过将两个差分输入相加来工作,一个来自线路(rxLINE),另一个来自折衷混合(rxHYB)。在标题为“AFE中的回声消除”的段落中描述了这两个输入的连接,以便从线信号中减去混合信号。差分放大器中每个输入的等效增益为1。然后,产生的信号传递到可编程增益放大器,该放大器可设置为0dB到+12dB的增益。在PGA之后,ADC将信号转换成14位数字字。

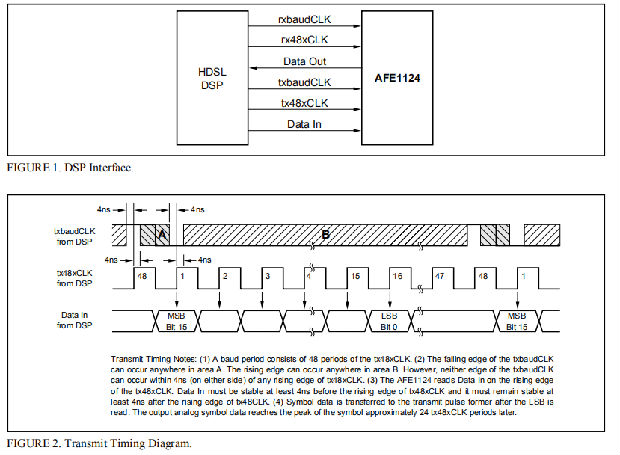

串行接口由三根传输线和三根接收线组成。三线传输接口为传输波特率时钟、传输48x过采样时钟和数据输出。三线接收接口为接收波特率时钟,接收48x过采样时钟和数据输入。发送和接收时钟由DSP提供给AFE1124,并且完全独立。

数字数据接口

数据由AFE1124在数据线上从DSP接收。数据从AFE1124传输到数据输出线上的DSP。以下段落描述了这些信号的定时和数据结构。

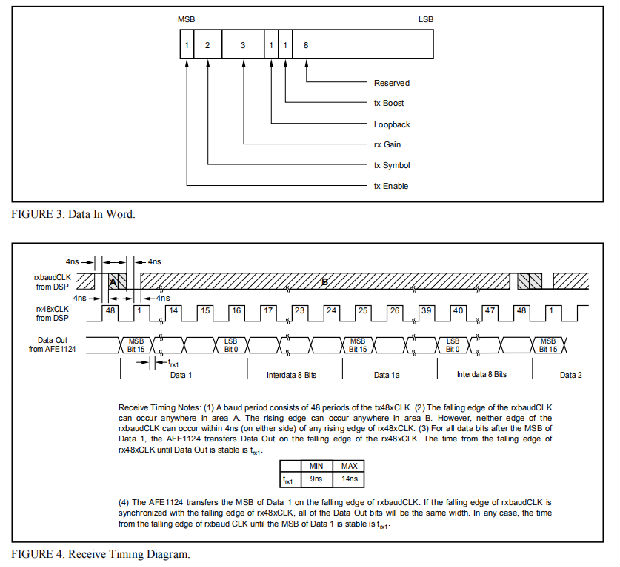

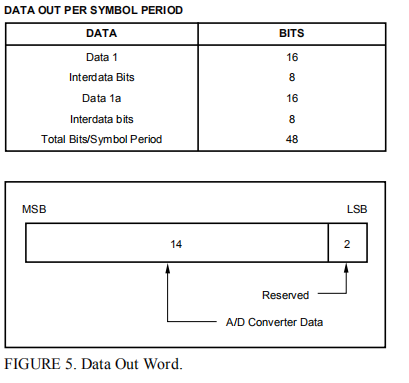

数据的发送和接收与48x发送和接收时钟(tx48xCLK和rx48xCLK)同步。每个波特率周期有48位时间。数据输入为在每个波特周期的前16位接收。其余32位周期不用于中的数据。数据输出在波特周期的前16位传输。第二个内插值在波特周期的后续比特中传输。

txbaudCLK公司:由数字信号处理器产生的传输数据波特率。T1为392kHz,E1为584kHz。它可能从32kHz(64kbps)到584kHz(1.168Mbps)不等。

tx48xCLK系列:由数字信号处理器产生的发射脉冲发生器过采样时钟。传输符号速率为48倍,584kHz符号速率为28.032MHz。这个钟应该连续运转。

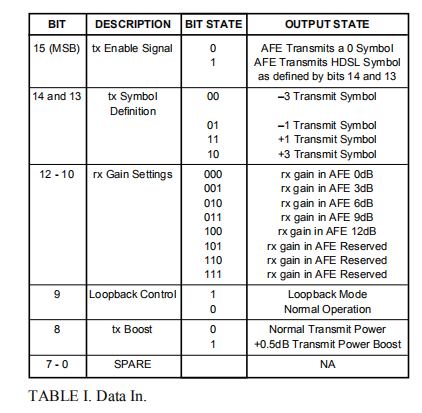

数据输入:这是从DSP发送到AFE的16位输出数据字。16位包括tx符号信息和其它控制位,如下所述。数据应在下降沿从数字信号处理器中计时,并在tx48xCLK上升沿有效。AFE1124在tx48xCLK的上升沿读取数据。位在表I中定义。数据在每个波特率周期的前16位期间由AFE1124读取。AFE1124中只使用前8位。第二个8位保留在将来的产品中使用。波特率周期的剩余32位周期不用于数据输入。

数据位:tx启用信号-该位控制tx符号定义位。如果该位为0,则不管tx符号定义位的状态如何,仅发送0符号。如果该位为1,则tx符号定义位确定输出符号。tx符号定义-这两个位决定发送的输出2B1Q符号。

接收增益设置-这些位设置接收通道可编程增益放大器的增益。

环回控制-该位控制环回操作。启用时(逻辑1),rxLINE+和rxLINE-输入与AFE断开。rxHYB+和rxHYB-输入保持连接。禁用时,连接rxLINE+和rxLINE–输入。

血栓素-该位控制输出线驱动器增加0.5dB的额外功率。

rxbaudCLK公司:这是由DSP生成的接收数据波特率(符号时钟)。T1为392kHz,E1为584kHz。它可以从32kHz(64kbps)到584kHz(1.168Mbps)不等。

rx48xCLK型:这是由数字信号处理器产生的采样时钟上的A/D转换器。接收符号速率为48倍,584kHz符号速率为28.032MHz。这个钟应该连续运转。

数据输出:这是从AFE发送到DSP的14位A/D转换器输出数据(+2个备用位)。A/D转换器的14位将是16位字(位15-2)的高位。备用位(1和0)将始终处于低位。接着是八个额外的(内部数据)位,它们总是很高。数据在rx48xCLK的下降沿上计时。A/D转换器抽取滤波器的带宽等于符号速率的一半。A/D转换器的标称输出速率为每符号周期一次转换。对于更灵活的后处理,在每个符号周期中存在第二内插A/D转换。在图4中,第一个转换显示为数据1,第二个转换显示为数据1a。建议将rxbaudCLK与rx48xCLK一起使用以读取数据1,而忽略数据1a。然而,任一或两个输出可用于更灵活的后处理。

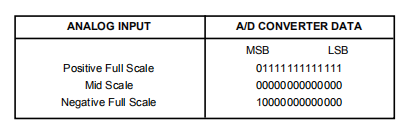

模数转换器数据

来自接收通道的A/D转换器数据以两个补码进行编码。

AFE中的回声消除

rxHYB输入从rxLINE输入中减去,用于一阶回波消除。为了正确操作,请确保rxLINE输入连接到变压器的同一极性信号(+到+和-到-),而rxHYB输入通过基本连接图中所示的折衷混合(–到+和+到-)连接到相反极性。

可缩放定时

AFE1124根据时钟频率缩放操作。所有的内部滤波器和脉冲发生器都随着时钟速度改变频率,这样只要改变时钟速度就可以在不同的频率下使用。

对于接收信道,delta-sigma转换器的数字滤波直接随时钟速度而缩放。转换器抽取滤波器的带宽总是符号速率的一半。在改变波特率时,唯一的接收通道问题是无源单极抗混叠滤波器(见下一节)。对于实现广泛速度范围的系统,应使用无源抗混叠滤波器的可选截止频率。

对于传输信道,脉冲形状和功率谱密度与时钟频率成正比。在变压器输出端测量曲线1所示的功率谱密度和曲线2所示的脉冲模板。输出端的变压器和RC电路为输出传输提供了一定的平滑度。在较低的比特率下,平滑的量将较小。

RXHYB和RXLINE输入抗混叠滤波器

如上面的基本连接图所示,混合输入和线路输入需要外部输入抗锯齿滤波器。对于RXLIN和RXHYB差分输入,输入抗混叠滤波器的3dB频率对于T1和E1符号速率应该是大约1MHz。两个输入电阻的滤波器建议值分别为750Ω和电容器的100 pF。两个750Ω电阻器和100pF电容器一起产生的3dB频率略高于1MHz。750Ω输入电阻将使AFE1124的输入阻抗的分压器损耗最小。

抗混叠滤波器将以3dB频率近似等于比特率获得最佳性能。例如,320kHz的3dB频率可用于每秒320k比特的单线比特率。

规范讨论

未消除回声

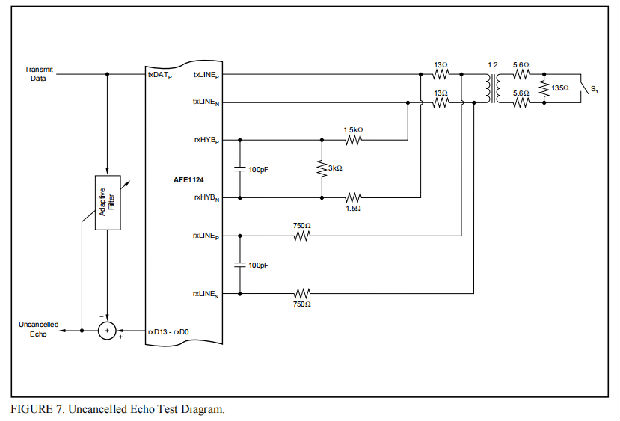

衡量收发机性能的一个关键指标是非抵消回波。未取消回声是AFE1124的发送和接收路径中所有错误的总和。它包括线性、失真和噪声的影响。未消除回声在生产中由Burr Brown进行测试,其电路类似于图7所示的未消除回声测试图。

未消除回波的测量如下。

AFE连接到一个输出电路,包括一个典型的1:2线路变压器。线路由135Ω电阻模拟。符号序列由测试仪生成并应用于AFE和自适应滤波器的输入。自适应滤波器的输出从AFE输出中减去,形成未消除的回波信号。一旦滤波器抽头收敛,将计算未取消回声的RMS值。由于不存在远端信号源或附加线噪声,因此未消除的回波仅包含在AFE1124的发射和接收部分中产生的噪声和线性误差。

未消除回波的数据表值是RMS未消除回波(指通过接收器增益输入的接收器)与标称传输信号(13.5dBm到135Ω或1.74Vrms)的比值。该回波值在多种条件下测量:启用环回(线路输入断开);在所有接收器增益范围内禁用环回;以及线路短路(图7中S1闭合)。

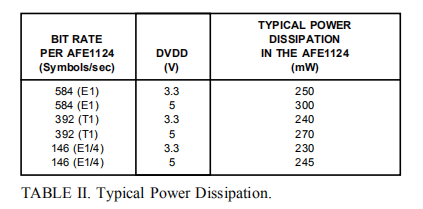

功耗

在AFE1124中功耗的大约80%在模拟电路中,并且这个分量不随时钟频率变化。然而,随着时钟频率的降低,数字电路中的功耗确实降低了。此外,当在较小的电源电压(如3.3V)下工作时,数字部分的功耗降低(模拟电源AVDD必须保持在4.75V到5.25V的范围内)。

规范章节中列出的功耗适用于以下正常工作条件:5V模拟电源;3.3V数字电源;传输到线路的标准13.5dBm;以及伪随机等概率HDSL输出脉冲序列。功率耗散规范包括AFE1124中耗散的所有功率,不包括外部负载中耗散的功率。外接电源为16.5dBm:13.5dBm对线路,13.5dBm对阻抗匹配电阻。16.5dBm的外负载功率为45mW。AFE1124在各种条件下的典型功耗如表二所示。

规范中的T1和E1功率测量使用图7所示的输出电路进行。这个电路使用1:2变压器。表2中所示的功率测量使用等效电阻负载代替变压器,以消除变压器的频率相关阻抗。

布局

HDSL系统的模拟前端有两个相互冲突的要求。它必须接收和传送中等高速率的数字信号,必须产生、驱动和转换精确的模拟信号。为了使用AFE1124达到最佳的系统性能,在电路板布局设计中,数字部分和模拟部分都必须仔细处理。

AFE1124数字部分的电源范围为3.3V到5V。该电源应与数字接地分离,并使用陶瓷0.1μF电容器,尽可能靠近DGND和DVD。一个电容器应放置在引脚3和4之间,第二个电容器应放置在引脚11和12之间。理想情况下,数字电源平面和数字接地平面都应连接到AFE1124的数字管脚(管脚5到10)上下。然而,DVDD可以由宽的印刷电路板(PCB)轨迹提供。强烈建议在所有数字管脚下安装一个数字接地平面。

AFE1124的其余部分应视为模拟。所有AGND引脚应直接连接到一个公共模拟接地平面,所有AVDD引脚应连接到一个模拟5V电源平面。这两个平面都应该有一个低阻抗的电源路径。模拟电源引脚应与模拟接地分离,陶瓷0.1μF电容器应尽可能靠近AFE1124。模拟电源和模拟接地之间的每个AFE1124还应使用一个10μF钽电容器。

理想情况下,所有接地平面和迹线以及所有电源平面和迹线应在连接在一起之前(如有必要)返回到电源连接器。每个接地和电源线对应相互布线,不应重叠另一线对的任何部分,线对之间的距离应至少为0.25英寸(6mm)。一个例外是数字和模拟接地平面应该通过一个小的轨迹连接在AFE1104下面。