FM18W08 256 Kbit(32 K x 8)宽电压字节宽度 F-RAM存储器

日期:2019-11-12特征

256 Kbit铁电随机存取存储器(F-RAM)逻辑组织为32k×8高耐久性100万亿(1014)读/写151年数据保留期(见数据保留和耐久表)NoDelay™写入先进的高可靠性铁电工艺与SRAM和EEPROM兼容工业标准32 K×8 SRAM和EEPROM引脚70 ns访问时间,130 ns周期时间优于电池支持的SRAM模块无电池问题单片可靠性真正的表面贴装解决方案,无返工步骤适用于潮湿、冲击和振动抗负电压过冲低功耗有功电流12毫安(最大值)备用电流20μA(典型值)宽电压运行:VDD=2.7 V至5.5 V工业温度:–40℃至+85℃??28针小外形集成电路(SOIC)封装符合有害物质限制(RoHS)

功能描述

FM18W08是一个32 K×8的非易失性存储器,它可以读取和写入类似于标准SRAM。铁电随机数存取存储器或F-RAM是非易失性的,这意味着数据在断电后保留。它为151年来,在消除可靠性问题的同时,功能缺陷和系统设计复杂性电池支持的SRAM(BBRAM)。快速写入计时和高写持久性使F-RAM优于其他类型的记忆。FM18W08操作与其他RAM设备类似因此,它可以作为系统中的标准SRAM。最小读写循环时间是平等的。由于F-RAM存储器的独特性,它是非易失性的铁电存储器过程。这些特性使FM18W08非常适合需要频繁或快速的书写。该设备提供28针SOIC表面安装封装。设备规格在工业上得到保证温度范围-40°C至+85°C。

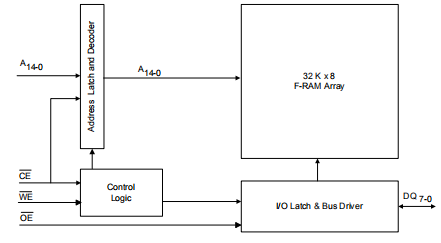

设备操作 :FM18W08是一个字节范围的F-RAM存储器,逻辑上是有组织的as 32768×8并使用工业标准并行访问接口。写入部件的所有数据立即不易失毫不迟疑。F-RAM存储器的功能操作是与SRAM型设备相同,但FM18W08要求开始每个存储周期的CE下降沿。见功能真值表,第13页,完整描述读写模式。存储器结构用户访问32768个内存位置,每个位置有8个数据位通过一个并行接口。完整的15位地址唯一指定8192字节中的每个字节。F-RAM阵列是组织为4092行,每行8字节。此行分段对操作没有影响,但是用户可以将数据分组到块体的耐久性特征,如耐力部分。读写存储器的周期时间相同操作。这简化了内存控制器逻辑和定时电路。同样,读写的访问时间是相同的内存操作。当CE被解除高压时,预充电操作开始,并且是每个内存周期所必需的。因此与SRAM不同,访问和循环时间并不相等。写入在访问结束时立即发生,没有延迟。不像一个EEPROM,不需要轮询设备是否准备好自写入以总线速度发生以来的状态。用户有责任确保VDD保持在防止错误操作的数据表公差。也很合适VDD和CE之间的电压电平和时序关系必须在通电和断电事件期间进行维护。见第12页的“动力循环计时”。

存储器操作FM18W08的设计方式与其他字节存储器产品。对于熟悉的用户BBSRAM,性能相当,但是字节范围接口的操作方式稍有不同,如前所述下面。对于熟悉EEPROM的用户来说,不同之处在于从F-RAM技术更高的写性能包括NoDelay写作和更高的写作耐力。读取操作读取操作从CE的下降沿开始。在这个时候,地址位被锁存并启动一个存储器周期。一旦启动,必须在内部完成完整的内存周期即使CE失效。数据在总线上可用达到访问时间后。地址被锁定后,地址值可以是在满足保持时间参数时更改。不像SRAM,更改地址值对地址锁定后的内存操作。当OE被断言为低时,FM18W08将驱动数据总线并且满足内存访问时间。如果在满足内存访问时间,数据总线将为driv数据。如果在完成内存访问之前断言了OE,在有效数据可用之前,不会驱动数据总线。这个该特性通过消除由驱动到总线的无效数据引起的瞬变。什么时候?OE被解除高配置,数据总线将保持在HI-Z状态。

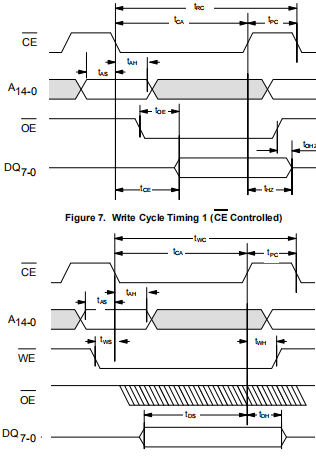

写操作在FM18W08中,写入与读取的间隔相同。这个FM18W08同时支持CE和WE控制的写入周期。在两种情况下,地址都锁定在CE的下降沿上。在CE控制的写操作中,WE信号在开始内存循环。也就是说,当设备在芯片启用时被激活。在这种情况下,设备以写入方式开始内存循环。FM18W08不能驱动数据总线与运行经验的状态无关。在我们控制的写入中,内存周期从CE的边缘。WE信号在CE下降边缘后下降。因此,存储周期以读取开始。数据总线将根据运行经验驾驶,直到我们摔倒。行政长官和我们控制的写入计时情况如第12页所示。对数组的写访问在启动内存循环。写入访问在我们或CE的上升沿,以先到者为准。有效的笔迹操作要求用户满足访问时间规范在我们或行政长官离开之前。数据设置时间指示在写访问。

与其他非易失性存储器技术不同,它没有写操作F-RAM延迟。因为底层内存相同,用户体验不到在公共汽车上耽搁。整个内存操作发生在单总线循环。因此,任何操作包括读或写可以在写入之后立即发生。数据轮询,a与eeprom一起用来确定写操作是否完整,是不必要的。预充电操作预充电操作是一种内部条件,其中内存状态已准备好进行新的访问。所有内存周期包括内存访问和预充电。预充电是用户通过驱动CE信号高启动。它必须留下至少在最短预充电时间内为高,tPC。用户确定此操作的开始,因为在CE升高之前,不会开始预充电。但是,设备有必须满足的最大CE低时间规范。耐力在内部,F-RAM通过读取和恢复操作机制。因此,每个读写周期都包含国家变更。内存结构基于一个数组行和列的。每次读或写访问都会导致一整排的耐力循环。在FM18W08中,一行是64有点宽。每8字节的边界标志着一个新的划船。通过频繁地确保访问的数据位于不同的行中。无论如何,F-RAM提供比其他非易失性更高的写持久性回忆。1014个循环的额定耐久极限将允许20多年来,每秒有150000次访问同一行。

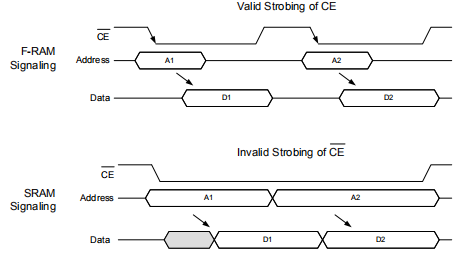

F-RAM设计注意事项在首次使用F-RAM进行设计时,SRAM的用户将认识到一些细微的差别。首先,字节范围的F-RAM存储器锁存在芯片使能的下降沿上的每个地址。这允许地址总线在启动内存后更改进入。因为每次访问都会锁定在CE的边缘,用户不能像用它一样接地SRAM公司。修改现有设计使用F RAM的用户应该检查内存控制器的计时兼容性地址和控制管脚。每个内存访问必须合格,CE含量低。在很多情况下,这是只需要更改。信号关系的一个例子是如下图所示。还显示了一个常见的SRAM信号不适用于FM18W08的关系。CE为每个地址选通的原因有两个:它锁存新地址并创建必要的预收费期当CE高的时候。

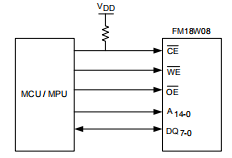

第二个设计考虑因素是操作。电池供电的sram被迫监视VDD以便切换到备用电池。它们通常会阻止用户访问低于某一VDD级别,以防止加载有源SRAM的电流需求电池。用户可以突然中断对非易失性存储器的访问没有警告或指示的断电情况。F-RAM存储器不需要这个系统开销。这个内存不会阻止符合以下条件的任何VDD级别的访问指定的工作范围。用户应采取措施当VDD为太过分了。举行一个关机期间处理器处于重置状态可能就足够了。它是建议将芯片启用拉高并允许在通电和断电循环期间跟踪VDD。它是用户有责任确保芯片使能防止低于VDD最小值(2.7 V)的访问。图显示了CE上的一个上拉电阻器,它将保持引脚高功率循环期间,假设MCU/MPU引脚在复位条件下三态。上拉电阻值应选择确保CE管脚轨迹VDD高足够大的值,因此当CE低时所消耗的电流一个问题。

请注意,如果CE与地面相连,用户必须确保我们没有在上电或断电事件中处于低位。如果芯片已启用而且我们在能量循环期间很低,数据会被破坏。图显示了WE上的一个上拉电阻器,它将保持pin高功率循环期间,假设MCU/MPU引脚在复位条件下三态。上拉电阻值应选择以确保我们将磁道VDD锁定到高足够大的值,所以当我们很低的时候所消耗的电流一个问题。