ADF4108是锁相式频率合成器

日期:2019-11-14特征

8.0 GHz带宽;3.2 V至3.6 V电源;单独的充油泵电源(VP)允许长时间调谐;3.3V系统中的电压;可编程双模预分频器;8/9、16/17、32/33或64/65;可编程电荷泵电流;可编程反间隙脉冲宽度;三线串行接口;模拟和数字锁检测;软硬件断电模式;用adispll设计环路滤波器;4 mm×4 mm,20铅屑秤包装。

应用

宽带无线接入;卫星系统;仪表;无线区域网路;无线电台基站。

一般说明

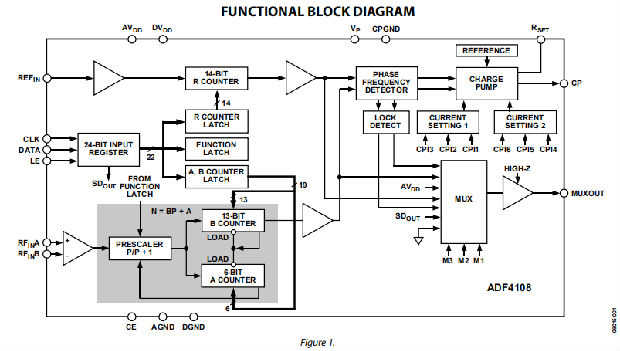

ADF4108频率合成器可用于实现上转换和下转换部分的本地振荡器无线接收器和发射器。它由低噪音组成数字鉴频器,精密电荷泵可编程参考分压器,可编程A和B计数器,以及一个双模预分频器(P/P+1)。A(6位)和B(13位)计数器,与双模预分频器一起使用(P/P+1),实现N除法器(N=BP+A)。此外,14位参考计数器(R计数器)允许选择重新输入PFD输入处的频率。一个完整的锁相环(PLL)如果合成器与外部环路滤波器和压控振荡器(VCO)。非常高带宽意味着倍频器可以在许多高频系统,简化了系统架构降低成本。

规格

AVDD=DVDD=3.3v±2%,AVDD≤VP≤5.5v,AGND=dgd=CPGND=0v,RSET=5.1kΩ,dBm为50Ω,TA=TMIN为TMAX,除非另有说明。

1、工作温度范围(B型)为-40°C至+85°C。

2、B芯片规格作为典型值给出。

3、这是CMOS计数器的最大工作频率。应选择预分频器值,以确保射频输入被分成小于该值的频率。

4、AVDD=DVDD=3.3伏。

5、交流耦合确保AVDD/2偏置。

6、由设计保证。样品测试以确保符合性。

定时特性

AV=DV=3.3v±2%,AV≤V≤5.5v,AGND=DGND=CPGND=0v,R=5.1kΩ,dBm为50Ω,T=T~T,除非另有说明。

1、由设计保证,但未经生产测试。

2、工作温度范围(B型)为-40°C至+85°C。

操作理论

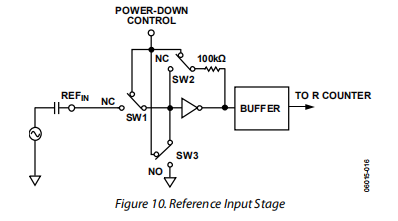

参考输入级

参考输入阶段如图10所示。SW1和SW2是常闭开关。SW3常开。当启动断电时,SW3关闭,SW1和SW2打开。这可确保断电时不会加载参考销。

射频输入级

射频输入级如图11所示。然后是一个两级限幅放大器,以产生预分频器所需的CML时钟电平。

预分频器(P/P+1)

双模预分频器(P/P+1)与A和B计数器一起,实现了大除法比N(N=BP+A)。在CML级工作的双模预分频器从RF输入级接收时钟,并将其划分为CMOS a和B计数器的可管理频率。预分频器是可编程的。它可以在软件中设置为8/9、16/17、32/33或64/65。它基于同步4/5核。对于连续的输出频率,最小分频比是可能的。该最小值由预分频器值P确定,并由(P-P)给出。

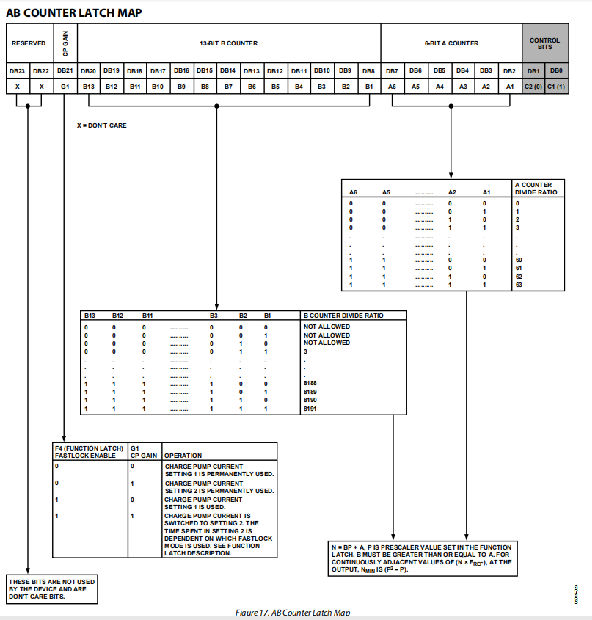

A和B计数器

A和B CMOS计数器与双模预分频器结合,在PLL反馈计数器中允许宽范围的分频比。计数器被指定在预分频器输出小于或等于300兆赫时工作。因此,在RF输入频率为4.0ghz的情况下,16/17的预分频器值是有效的,但8/9的值是无效的。

脉冲吞咽功能

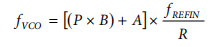

A和B计数器与双模预分频器一起,使得能够产生仅由参考频率除以R隔开的输出频率。VCO频率的方程式如下:

其中:fVCO是外部电压控制的输出频率振荡器(VCO);P是双模预分频器的预设模数(8/9、16/17,等等);B是二进制13位计数器(3到8191)的预设除法比;A是二进制6位燕子计数器的预设除法比(0到63);fREFIN是外部参考频率振荡器。

R计数器

14位R计数器允许将输入参考频率向下分割,以产生相位频率检测器(PFD)的参考时钟。允许1到16383的分割比。

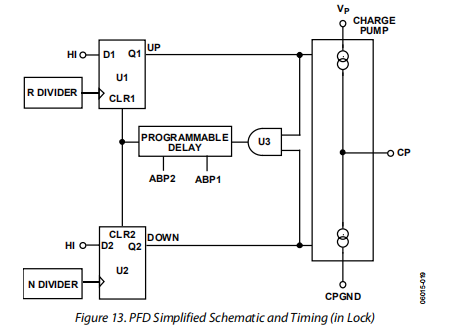

相频探测器和电荷泵

相位频率检测器(PFD)从R计数器和N计数器(N=BP+A)接收输入,并产生与它们之间的相位和频率差成比例的输出。图13是一个简化的示意图。PFD包括可编程延迟元件,用于控制反间隙脉冲的宽度。该脉冲确保PFD传递函数中没有死区,并将相位噪声和参考杂散降至最低。参考计数器锁存器中的两个位ABP2和ABP1控制脉冲的宽度(见图16)。不建议使用最小反间隙脉冲宽度。

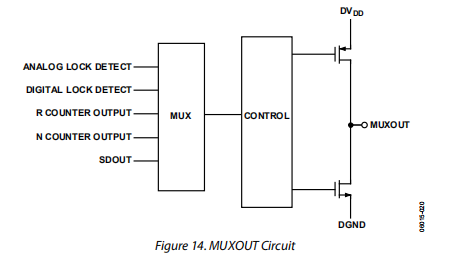

多路输出和锁定检测

ADF4108上的输出多路复用器允许用户访问芯片上的各种内部点。MUXOUT的状态由函数锁存器中的M3、M2和M1控制。图18显示了完整的真值表。图14以框图形式显示了MUXOUT部分。

锁定检测

MUXOUT可编程用于两种锁检测:数字锁检测和模拟锁检测。

数字锁检测处于高激活状态。当R计数器锁存器中的锁检测精度(LDP)位设置为0时,当连续三个相位检测器(PD)周期的相位误差小于15ns时,数字锁检测设置为高。当LDP设置为1时,需要5个小于15ns的连续周期来设置锁检测。在随后的任何PD循环中检测到大于25 ns的相位误差之前,它一直保持高值。

N通道开漏模拟锁检测应使用标称值为10 kΩ的外部上拉电阻器进行操作。当检测到锁止时,该输出是高的,带有窄的、低的脉冲。

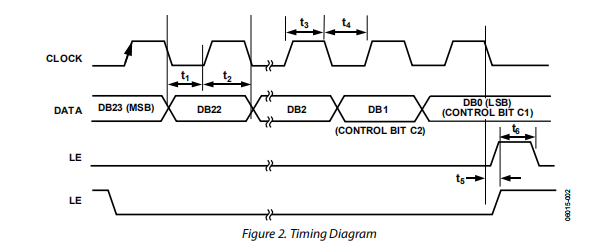

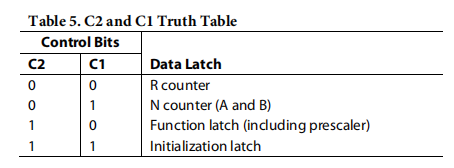

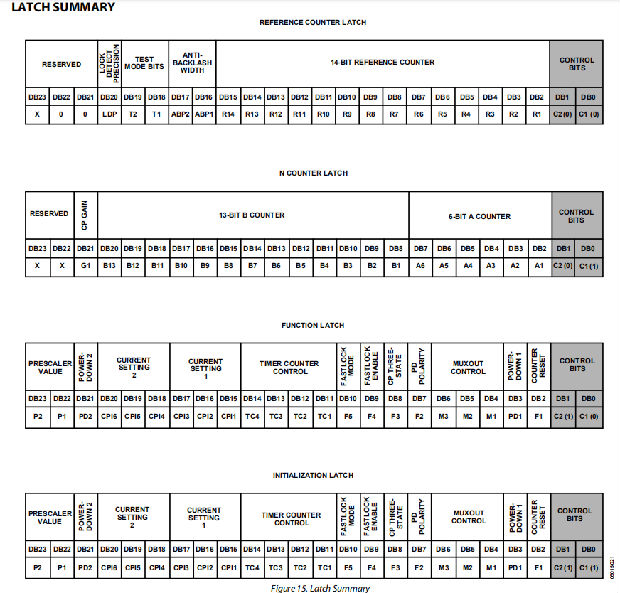

输入移位寄存器

ADF4108数字部分包括24位输入移位寄存器、14位R计数器和19位N计数器,包括6位a计数器和13位B计数器。数据被记录到CLK每个上升沿上的24位移位寄存器中。数据首先在MSB中计时数据从移位寄存器传输到LE上升沿上的四个锁存器之一。目标锁存由移位寄存器中两个控制位(C2,C1)的状态决定。这是2个lsb、DB1和DB0,如图2的时序图所示。这些位的真值表如表5所示。

图15显示了锁存器是如何编程的概要。

功能闩锁

片上功能锁存器编程时,C2和C1分别设置为1和0。图18显示了用于编程函数锁存器的输入数据格式。

计数器复位

DB2(F1)是计数器重置位。当该位为1时,R计数器和AB计数器复位。对于正常操作,该位应为0。通电后,需要禁用F1位(设置为0)。然后,N计数器继续与R计数器紧密对齐计数。(最大误差是一个预分频器周期。)

断电

DB3(PD1)和DB21(PD2)提供可编程的断电模式。它们由CE pin启用。

当CE引脚低时,无论PD2和PD1的状态如何,设备都会立即被禁用。

在编程异步关机中,设备在将1锁定到PD1位后立即关机,条件是PD2已加载0。

在程控同步掉电中,电荷泵对器件的掉电进行门控,以防止不必要的跳频。一旦通过将1写入PD1来启用断电(在1也已加载到PD2的情况下),设备在下一个电荷泵事件发生时进入断电状态。

当启动断电(同步或异步模式,包括CE引脚启动断电)时,会发生以下事件:

(1)、移除所有有效直流电流路径。

(2)、R、N和超时计数器被强制设置为其加载状态条件。

(3)、充油泵被强制进入三态模式。

(4)、数字锁检测电路复位。

(5)、RFIN输入被借记。

(6)、参考输入缓冲电路被禁用。

(7)、输入寄存器保持激活状态,并能够加载和锁定数据。

多路输出控制

片上多路复用器由ADF4108上的M3、M2和M1控制。

快锁启用位

函数锁存器的DB9是fastlock启用位。仅当此位为1时才启用快速锁定。

快锁模式位

功能锁存器的DB10是快锁模式位。启用fastlock时,该位决定使用哪种fastlock模式。如果fastlock mode位为0,则选择fastlock mode 1;如果fastlock mode位为1,则选择fastlock mode 2。

快速锁定模式1

充电泵电流切换到电流设置2的内容。设备通过将1写入AB计数器锁存器中的CP增益位进入fastlock。该装置通过在AB计数器锁存器中写入0的CP增益位而退出FASTLIKE。

快速锁定模式2

充电泵电流切换到电流设置2的内容。

设备通过将1写入AB计数器锁存器中的CP增益位进入fastlock。该装置在定时器计数器的控制下退出FASTROCK。在由TC4:TC1中的值确定的超时时间之后,AB计数器锁存器中的CP增益位自动重置为0,并且设备恢复为正常模式而不是fastlock。超时时间如图18所示。

定时器计数器控制

用户可以选择编程两个电荷泵电流。其目的是当射频输出稳定且系统处于静态时使用电流设置1。当系统是动态的并且处于变化状态(即,当新的输出频率被编程时)时,使用电流设置2。

正常的事件顺序如下:

用户首先决定首选的电荷泵电流是多少。例如,选择2.5毫安作为电流设置1,5毫安作为电流设置2。

同时,在恢复到一次电流之前,必须确定二次电流保持激活的时间。这由功能锁存器中的定时器计数器控制位DB14:DB11(TC4:TC1)控制。真值表如图18所示。

现在,要编程一个新的输出频率,用户只需使用新的a和B值编程AB计数器锁存器。同时,CP增益位可以设置为1,这将在TC4:TC1确定的一段时间内使用CPI6:CPI4中的值设置电荷泵。当此时间结束时,电荷泵电流恢复为CPI3:CPI1设置的值。同时,AB计数器锁存器中的CP增益位被重置为0,并且现在准备好下次用户希望改变频率。注意,定时器计数器上有一个启用功能。当通过将功能锁存器中的Fastlock Mode位(DB10)设置为1来选择Fastlock Mode 2时,它被启用。

电荷泵电流

CPI3、CPI2和CPI1为电荷泵编程电流设置1。CPI6、CPI5和CPI4为电荷泵编程电流设置2。

预分频器值

功能锁存器中的P2和P1设置预分频器值。应选择预分频器值,使预分频器输出频率始终小于或等于300 MHz。因此,在RF频率为4ghz的情况下,16/17的预分频器值是有效的,但8/9的值是无效的。

局部放电极性

该位设置相位检测器极性位。

CP三态

该位控制CP输出引脚。当位设置为高时,CP输出将进入三种状态。当位设置为低时,CP输出被启用。

初始化闩锁

当C2和C1设置为1和1时,初始化锁存器编程。这与功能锁存器基本相同(当C2,C1=1,0时编程)。

然而,当初始化锁存被编程时,额外的内部复位脉冲被应用到R和AB计数器。当AB计数器数据被锁定时,该脉冲确保AB计数器处于加载点,并且设备将开始以近相位对齐方式计数。

如果锁存器编程为同步断电(CE引脚高;PD1位高;PD2位低),内部脉冲也会触发此断电。预分频器基准和振荡器输入缓冲器不受内部复位脉冲的影响,因此在计数恢复时保持紧密的相位对准。

当初始化后第一个AB计数器数据被锁定时,内部复位脉冲再次被激活。然而,此后连续的AB计数器加载不会触发内部复位脉冲。

初次通电后的设备编程在最初给设备通电之后,有三种方法可以对设备进行编程。

1、应用VDD。

2、编程初始化锁存器(输入字的11/2 LSB)。确保F1位编程为0。

3、接下来,执行一个功能锁存加载(控制字的10/2 lsb),确保F1位编程为0。

4、然后进行R加载(00/2 LSB)。

5、然后进行AB加载(1/2 LSB)。

加载初始化闩锁时,将发生以下情况:

1、加载功能闩锁内容。

2、内部脉冲将R、AB和超时计数器重置为负载状态条件,并将电荷泵重置为三种状态。注意,预分频器带隙基准和振荡器输入缓冲器不受内部复位脉冲的影响,允许在计数恢复时进行近相位对准。

3、初始化字激活相同的内部复位脉冲后锁定第一个AB计数器数据。连续AB加载不会触发内部复位脉冲,除非有另一个初始化。

CE-Pin法

1、应用VDD。

2、将CE调低以使设备断电。这是一种异步断电,因为它会立即发生。

3、对功能锁存器(10)进行编程。

4、对R计数器闩锁(00)进行编程。

5、编程AB计数器闩锁(01)。

6、将CE调高,使设备断电。R和AB计数器现在将以紧密对齐的方式恢复计数。

注意,在CE变高之后,可能需要1μs的持续时间,以使预分频器带隙电压和振荡器输入缓冲偏置达到稳定状态。

CE可用于上下驱动设备以检查通道活动。只要输入寄存器在最初应用V之后至少编程一次,则无需每次禁用和启用设备时对其重新编程。尽职调查

计数器复位方法

1、应用VDD。

2、执行功能闩锁加载(10英寸2 LSB)。作为此操作的一部分,将1加载到F1位。这将启用计数器重置。

3、进行R反向加载(00/2 LSB)。

4、进行AB反向加载(1/2 LSB)。

5、执行功能闩锁加载(10英寸2 LSB)。作为此操作的一部分,将0加载到F1位。这将禁用计数器重置。此序列提供与初始化方法相同的紧密对齐。它提供对内部重置的直接控制。请注意,计数器复位将计数器保持在负载点,并使电荷泵处于三种状态,但不会触发同步断电。

电源注意事项

ADF4108在3.2 V到3.6 V的电源范围内工作。ADP3300ART-3.3是来自模拟设备公司的一个低损耗线性调节器。它输出3.3 V,精度为1.4%,建议与ADF4108一起使用。

接口

ADF4108具有一个简单的SPI兼容串行接口,用于向设备写入数据。CLK、DATA和LE控制数据传输。当LE(锁存启用)变高时,已在CLK的每个上升沿上进入输入寄存器的24位被传输到适当的锁存。时序图见图2,锁存真值表见表5。

最大允许串行时钟速率为20 MHz。这意味着该设备的最大更新速率为833 kHz或每1.2秒更新一次。这对于在几百微秒内具有典型锁定时间的系统来说肯定是绰绰有余的。

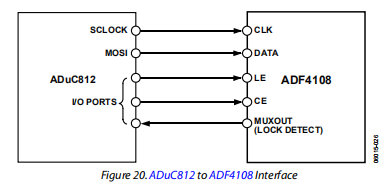

ADUC812接口

图20显示了ADF4108和ADuC812 MicroConverter®之间的接口。由于ADuC812基于8051内核,因此该接口可与任何基于8051的微控制器一起使用。MicroConverter设置为SPI主模式,CPHA=0。要启动操作,I/O端口驱动LE将变低。ADF4108的每个锁存需要一个24位字。这是通过将三个8位字节从微转换器写入设备来实现的。当第三个字节被写入时,应该将LE输入调高以完成传输。

在第一次向ADF4108通电时,需要四次写入(初始化锁存器、功能锁存器、R计数器锁存器和N计数器锁存器各一次)才能使输出变为活动。

ADuC812上的I/O端口线也用于控制断电(CE输入)和检测锁(MUXOUT配置为锁检测并由端口输入轮询)。

当在所描述的模式下工作时,ADuC812的最大突发速率为4 MHz。这意味着输出频率可以改变的最大速率是166 kHz。

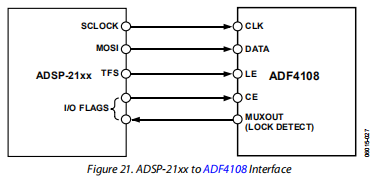

ADSP-21xx接口

图21显示了ADF4108和ADSP-21xx数字信号处理器之间的接口。ADF4108需要一个24位串行字用于每次闩锁写入。使用ADSP-21xx系列实现这一点的最简单方法是使用具有备用帧的自动缓冲传输操作模式。这提供了一种在生成中断之前传输整个串行数据块的方法。为8位设置字长,并为每个24位字使用三个内存位置。要对每个24位锁存器进行编程,存储三个8位字节,启用自动缓冲模式,然后写入DSP的发送寄存器。最后一个操作启动自动缓冲传输。

芯片级封装电路板设计指南

芯片级封装(CP-20-6)上的焊环是矩形的。印刷电路板衬垫的长度应比包装带长度长0.1 mm,宽度应比包装带宽度宽0.05 mm。土地应该在地垫上居中。这确保焊点尺寸最大化。芯片秤封装的底部有一个中央热垫。

印刷电路板上的热敏垫应至少与该外露垫一样大。在印刷电路板上,热衬垫和衬垫图案的内边缘之间至少应有0.25 mm的间隙。这样可以避免短路。

热过孔可用于印制电路板热垫上,以提高封装的热性能。如果使用过孔,则应将其并入1.2 mm间距网格处的热垫中。通孔直径应在0.3 mm和0.33 mm之间,通孔筒应镀1盎司铜以插入通孔。用户应将印刷电路板热垫连接到AGND。